Устройство для деления чисел

Иллюстрации

Показать всеРеферат

Устройство относится к вычислительной технике и позволит делить два числа с исправлением одиночных ошибок. Цель изобретения - повышение надежности. Устройство Содержит регистры делителя и делимого, принимающие делитель А и делимое В, блок деления, определяющие деления без восстановления остатка частное С и остаток или R-B при R О, узлы свертки, формирующие контрольные коды по модулю три -mod3, , , элемент НЕ, элементы И, сумматор по модулю три, формирующие контрольный код mod3 и kB kA-kC+k-RJmodS, узел, сравнивающий коды kB и kB и, в случае несовпадения, блокирующий прием новых операндов в регистры, а также записывающий единичный сигнал в триггер. В следующем такте под действием этого сигнала на группах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ инвертируются коды делимого, частного и остатка, а также сигналы на входах и выходах блока деления, что позволяет маскировать одиночную ошибку и таким образом получить правильный результат. 2 ил. ё

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 6 06 F 7/52, 11/08

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4701098/24 (22) 06.06.89 (46) 07.02.92, Бюл. М 5 (71) Одесский политехнический институт (72) А.В.Дрозд, Е,Л,Полин, И.В.Егорова и Ю,В.Дрозд (53) 681.325(088.8) (56) Авторское свидетельство СССР

Q 1635183, кл. G 06 F 7/52, 11/00, 1988.

Авторское свидетельство СССР

М 243964, кл, G 06 F 7/52, 11/10, 1968. (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЕЛ (57) Устройство относится к вычислительной технике и позволит делить два числа с исправлением одиночных ошибок. Цель изобретения — повышение надежности.

Устройство содержит регистры делителя и делимого, принимающие делитель А и делимое В, блок деления, определяющие метоИзобретение относится к вычислительной технике и может быть использовано в цифровых устройствах для выполнения операций деления, Цель изобретения — повышение надежности устройства.

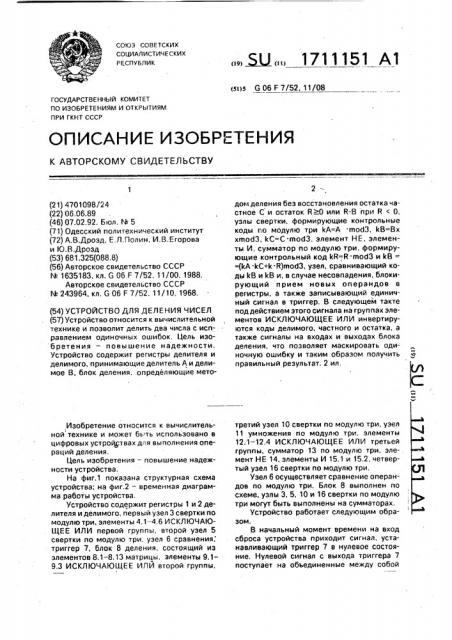

На фиг.1 показана структурная схема устройства; на фиг.2 — временная диаграмма работы устройства.

Устройство содержит регистры 1 и 2 делителя и делимого, первый узел 3 свертки по модулю три, элементы 4.1-4,6 ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, второй узел 5 свертки по модулю три, узел 6 сравнения, триггер 7, блок 8 деления, состоящий из элементов 8.1-8.13 матрицы, элементы 9.19,3 ИСКЛЮЧАЮЩЕЕ ИЛЙ второй группы, ». Ж,, 1711151 А1 дом деления без восстановления остатка частное С и остаток R O или R-В при R < О, узлы свертки, формирующие контрольные коды nо модулю три kA=A mod3, kB=Bx хтобЗ, kC=C mod3, элемент НЕ, элементы И, сумматор по модулю три, формирующие контрольный код kR=,, R mod3 и kB =

=(МА -kC+k R)mod3, узел, сравнивающий коды kB u kB и, в случае несовпадения, блокирующий прием новых операндов в регистры, а также записывающий единичный сигнал в триггер, В следующем такте поддействием этого сигнала на группах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ инвертируются коды делимого, частного и остатка, а также сигналы на входах и выходах блока деления, что позволяет маскировать одиночную ошибку и таким образом получить правильный результат. 2 ил. третий узел 10 свертки по модулю три, узел

11 умножения по модулю три, элементы

12.1 — 12.4 ИСКЛЮЧАЮЩЕЕ ИЛИ третьей группы, сумматор 13 по модулю три, элемент НЕ 14, элементы И 15.1 и 15,2, четвертый узел 16 свертки по модулю три.

Узел 6 осуществляет сравнение операндов по модулю три. Блок 8 выполнен по схеме, узлы 3, 5, 10 и 16 свертки по модулю три могут быть выполнены на сумматорах, Устройство работает следующим образом.

В начальный момент времени на вход сброса устройства приходит сигнал, устанавливающий триггер 7 в нулевое состояние. Нулевой сигнал с выхода триггера 7 поступает на объединенные между собой

1711151

ЗО

40 входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой 4, второй 9 и третьей 12 групп, обеспечивая тем самым трансляцию информации с первых входов на входы этих элементов без изменения. На входы делимого и делителя устройства поступают двоичные коды положительных чисел B и А соответственно делимого и делителя. По внешнему сигналу "Запись" эти коды заносятся в регистры 2 и 1. с выходов которых поступают без изменения соответственно через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы 4 и непосредственно на входы элементов матрицы 8, выполняющей деление чисел без восстановления остатка, На первый вход первого элемента 8,1 первой строки матрицы 8 поступает единичное значение с инверсного выхода триггера 7. Это значение транслируется через второй выход и первый вход последующего элемента на все элементы первой строки. обеспечивая вычитание в дополнительном коде делителя из старших разрядов кода делимого.

На первых выходах первых элементов строк матрицы 8 определяются разряды частного, а на четвертых выходах элементов

8.9+8.12 последней строки матрицы вычисляется остаток R, если 8 =. О, или величина

{R-В) в дополнительном коде, если R < О.

Разряды част oro и остатка транслируются через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ

9 и 12 второй и третьей 4-рупп соответственно без изменения на выходы третьего

10 и четвертого 16 узлов свертки по моду-. лю три соответственно, Выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы

9 являются выходами устройства и определяюг разряды частного. Коды „елителя А и делимого В с выходов регистров делителя

1 и делимого 2-, а также код частного С с выходов элементов ИСКЛЮЧАЮЩEE

ИЛИ второй группы 9 поступают соответственно на входы первого 3, второго 5 и третьего 10 узлов свертки по модулю три, которые формируют контрольные коды по модулю три: КВ=ВглобЗ, КА=АгпобЗ, kC=Cmod3.Ê0èTðoëüHûå коды kB u kC далее поступают на входы узла 11 умножения по модулю три, который вычисляет их произведения по модулю три, поступающие на первую группу входов сумматора

13 по модулю три. Код с выходов элемен: ов ИСКЛЮЧАЮЩЕЕ ИЛИ третьей группы

12 поступает на входы четвертого узла 16 свертки по модулю три, формирующего контрольный код остатка кр=йгпобЗ при R 0 .или код kR=(R-В)гпобЗ при R < О. Этот код поступает на входы сумматора 13 по модулю три, на другие входы которого подаются слагаемые, комплексирующие разницу между кодами kR u kR для случая R<0.

Для этого код kB при R<0 ???????????????????????? ?????????? ???????????????? ?? 15,2 ?? 15,1 ???????????? ?????????????????? ???? ???????????? ?????????? ?????????????????? 13 ???? ???????????? ??????, ???????????? ???????? ???????????????????? ???????????????????? ???????????????? ???????????? ?? ???????????? ???????????????? ???? 14. ???? ?????????????????? ?????? r<0 ?????????????????? ????????????????, ???????????????????????????? ??????????????, ?????????????? ?????????????????????? ???????????????????????????? ???????????????? ???????? ???????????????? r-??, ?????????? ??????????????, ???????????????? ?????? ?????????????????? ?????????????????????? ?????? kb =(kA

1С+КВ)тобЗ, который сравнивается по модулю три на узле 6 сравнения с кодом kB. В случае несовпадения по модулю три кодов

kA и kB, что имеет место при неправильном функционировании устройства. узел 6 сравнения формирует единичный сигнал, блокирующий запись следующих разрядов в регистры делителя 1 и делимого 2 с началом следующего такта, а также записывающийся в начале следующего такта в триггер

7 (фиг.2), С выходов триггера 7 единичный сигнал поступает на входы элементов ИСКЛЮЧАЮЩЕЕЕ ИЛИ первой 4, второй 9 и третьей 12 групп. обеспечивая инвертирование кодов, поступающих на их вторые входы. При этом инвертируют сигналы на первом, третьем и четвертом входах, а также первом, втором и четвертом выходах каждого элемента матрицы 8. Такое инвертирование сигналов маскирует ошибку, проявившуюся на предыдущем такте, и позволяет получить инверсию правильного частного на вторых входах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы 9, а на их выходах — прямое значение правильного результата.

Формула изобретения

Устройство для деления чисел, содержащее регистры делимого и делителя, блок деления, четыре узла свертки по модулю три, узел сравнения. причем информационные входы регистров делимого и делителя соединены с входами делимого и делителя устройства, выходы регистра делителя соединены с входами первого узла свертки по модулю три и входами делителя блока деления, выходы регистра делимого соединены с входами второго узла свертки по модулю три, выходы которого соединены с первыми входами узла сравнения, о т л ич а ю щ е е с я тем, что. с целью повышения надежности, устройство содержит три группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, триггер, узел умножения по модулю три, сумматор по модулю три, элемент НЕ, два

1711151 элемента И, причем выходы разрядов регистра делимого соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ первой группы, выходы которых соединены с входами делимого блока деле- 5 ния, выходы разрядов частного которого соединены с первыми входами элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, выходы которых соединены с выходами частного устройства и с входами третьего узла 10 свертки по модулю три, выходы которого соединены с входами первого операнда узла умножения по модулю три, выходы которого соединены с входами первого слагаемого сумматора и модулю три, вхо- 15 ды второго слагаемого которого соединены с выходами четвертого узла свертки по модулю три, входы которого соединены с выходами элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ третьей группы, первые входы кото- 29 рых соединены с выходами остатка блока деления, выходы первого узла свертки по модулю три соединены с входами сомножителя узла умножения по модулю три и

25 первыми входами первого и второго элементов И, выходы которого соедичены с входами третьего слагаемого сумматора по модулю три, выходы которого соединены с вторыми входами узла сравнения, выход которого соединен с входами блокировки записи регистров делимого и делителя и информационным входом триггера, вход сброса триггеоа соединен с входом сброса устройства, вход записи устройства — с входами 1.возражения записи регистров делимого и делителя и синхровходом триг- гера, прямой выход которого соединен с вторыми входами элементов ИСКЛЮЧАЮ "(ЕЕ ИЛИ всех групп, инверсный выход триггера — c входом логической единицы блока деления, выход старшего разряда частного устройства соединен с входом weмента НЕ, выход которого соединен с вторыми входами первого и второго элементов И и первым входом четвертого слагаемого сумматора по модулю три, второй вход четвертого слагаемого которого соединен с входом логического нуля устройства.

1711151

Редактор A. Коэориэ

3 каэ 340 Тираж Подписное

ВЧИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

" дроа" Д Залаете

Выход рп. Ю

Выюд эа 7

Составитель Н. Маркелова

Техред М.Моргентал Корректор Н, Король