Устройство для контроля хода программ

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для контроля хода программы в мультилрограммных вычислительных системах с динамически изменяемым приоритетом выполнения программы. Целью изобретения является расширение области применения. Устройство содержит счетчик, блок элементов ИЛИ, первый, второй и третий блоки элементов И, два регистра, генератор тактовых импульсов, элемент задержки и К блоков памяти, каждый из которых содержит триггер , второй элемент задержки, элемент ИЛИ, схему сравнения, элемент НЕ, два регистра , два элемента И. Устройство обеспечивает запоминание и восстановление оставшегося времени выполнения К прерванных программ. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (st)s G 06 F 11/28

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4672008/24 (22) 03.04.89 (46) 07.02.92. Бюл. N 5 (72) В.Ю.Анисимов, И.X. Галимзя нов, А.В.Тихобаев, А.Г. Ш евчи к и П.В.Денисович (53) 681.3(088.8) (56) Клямкин 3.Н. Схемный и тестовый контроль автоматических цифровых вычислительных машин. М.: Советское радио, 1963, с.91 — 92, рис.8.4.

Авторское свидетельство СССР

N 894713, кл. G 06 F 11/28, 1980, (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ХОДА

ПРОГРАММ (57) Изобретение относится к вычислительной технике и может быть использовано для

Изобретение относится к вычислительной технике и может быть использовано в мул ьтип рог раммн ых вычислительных системах с динамическим приоритетом выполняемых программ, Цель изобретения — расширение области применения.

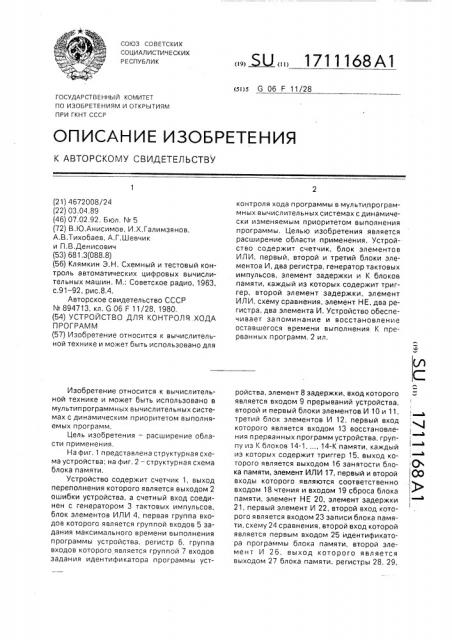

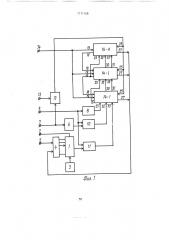

На фиг. 1 представлена структурная схема устройства; на фиг. 2 — структурная схема блока памяти.

Устройство содержит счетчик 1, выход переполнения которого является выходом 2 ошибки устройства, а счетный вход соединен с генератором 3 тактовых импульсов, блок элементов ИЛИ 4, первая группа входов которого является группой входов 5 задания максимального времени выполнения программы устройства, регистр 6, группа входов которого является группой 7 входов задания идентификатора программы уст„„5U) „„1711168 А1 контроля хода программы в мультипрограммных вычислительных системах с динамически изменяемым приоритетом выполнения программы. Целью изобретения является расширение области применения. Устройство содержит счетчик, блок элементов

ИЛИ, первый, второй и третий блоки элементов И, два регистра, генератор тактовых импульсов, элемент задержки и К блоков памяти, каждый из которых содержит триггер, второй элемент задержки, элемент

ИЛИ, схему сравнения, элемент НЕ, два регистра, два элемента И. Устройство обеспечивает запоминание и восстановление оставшегося времени выполнения К прерванных программ. 2 ил. ройства, элемент 8 задержки, вход которого является входом 9 прерываний устройства, второй и первый блоки элементов И 10 и 11, третий блок элементов И 12, первый вход которого является входом 13 восстановле, ««Ъ ния прерванных программ устройства, группу из К блоков 14-1, ..., 14-К памяти, каждый ! а из которых содержит триггер 15, выход которого является выходом 16 занятости бло-,0 ка памяти, элемент ИЛИ 17, первый и второй IQP входы которого являются соответственно входом 18 чтения и входом 19 сброса блока памяти, элемент НЕ 20, элемент задержки

21, первый элемент И 22, второй вход кото1 рого является входом 23 записи блока памяти, схему 24 сравнения, второй вход которой является первым входом 25 идентификатора программы блока памяти, второй элемент И 26, выход которого является выходом 27 блока памяти, регистры 28, 29, 1711168 выходы которых являются выходами 30 и 31 блока памяти, а информационные входы являются информационными входами 32, 33 блока памяти, Вход 34 являются входом сброса устройства.

Устройство работает следующим образом, В начале работы устройства на вход 34 подается сигнал сброса, передаваемый далее на входы 19 каждого из блоков 14. Блоки

15 памяти сбрасываются в состояние "свободно", В момент запуска каждой программы в счетчик 1, используя вход 5 и блок 4, записывают дополнительный код максимального времени ее выполнения, через вход 7 в регистр 6 заносится код идентификатора программы, В процессе выполнения программы на счетный вход счетчика 1 поступает тактовые импульсы от генератора 3.

Если времА выполнения программы превосходит максимально допустимое, на соответствующем выходе счетчика 1 формируется сигнал переполнения, который через выход

2 устройства поступает в систему прерывания. При мультипрограммном режиме работы возможно прерывание данной программы для выполнения программ более высокого приоритета, При этом естественно, возникает необходимость сохранения и восстановления кода оставшегося времени выполнения прерванных программ.

Сигналы прерывания поступают на вход 9 устройства и далее через элемент 8 на вход 23 блока 14-1. Кроме того, сигналы прерываний поступают на блоки 10 и 11 элементов и в этом случае с выхода регистра

6 на вход 32 блока 14-1 памяти подается код, идентифицирующий прерываемую программу, а из счетчика 1 на вход 33 блока 14-1 памяти подается дополнительный код оставшегося времени выполнения этой программы, Таким образом, при поступлении сигнала прерывания создаются условия для записи идентификатора прерванной программы в блок 14-1, После записи этого кода в блок 14-1 информация с выходов 30 и 31 блока 14-1 подается на входы 32 и 33 блока

14-2. Сигнал с выхода 16 блока 14-1 подается на вход 23 блока 14-2 и инициирует перезапись информации из блока 14-1 в блок

14-2. После записи информации о прерванной программе в блок 14-2 на выходе 16 этого блока вырабатывается сигнал, передаваемый на вход 18 блока 14-1, Блок 14-1 переходит в состояние "свободно". Аналогичным образом информация о прерванной программе переписывается из i-го блока памяти в -1-ый, при условии, что 1-1-ый блок памяти находится в состоянии "свободно", В итоге информация о первой прерванной

55 программе помещается в К-ый блок памяти, о второй прерванной программе — в К+1-ый и т.д. После записи информации о прерванной программе начинается выполнение программы вызвавшей прерывание, При этом в счетчик 1 через блок 4 вновь заносится дополнительный код максимально допустимого времени выполнения программы, а через информационный вход 7 в регистр 6 заносится код, идентифицирующий саму программу, При возвращении к обработке прерванных программ на вход 7 подается код, идентифицирующий восстанавливаемую программу, который записывается в регистр

6, Кроме того, с входа 13 подается сигнал восстановления, инициирующий передачу кода восстанавливаемой программы через блок 12 на входы 25 каждого из блоков 14 памяти, На выходе 27 того из блоков 14, в котором полученный код идентификатора программы совпал с хранимым кодом, вырабатывается дополнительный код оставшегося времени выполнения восстанавливаемой программы, Этот код через блок элементов

ИЛИ 4 передается на информационный вход счетчика 1. Если дополнительный код оставшегося времени считан из I-го блока памяти, блок 14-i памяти переходит в состояние "свободно". Если при этом -1-ый блок памяти группы 14 находится в состоянии

"занято", создаются условия для перезаписи информации и. ; i-1-го блока памяти в блок

14- . После пере=аписи i-1-ый блок памяти переходит в состояние "свободно", а если -2-ой блок памяти в этот момент находится в состояние "занято", информация из него переписывается в i-2-ый блок памяти и т.д.

Таким образом, информация, хранимая в блоках14, всегда "поджимается", насколько это возможно, к К-му блоку 14-К, Во время выполнения восстановленной программы устройство работает обычным образом.

Блок 14 памяти работает следующим образом, В момент запуска на вход 19 подается сигнал, который, пройдя через элемент

ИЛИ 17, сбрасывает триггер 15 в нулевое состояние, что соответствует состоянию

"свободно" блока памяти, и "разрешает" запись информации в регистры 28 и 29. Причем в регистр 28 записывается код, идентифицирующий программу, а в регистр

29 — дополнительный код оставшегося времени выполнения данной программы, Информация, находящаяся в регистрах 28, 29, может быть считана соответственно с выходов 30 и 31 блока памяти, Сигнал, разрешающий запись, через элемент И 22, элемент

21 задержки передается на вход установки триггера 15, что приводит к переключению

1711168 триггера в единичное состояние. Блок памяти переходит в состояние "занято".

Для считывания информации из блока

14 памяти на вход 25 считывается код и рограммы, который передается на второй вход схемы 24 сравнения и сравнивается с кодом, хранящимся в регистре 28. При совпадении кодов сигнал с выхода компаратора поступает на второй вход элемента И 26, С выхода регистра 29 на выход 27 блока памяти передается дополнительный код оставшегося времени выполнения программы, информация о которой хранится в данном блоке памяти. Кроме того, при успешном сравнении сигнал с выхода схемы 24 поступает также через элемент ИЛИ 17 на вход сброса триггера 15, в результате чего данный блок памяти переходит в состояние

"свободно".

Формула изобретения

Устройство для контроля хода программ, содержащее блок элементов ИЛИ, счетчик, генератор тактовых импульсов, первый блок элементов И, причем группа входов задания максимального времени выполнения программы устройства подключена к первой группе входов блока элементов

ИЛИ, группа выходов которого соединена с группой установочных входов счетчика, счетный вход которого соединен с выходом генератора тактовых импульсов, информационный выход и выход переполнения счетчика соединены соответственно с информационным входом первого блока элементов И и выходом ошибки устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет возможности контроля длительности выполнения программ, которые допускают изменение приоритетов прерванных программ, в него введены второй и третий блоки элементов И, элемент задержки, регистр, группа из К-блоков памяти (К вЂ” количес во прерванных программ), причем вход прерывания устройства подключен к стробирующим входам первого и второго блоков элементов И и через элемент задержки — к входу записи первого блока памяти группы, вход задания кода идентификации программы устройства соединен с информационным входом регистра и информационным входом третьего блока элементов И, стробирующий вход которого соединен с входом признака восстановления программы уст5

55 ройства, выход регистра соединен с информационным входом второго блока элементов И, выход третьего блока элементов И соединен с первыми информационными входами блоков памяти группы, вход начальной установки устройства соединен с входами начальной установки блоков памяти группы, выходы первого и второго блоков памяти группы соединены соответственно с первым и вторым информационными входами первого блока памяти группы, выход занятости каждого блока памяти группы, кроме последнего, подключен к входу записи последующего блока памяти, второй и третий информационные выходы i-го блока памяти группы (1-i-n) соединены с соответствующими информационными входами

I+1-го блока памяти группы, третий информационный выход i-го блока памяти группы соединен с соответствующим входом второй группы входов блока элементов ИЛИ, выход занятости i-го блока памяти группы, кроме первого, соединен с входом чтения -1-го блока памяти группы, каждый блок памяти группы содержит элемент ИЛИ, триггер, два регистра, схему сравнения, два элемента И, элемент НЕ и элемент задержки, причем первый и второй входы элемента

ИЛИ являются соответственно входом чтения и входом начальной установки блока памяти, выход элемента ИЛИ подключе». к нулевому входу триггера, выход которого является выходом занятости блока памяти и через элемент НЕ соединен с первым входом первого элемента И, второй вход которого соединен с входом записи блока памяти. выход первого элемента И соединен с входами записи первого и второго регистров и через элемент задержки — с единичным входом триггера, информационные входы регистров являются соответственно вторым и третьим информационными входами блока памяти, выходы регистров соединены соответственно с первым входом схемы сравнения и первым входом второго элемента И и являются первым и вторым информационными выходами блока памяти, выход схемы сравнения соединен с вторым входом второго элемента И и третьим входом элемента ИЛИ, второй вход схемы сравнения и выход второго элемента И являются соответственно первым информационным входом и третьим информационным выходом блока памяти.

1711168 г1

1711168 г.2

40

50

Составитель В. Быков

Техред M.Moðãåíòàë Корректор И.Муска

Редактор Т. Федотов

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 341 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5