Устройство для логической обработки изображений

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для реализации матричных оптических процессоров. Цель изобретения - повышение быстродействия устройства. Устройство содержит матрицы ячеек памяти и матрицы логических ячеек, а также блок управления , осветитель и оптоэлектронный затвор. Положительный эффект достигается за счет уменьшения числа тактов обработки, а также применения в составе ячеек биспинфотоприемников. 2 з,п. ф-лы. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si)s 6 06 Е 3/00, G 02 F 3/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТО РС КОМУ .СВИДЕТЕЛЬСТВУ (21) 4719346/24 (22) 14.07.89 (46) 07.02.92. Бюл. М 5 (71) Винницкий политехнический институт (72) В.Г.Красиленко, В.Н.Дубчак, В.И.Билык и B,Ä.Ôðoëîâ (53) 681.333(088.8) (56) Авторское свидетельство СССР

М 1645974, кл. G 06 G 9/00, 30.10.89. (54) УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОЙ ОБРАБОТКИ ИЗОБРАЖЕНИЙ

Изобретение относится к автоматике и вычислительной технике и может быть использовано для реализации матричных процессов.

Цель изобретения — повышение быстродействия устройства.

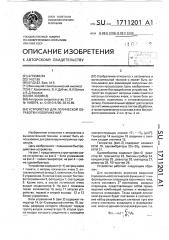

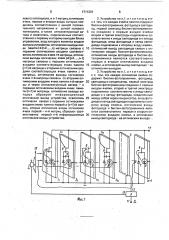

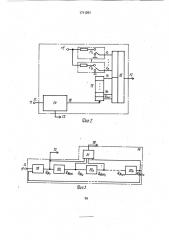

На фиг.1 представлена структурная схема устройства; на фиг.2 — блок управления; на фиг.3 —; на фиг.4- схема одновибратора.

Устройство содержит (и+1) матриц ячеек

1 памяти, г матриц логических ячеек 2, оптоэлектронный затвор 3, осветитель 4 и блок

5 управления. В состав ячеек входят биспинфотоприемники 6, фотодиоды 7, светодиоды

8. Кроме того,,в состав логический ячеек входит конденсатор 9, На фиг.1 показаны также коллиматор 10, вход 11 запуска устройства, первый и второй выходы 12 и 13 блока управления.

Блок управления 5 (фиг.2) содержит генератор 14, (и+1)-разрядный счетчик 15, выходы разрядов которого образуют первую группу входов коммутатора 16, вторая группа входов которого соединена с выходами

„„ Ц„„1711201 А1 (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для реализации матричных оптических процессоров. Цель изобретения— повышение быстродействия устройства. Устройство содержит матрицы ячеек памяти и матрицы логических ячеек, а также блок управления, осветитель и оптоэлектронный затвор. Положительный эффект достигается за счет уменьшения числа тактов обработки, а также применения в составе ячеек биспинфотоприемников. 2 з,п. ф-лы. 4 ил. соответствующих ключей 171 — 17> (р=2").

Генератор 14 выходом 18 соединен с счетным входом счетчика 15.

Генератор (фиг.3) содержит элемент

ИЛИ 19, одновибраторы 201-20>, элемент

ИЛИ 21.

Одновибратор содержит (фиг.4) резистор 22, транзистор 23, биспин-прибор 24, конденсатор 25, резистор 26, светодиод 27, резистор 28, RS-триггер 29.

Устройство работает следующим образом.

Для вычисления значения заданной (произвольной) логической функции от п информационных операндов картинного типа, нужно составить 2" минтермов входных операндов, представляющих собой произведения комбинаций прямых и инверсных входных операндов. Тогда каждой логической функции будет поставлен в соответствие набор разрешающих сигналов трго или иного минтерма, входящего в формирование именно данной логической функции, т.е. и.

1(х1,...,хп) = т А), J =1

1711201

20

30 где А = 1, если Т1 входит в логическую сумму, и А = 0 — в противном случае.

Таким образом, суть вычислительного процесса Заключается в последовательном формировании во времени значений текущих минтермов и в соответствии с той или иной логической функцией их разрешение (включение) или запрещение. Такое формирование в устройстве основано на использовании свойств биспин-фотоприемников, преобразующих оптические сигналы, поступающие на их оптический вход, в длительность определенного временного интервала задержки. Если со входа х на оптический вход соответствующего биспин-фотоприемника 6 подается оптический сигнал, то на выходе соответствующего светодиода 8 появляются последовательно разделенные некоторым временным интервалом tj импульсы, Ни х на Кихь где Ни — значение части произвольного минтерма, сформированного предыдущими информационными операндами. Таким образом в устройстве формируются последовательно расположенные во времени значения всех текущих минтермов, причем соответствующий управляющий сигнал с первого выхода

12 блока.5 управления разрешает прохождение соответствующего сформированного минтерма через оптоэлекронный затвор 3.

Последняя матрица ячеек памяти 1 +1 обеспечивает накопление разрешенных значений минтермов и формирование окончательного результата вычислений.

Время задержки т1 зависит от интенсивности входных операндов, напряжения питания и емкостей, конденсаторов 9, При постоянном питании и рассмотрении бинарных операндов временная задержка пропорциональна соответствующей применяемой емкости, B результате соответствующим подбором емкости в каждой из лдгических ячеек, а значит, и времени задержки формирования последовательности значений минтермов, обеспечивается формирование всех возможных 2 " значений соответствующих логических функций.

С другой стороны, в соответствующие моменты времени на вход оптоэлектронного затвора 3 должен быть подан соответствующий разрешающий сигнал, формируемый блоком

5 управления.

При подаче сигнала на вход 11 запуска устройства на выходе 18 генератора 14 последовательно во времени формируются электрические сигналы. Задержку сигналов обеспечивает каждый из одновибраторов

20> — 20р, причем время задержки пропорционально выбранному на переменном рези35

55 сторе 28 сопротивлению. Следовательно, на счетный вход счетчика 15 через интервалы времени tt будут поступать единичные сиг-. налыы.

Состояния ключей выбираются в зависимости от значения вычисляемой функции, т.е. сигнал формируется на выходах тех ключей 17>-17>, значения соответствующих термов которых должны войти в логическую сумму при окончательном формировании результата, В начальный момент времени значение счетчика равно единице, поэтому в зависимости от состояния первого ключа 17 на выходе 12 формируется "1" или "0". Затем через время г значение счетчика равно двум, поэтому уже в зависимости от состояния второго ключа 17г, на выходе 12 формируется "1" или "0". И т.д. до тех пор, пока значение счетчика не станет равным 2", когда будет сформирован последний управляющий сигнал.

Таким образом, формирование управляющих сигналов реализуется синхронно во времени с формированием соответствующих текущих значений минтермов.

Устройство обеспечивает выполнение всего спектра логических функций от картинных операндов при высоком быстродействии, обусловленном малым числом тактов и высоким быстродействием биспин-фотоприемников. При этом за счет одновременной подачи на входы xi картинныхоперандов нет необходимости применять дополнительные блоки памяти для хранения операндов.

Формула изобретения

1. Устройство для логической обработки изображений, содержащее блок управления, блок памяти, выполненный в виде первой матрицы ячеек памяти, первые и вторые входы которых соединены соответственно с шиной положительного напряжения и шиной нулевого потенциала, и блок формирования логических функций, выполненный в виде первой матрицы логических ячеек, первые и вторые входы которых соединены соответственно с шиной положительного напряжения и шиной нулевого потенциала, первые оптические входы логических ячеек первой матрицы связаны с оптическими выходами соответствующих ячеек памяти первой матрицы, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия устройства, в него дополнительно введены и матриц ячеек памяти, где п — количество обрабатываемых изображений, первые и вторые входы которых соединены соответственно с шиной положительного напряжения и с шиной ну1711201

1 левого потенциала, и п-1 матриц логических ячеек, первые и вторые вхбды которых соединены соответственно с шиной положительного напряжения и шиной нулевого потенциала, а также оптоэлектронный за- 5 твор и осветитель, подключенные соответ-, ственно к первому и второму выходам блока управления, вход которого является входом запуска устройства; оптические выходы яче. ек памяти!-й(1=2„...,n) матрицы связаны с 10 первыми оптическими входами соответственно логических ячеек 1-й матрицы, оптические выходы логических ячеек/-й O=1, ...,n-1). матрицы связаны с первыми оптическими входами соответствующих ячеек памяти 15 (+1)-й матрицы и вторыми оптическими входами соответствующих ячеек памяти j -й матрицы, оптические выходы логических ячеек и-й матрицы связаны со вторыми оп- тическими входами ячеек памяти и-й матри- 20 цы и через оптоэлектронный затвор — с первыми оптическими входами ячеек памяти (п+1)-й матрицы, оптические выходы которых образуют информационный оптический выход устройства, осветитель 25 оптически связан с первыми оптическими входами ячеек памяти первой и (и+1)- и матриц, вторые оптические входы логических ячеек первой -«n-й матриц образуют соо гветственно первый и-й информационные 30 оптические входы устройства.

2. Устройство по п.1, о т л и ч а ю щ е ес я тем, что каждая ячейка памяти содержит биспин-фотоприемник, фотодиод и светодиод, первый электрод биспин-фотоприемника соединен с первым входом ячейки второй и третий электроды подключены соответственно к аноду светодиода и к катоду фотодиода, анод фотодиода и катод светодиода подключены к второму входу ячейки, оптический выход светодиода связан с оптическим входом биспин-фотоприемника, оптические входы фотодиода и биспин-фотоприемника являются соответственно первым и вторым оптическими входами ячейки, а оптический выход светодиода — ее оптическим выходом.

3. Устройство по п.1, о т л и ч а ю щ е ес я тем, что каждая логическая ячейка содержит биспин-фотоприемник, фотодиод, светодиод и конденсатор, первый электрод биспин-фотоприемника соединен с первым входом ячейки, второй и третий электроды подключены соответственно к аноду светодиода и к катоду фотодиода, соединенным между собой через конденсатор, анод фотодиода и катод светодиода подключены к второму входу ячейки, оптические входы фотодиода и биспин-фотоприемника являются соответственно первым и вторым оптическими входами ячейки, а оптический выход светодиода — ее оптическим выходо .

1711201

1711201

45

Составитель С.Бабкин

Техред М.Моргентал Корректор Н.Ревская

Редактор М.Янкович

Заказ 342

ВНИИПИ Государственного к

Тираж Подписное о о комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент" . У т, г. жгород, ул.Гагарина, 101