Оптоэлектронное устройство для логической обработки изображений

Иллюстрации

Показать всеРеферат

Изобретение относится к оптической обработке информации и может быть использовано в различных системах параллельной обработки изображений при построении матричных процессоров для вычисления произвольных логических функций от бинарных изображений. Цель изобретения - повышение точности устройства . Устройство содержит последовательно оптически связанные первый оптический инвертор, первый оптический триггер, второй оптический инвертор, оптический затвор и второй оптический триггер, оптический выход которого является выходом устройства. Повышение точности устройства обусловлено его повышенной разрешающей способностью и отсутствием гальванических связей. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si)s G 06 К 9/00, G 02 F 3/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4622424/24 (22) 21.12.88 (46) 07.02.92. Бюл. KL 5 (71) Винницкий политехнический институт (72) В.Г.Красиленко и B.Н.Дубчак (53) 681.327.12(088.8) (56) Акаев А.А., Майоров С.А. Оптические методы обработки информации, — M.: Высшая школа, 1988, с. 187.

Авторское свидетельство СССР

М 1645974 (прототип). (54) ОПТОЭЛЕКТРОННОЕ УСТРОЙСТВО

ДЛЯ ЛОГИЧЕСКОЙ ОБРАБОТКИ ИЗОБРАЖЕНИЙ (57) Изобретение относится к оптической обработке информации и может быть исИзобретение относится к оптической обработке информации и может быть использовано в различных системах парал= лельной обработки изображений при построении матричных процессоров для вычислений произвольных логических функций бинарных изображений.

Целью изобретения является повышение точности устройства.

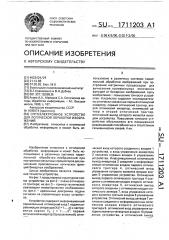

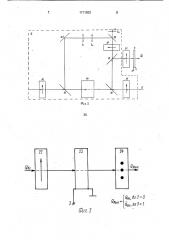

На фиг,1 представлена структурная схема устройства; на фиг.2 — схема оптического триггера; на фиг.3 — пример технической реализации инвертирования изображения; на. фиг.4 — временные диаграммы подачи сигналов на управляющие входы устройства.

Устройство содержит информационный параллельный оптический вход 1 подачи управляющих операндов Х, (i = 1,...,n) и настроечных картин Yj, j = 1,..„2", первый оптический инвертор 2 (управляемый), опти„„ЯЛ„„1711203 А1 пользовано в различных системах параллельной обработки изображений при построении матричных процессоров для вычисления произвольных логических функций от бинарных изображений. Цель изобретения — повышение точности устройства. Устройство содержит последовательно оптически связанные первый оптический инвертор, первый оптический триггер, второй оптический инвертор, оптический затвор и второй оптический триггер, оптический выход которого является выходом устройства. Повышение точности устройства обусловлено его повышенной разрешающей способностью и отсутствием гальванических связей. 4 ил. ческий вход которого соединен с входом 1 устройства, а вход управления инвертора

2 является первым. входом 3 управления устройства. Информационный оптический выход инвертора 2 соединен с информационным оптическим входом первого оптического триггера 4, оптический вход управления которого является вторым входом 5 управления устройства. Оптический выход первого оптического триггера 4 соединен с оптическим входом второго оптического инвертора 6, оптический выход которого соединен с оптическим входом оптического затвора 7, вход управления которого является третьим входом 8 управления устройства. Оптический выход затвора 7 оптически соединен с информационным оптическим входом второго оптического триггера 9, оптический вход управления которого является четвертым входом 10управления устройства, а оптический выход

1711203

10

20

55 второго триггера является выходом 11 устройства.

Оптические триггеры 4 и 9 являются 0защелками суммирования световых потоков. Такая защелка может включать в себя (фиг.2) поляризаторы 12, светообъединитель 13, транспарант 14, поляризатор 15, светообъединитель 16, светоделитель 17, анализатор 18, отражатели 19 и 20, а также линзы. В зависимости от наличия оптического сигнала на входе 5, являющегося управляющим сигналом для транспаранта 14 и источником усиления (подпитки), производится (или не производится) инверсия накопленной суммы. При использовании данной схемы триггера 4 функцию второго оптического инвертора выполняет анализатор 21. При этом, если на входе 5 присутствует сигнал, то плоскость поляризации оптического сигнала с выхода поляризатора

12 поворачивается транспарантом 14, поэтому на выходе анализатора 18 получается прямое, а на выходе анализатора 21 инверсное изображение. За время присутствия на входе 5 сигнала последовательно во времени накапливаются значения операндов

Х(Х) и У по схеме ИЛИ, а значение накопленной суммы окончательно инвертируется на выходе анализатора 21.

Инвертор 2 (фиг.3) содержит поляризатор.22, вращатель плоскости поляризации светового потока 23 и анализатор 24.

При указанной реализации блоков устройства входная информация кодируется ортогональным положением плоскости поляризации световых потоков, соответствующих логическим "0" и "1".

На фиг.4 приведены временные диаграммы подачи световых и электрических сигналов на информационный вход 1 и входы управления 3, 5, 8 и 10 устройства для двух операндов картинного типа Х> и Xz c формированием настроечных картин У<, Уг, Уз, У4, Они поясняют сущность работы устройства по вычислению логических функций . Устройство работает следующим образом.

Логическая функция от и бинарных изображений реализуется устройством по следующему закону П

f(X1,...,Х.)=0 Tj

j =1 где Т = X1+...+Xk+Xk+1+.;.Xn+Yj

X1...XkXk+1...Xn Yj — j-A терм, составленный из прямых (либо инверсных) операндов и j-ro настроечного изображения разрешения данного терма (т.е. если Yi=1, то данный терм участвует в формировании f(X>...,Õn), если же У1=0, то не участвует). Работа устройства заключается в двойном накоплении: первый оптический триггер 4 служит для формирования текущего терма Tj, вто-. рой 9-для логического суммирования сформированных термов.

Управляемый оптический инвертор (фиг.3) в зависимости от величины порогового сигнала на управляющем входе 3 производит передачу прямого изображения Xj, если сигнал на входе 3 отсутствует, или Хь

Yi при наличии сигнала на входе 3. Работа данного блока основана на изменении (вращении) плоскости поляризации вращателем 23 поляризованного с помощью поляризатора 22 изображения. Анализатор

24 выделяет прямое изображение Х в случае, если плоскость поляризации не изменена, в противном случае он инвертирует подаваемое изображение, При помощи первого оптического инвертора 2 подаваемые последовательно значения текущих операндов Xz и свое настроечное изображение У в зависимости от значения управляющего сигнала на первом управляющем входе 3 проходят либо прямые, либо инверсные (если на входе 3 присутствует "0", то изображения прямые, если "1" -то инверсные). При этом каждому настроечному изображению Yj всегда на управляющем входе 3 соответствует сигнал

"1", т.е. формируетсл У .

Снятием светового потока со второго 5 (четвертого 10) входа управления устройства достигается сбрасывание, т.е. подготовка к формированию очередного терма (вычислению другой логической функции).

Затвор 7 при помощи входа 8 срабатывает тогда, когда очередной терм изображений полностью сформирован первым триггером

4. При этом сформированное изображение терма через затвор 7 записывается во второй оптический триггер 9, суммируясь с значениями предыдущих термов, затем затвор

7 закрывается, а приведенный в состояние

"0" первый оптический триггер начинает формирование очередного терма изображений.

Отметим, что наличие в схеме второго триггера 9 третьего светоделителя 17 необязател ьно.

Пример вычисления логической функции от двух операндов Х> и Х рассмотрен на фиг.4. На оптический вход 1 устройства подают четыре серии изображений Х, Хг и

Y<, j = 1,...,4. На фиг.4 отмечено формирование адресов при считывании из оптического

ЗУ всех требуемых изображений. Чтобы хранить адреса текущих изображений и осуществлять выбор требуемой маски настро1711203

5 ф,..., Нп/ д Риа g 55

1 ечного изображения, нужно иметь logz(n+1) разрядов Э (данное число округляется до ближайшего большего числа). В данном случае необходимо два таких разряда. Если, например, значение этих разрядов 00, то выбирается адрес Х, если 01 — то Хг, если

10, то осуществляется выбор текущего значения разрешающей маски У, для формирования адресов которой нужно иметь дополнительно еще и разрядов, Хранение адресов Хь У с соответствующей прошивкой можно осуществлять с помощью ПЗУ, при каждом обращении к которому выдается адрес подаваемого текущего операнда из оптического ЗУ на оптический вход устройства. Синхронизация во времени подаваемых изображений совместно с подачей управляющих сигналов на входы 3, 5; 8 и 10 приведена на фиг.4, Время инвертирования текущего операнда (на Вх.3 сигнал логической "1") строго соответствует времени подаваемого операнда.

Состояние логической "1" на входе 5 необходимо для накопления суммы формирования всего текущего терма. Если осуществлен перебор. всех операндов и соответствующего настроечного изображения, инверсия всей логической суммы при помощи инвертора 6 (фиг.1) записывается (суммируется) вторым оптическим тригге- ром 9 при помощи открытого на необходимое время затвора 7, на вход 8 которого подается код."1". Сброс первого триггера 4 для формирования следующего терма осуществляется при помощи сброса входа 5.

Если все термы перебраны сбросом сигнала, на входе 10 осуществляется подготовка устройства к вычислению другой логической функции.

Отсутствие в устройстве блоков, имеющих дискретную структуру, обуславливает

5 высокую разрешающую способность устройства, которая определяется характеристиками входящих в его состав оптических элементов. Отсутствие гальванических связей между элементами устройства

10 обеспечивает высокую надежность и помехозащищенность устройства.

Формула изобретения

Оптоэлектронное устройство для логической обработки изображений, содержа15 щее первый и второй блоки формирования логических функций, причем оптический выход второго блока формирования логических функций является выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью

20 повышения точности устройства, первый и второй блоки формирования логических функций выполнены соответственно в виде первого и второго оптических триггеров, в устройство введены первый и второй опти25 ческие инверторы и оптический затвор, первый оптический инвертор, первый оптический триггер, второй оптический инвертор, оптический затвор и второй оптический триггер последовательно оптически

30 связаны, оптический вход первого оптического инвертора является входом устройства, а входы управления первого оптического инвертора, первого оптического триггера, оптического затвора и вто35 рого оптического триггера являются соответственно первым — четвертым входами управления устройства.

1711203 Риг. 2

1711203

10 с с и! ь с 4- ц

Э

Ц,. ь< ++K

NM.N с Q c3

II р 414 р

Ф с

Составитель С.Бабкин

Техред М.Моргентал

Редактор М.Янкович

Корректор Н.Ревская

Заказ 342 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101