Устройство для преобразования изображений объектов

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике, в частности к устройствам для преобразования изображений объектов, и может быть использовано для предварительной обработки изображений объектов. Целью изобретения является сокращение аппаратурных затрат. Для достижения цели обеспечивается коммутация информации на адресных входах блоков памяти и на входе данных второго блока памяти, организуется обмен информацией между первым и вторым блоками памяти, своевременное обнуление второго блока памяти и формиров,ание соответствующих управляющих сигналов . Это достигается путем введения в устройство для преобразования изображений объектов, содержащее коммутатор, два блока памяти, два сумматора, регистр и распределитель импульсов, содержащий элемент НЕ, три элемента И и элемент ИЛИ. второго элемента НЕ, счетчика и двух элементов задержки. 2 ил. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 06 К 9/36

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4741225/24 (22) 25.09.89 (46) 07.02.92. Бюл, М 5 (71) Научно-исследовательский институт телевизионной техники "Электрон" (72) Ю.А.Лысенко, С.А.Елманов и Н.А.Бурындин (53) 681.327.12(088.8) (56) Авторское свидетельство СССР

М 1234859, кл. G 06 К 9/36, 1986.. (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗОБРАЖЕНИЙ ОБЪЕКТОВ. (57) Изобретение относится к автоматике, в частности к устройствам для преобразова. ния изображений объектов, и может быть использовано для предварительной обра. ботки изображений объектов. Целью изоИзобретение относится к автоматике и может быть использовано для предварительной обработки изображений объектов.

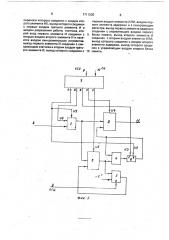

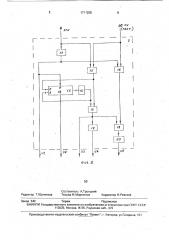

Целью изобретения является упрощение устройства, На фиг,1 приведена функциональная схема устройства; на фиг.2 — схема распределителя импульсов.

Устройство содержит коммутатор 1, первый 2 и второй 3 блоки памяти,.первый

4 и второй 5 сумматоры, регистр 6, распределитель 7 импульсов. На фиг.1 также показаны информационный вход 8 устройства, вход 9 кадровых синхроимпульсов, вход 10 синхроимпульсов, выход 11 устройства.

Распределитель 7 импульсов содержит. счетчик 12, элементы НЕ 13 и 14, элементы

И 15, 16 и 17, элемент ИЛИ 18 и элементы

19 и 20 задержки.

„„5LI 1711205 А1

Г бретения является сокращение аппаратур ных затрат. Для достижения цели обеспечивается коммутация информации на адресных входах блоков памяти и на входе данных второго блока памяти, организуется обмен информацией между первым и вторым блоками памяти, своевременное обнуление второго блока памяти и формирование соответствующих управляющих сигналов. Это достигается путем введения в устройство для преобразования изображений объектов, содержащее коммутатор, два блока памяти, два сумматора, регистр и распределитель импульсов, содержащий элемент НЕ, три элемента И и элемент ИЛИ, второго элемента НЕ, счетчика и двух элементов задержки. 2 ил.

Устройство работает следующим абра- д зом.

В промежутке между кадровыми гася° аааЬ щими импульсами цифровой k-разрядный код сигнала с информационного входа 8 устройства поступает на второй вход коммутатора 1, на управляющий вход которого O поступает сигнал, равный единице, с перво-. Ql го выхода распределителя 7 импульсов. С выхода коммутатора 1 код значения текущего отсчета сигнала поступает на адресные входы блоков 2 и 3 памяти.

На управляющий вход блока 2 памяти поступает значение сигнала с четвертого выхода распределителя 7 импульсов. Таким образом, в промежутке времени между кадровыми гасящими импульсами на управляющий вход блока 2 памяти сигналы записи не поступают и блок 2 памяти работает в режиме считывания. В ячейках блока 2 па-.

1711205

35

50

55 мяти хранятся соответствующие значения функции преобразования изображения, построенной на основе анализа гистограммы предшествующего кадра, и преобразованное значение сигнала с выхода блока 2 памяти поступает на выход 11 устройства.

Параллельно код текущего отсчета сигнала поступает на адресный вход блока 3 памяти, на выходе которого формируется значение содержимого соответствующей ячейки памяти. Затем оно увеличивается на единицу в сумматоре 5, поступает на вход данных блока 3 памяти и записывается в него по тому же адресу с приходом очередного импульса сигнала на управляющий вход блока

3 памяти. Далее на адресных входах блоков

2 и 3 памяти формируется значение следующего отсчета сигнала и начинается следующий такт работы устройства. На тактовый

- вход регистра 6 импульсы не поступают, а на его вход сброса в ноль поступает значение логической "1" с первого выхода распределителя 7 импульсов, Поэтому содержимое регистра 6 в промежутке между кадровыми гасящими импульсами равно нулю, Таким образом, перед началом кадрового импульса в блоке 3 памяти формируется гистограмма распределения уровней значений сигнала текущего кадра изображения.

С приходом текущего гасящего кадрового импульса на управляющем входе коммутатора 1 формируется значение логического "0" с первого выхода распределителя 7 импульсов. С второго выхода распределителя 7 импульсов на первый вход коммутатора 1 поступает номер такта работы устройства (0,1,2...N-1), начиная с времени прихода текущего гасящего кадрового импульса, который затем поступает на адресные входы блоков 2 и 3 памяти. В блоке 3 памяти считывается значение, содержащееся в его соответствующей ячейке, которое затем суммируется с содержимым регистра 6 и записывается в регистр 6. При этом импульсы на тактовый вход регистра 6 поступают с третьего выхода распределителя 7 импульсов, а на вход сброса регистра 6 поступает значение логического "0" с первого выхода распределителя 7 импульсов.

На вход сброса в ноль сумматора 5 с входа кадровых гасящих импульсов устройства поступает значение логической "1" и сумматор сбрасывается в нуль, т.е. на его выходе формируется нулевой код, который затем поступает на вход данных блока 3 памяти. После того как на входах блоков 2 и

3 памяти сформировались соответствующие значения, на их управляющие входы поступают импульсы с четвертого и пятого выходов распределителя 7 импульсов. Таким образом, по окончании N-ro такта работы, со времени начала текущего гасящего кадрового импульса, в блоке 2 памяти формируются значения функции преобразования для следующего кадра изображения, а блок 3 памяти обнулен. На протяжении последующих тактов работы (начиная с (N+1)го) во время текущего гасящего кадрового импульса значение адреса на втором выходе распределителя 7 импульсов не меняется, не поступают импульсы на управляющие входы блоков 2 и 3 памяти. Они работают только в режиме чтения, и их содержимое не меняется.

По окончании текущего гасящего кадрового импульса в блоке 2 памяти записана функция преобразования текущего кадра изображения, блок 3 памяти обнулен и готов к формированию гистограммы нового текущего кадра изображения.

Формула изобретения

Устройство для преобразования изображений объектов, содержащее коммутатор, первый и второй блоки памяти, первый и второй сумматоры, регистр и распределитель импульсов, содержащий первый элемент НЕ, первый, второй и третий элементы

И и элемент ИЛИ, причем первый информационный вход коммутатора является информационным входом устройства, выход коммутатора соединен с адресными входами блоков памяти, выход первого сумматора соединен с входом регистра, выход Котороro соединен с первым входом первого сумматора, выход второго сумматора соединен с входом данных второго блока памяти, о тл и ч а ю щ е е с я тем, что, с целью упрощения, в распределитель импульсов введены второй элемент НЕ, счетчик и первый и второй элементы задержки, причем выход второго блока памяти соединен с вторым входом первого сумматора и с первым входом второго сумматора, второй вход второго сумматора является входом логической "1" устройства, вход сброса в ноль второго сумматора является входом кадровых синхроимпульсов устройства, выход регистра соединен с входом данных первого блока памяти, выход которого является выходом устройства, вход первого элемента НЕ соединен с первым входом первого элемента И и является входом кадровых синхроимпульсов устройства, выход первого элемента Н Е соединен с первым входом второго элемента И, с входом сброса в ноль счетчика, с входом сброса в ноль регистра и с управляющим входом коммутатора, второй информационный вход которого соединен с информационным выходом счетчика, выход

1711205 переноса которого соединен с входом второго элемента НЕ, выход которогосоединен. с первым входом третьего элемента И и входом разрешения работы счетчика, второй вход первого элемента И соединен с вторым входом второго элемента И и является входом синхроимпульсов устройства, выход первого элемента И соединен с синхровходом счетчика и вторым входом третьего элемента И, выход которого соединен с первым входом элемента ИЛИ, входом первого элемента задержки и с синхровходом регистра, выход первого элемента задержки соединен с управляющим входом первого

5 блока памяти, выход второго элемента И соединен с вторым входом элемента ИЛИ, выход которого соединен с входом второго элемента задержки, выход которого соединен с управляющим входом второго блока

10 памяти.

gp. кц (rAw r3

Составитель А.Троицкий

Редактор T.Þð÷èêaBà Техред M.Mîðãåíòàë Корректор Н.Ревская

Заказ 342 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж 35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101