Резервированное запоминающее устройство с байтовой записью

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике/а именно к резервированным запоминающим устройствам, и может быть использовано при построении запоминающих устройств высоконадежных вычислительных машин. Целью изобретения является расширение области применения устройства за счет обеспечения Записи информации как в виде слова, так и полуслова. Устройство содержит два блока коррекции, два рабочих блока памяти и два дополнительных блока памяти, разрядные сетки которых разделены на две части. Каждый блок памяти снабжен двумя блоками управления , в состав которого входит ключ, коммутатор и регистр. Устройство позволяет, производить запись как слова, так и полуслова с перезаписью информации и одновременным устранением случайных сбоев. 1 ил. Ј

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)я G 11 С 29/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР,!

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4760891/24 (22) 14.08,89 (46) 07.02,92, Бюл. ¹ 5 (72) Л.А. Карева,Н.Б.Нифонтов,M.Н.Рогов и

В,Л.Сафронов (53) 681.327,6 (088.8) (56) Авторское свидетельство СССР

N1239751,,кл. G 11 С 29/00, 1985.

Авторское свидетельство СССР

¹ 1564696, кл. G 11 С 29/00, 1987.

i (54) РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С БАЙТОВОЙ ЗА-

ПИСЬЮ (57) Изобретение относится к вычислительной технике, а именно к резервированным запоминающим устройствам, и может быть

Изобретение относится к вычислительной технике, а именно к резервированным запоминающим устройствам, и может быть использовано при построении запоминающих устройств высоконадежных вычисли- . тельных систем.

Цель изобретения — расширение обла сти применения устройства за счет обеспечения записи информации как в виде слова, так и полуслова.

Для пояснения сущности изобретения одно полуслово информации, поступаемой в ЗУ, назовем первым байтом, а другое по- . луслово — вторым байтом. Каждый байт поступаемой информации кодируется в соответствии с правилом недвоичного двуизбыточного корректирующего кода, образуя кодовое полуслово. При этом кодовому" полуслову первого байта соответствуют первые части разрядов всех блоков памяти, а кодовому полуслову второго байта — их й. 171 1236 А1 использовано при построении запоминающих устройств высоконадежных вычислительных машин. Целью изобретения является расширение области применения устройства за счет обеспечения записи информации как в виде слова, так и полуслова.

Устройство содержит два блока коррекцйи, два рабочих блока памяти. и два дополнительных блока памяти, разрядные сетки которых разделены на две части. Каждый блок памяти снабжен двумя блоками управления, в состав которого входит ключ, коммутатор и регистр. Устройство позволяет, производить запись как слова, так и полуслова с перезаписью информации и одновременным устранением случайных сбоев. 1 ил. вторые части, При записи информации в ви де слова (т.е. обоих байтов) на входы устройства поступают кодовые"полуслова.первого и второго байтов, которые записываются в соответствующие им части разрядов блоков памяти (рабочих и дополнительных)..При.записи только одного байта сначала- во всех блоках памяти происходит предварительное считывание из них полуслова другого байта, которое заносится в соответствую щие регистры, и затем осуществляется за,пись в блоки памяти поступаемого на устройство кодового полуслова и предварительно считанного полуслова. Заметим, что . предварительно считанное полуслово при неисправности одного из блоков памяти может быть и не кодовым.

Таким образом, при записи байта соответствующее ему кодовое полуслово записывается в одни части разрядов всех блоков памяти, и происходит перезапись информа1711236 ции в других частях разрядов этих блоков.

При неисправности одного из блоков памяти (рабочих или дополнительных) может произойти ошибка.в обоих частях его разря, дов. Тогда ошибка в первой части разрядов этого блока исправляется в блоке коррекции (корректоре) первого байта при считывании достоверной информации из первых частей разрядов трех исправных блоков памяти, а ошибка во второй части разрядов неисправного блока памяти — в корректоре второго байта. Таким образом, устройство сохраняет отказоустойчивость, т.е, свою ра ботоспособность, в случае неисправности .одного из блоков памяти при записи информации как в виде слова, так и полуслова.

Повышение надежности связано с устранением последствий случайного сбоя в одном из блоков памяти за счет того, что при байтовой перезаписи предварительно считываемая информация для записи в регистры.снимается с выходов соответствующего корректора, тем самым устраняя случайную ошибку.

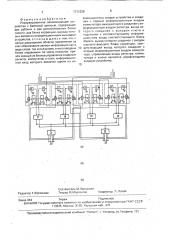

На чертеже изображена функциональная схема предлагаемого устройства, На чертеже приняты следующйе обозначения: 1 — входы кодового полуслова первого байта, 2 — входы кодового полуслова второго байта, 3 — 10 — ключи, 11 — 18 — регистры; 19-26 — коммутаторы, 27 и 28 — рабочие блоки памяти, 29 и 30 — дополнительные блоки памяти, 31 —.блок коррекции первого байта, 32 — блок коррекции второго байта, 33 — вход управления коммутаторов 19 — 22, 34 — вход управления коммутаторов 23 — 26, 35 — вход управления ключей 3 — 10, 36 и 37— входы управления регистров 11 — 18, 38 — выходы первого. байта, 39- выходы второго байта.

Устройство состоит из рабочих блоков

27 и 28 памяти, дополнительных блоков 29 и 30 памяти, блоков 31 и 32 коррекции и восьми блоков управления (на чертеже показаны пунктиром), Каждый блок управления (например, первые слева на чертеже) содержит регистр (11), ключ (3) и коммутатор . (19).

Разрядность каждого блока памяти одинакова и равна Ь (b — четное), так что разрядность входа 4 выхода каждой части его разрядной сетки равна Ь/2. Число разрядов входа каждого регистра 11 — 18 равно b/2 и равно числу разрядов входа каждого ключа

3-10. Этому же значению равно и число разрядов их выходов. Число разрядов входов каждого коммутатора 19 — 26 равно Ь (по

b/2 на каждый вход), а число разрядов выхода — b/2. Кроме того, каждый ключ и коммутатор имеют по одному управляющему входу, а каждый регистр — по два. Разрядность входного кодового полуслова первого байта равна разрядности входного кодового полуслова второго байта и равна 2Ь. Разряд5 ность входа каждого блока коррекции равна

2Ь и равна разрядности его выходов (каждый выход содержит по Ь/2 разрядов).

Устройство работает по следующему алгоритму, 10 b-разрядная сетка (число разрядов) каждого записываемого байта разбивается на две равные части, и каждая такая часть рассматривается как элемент поля мощности

2** (Ь/2), Каждый байт поступаемой двоич15 ной информации, таким образом, эквивалентен двум символам из поля. К этим двум символам в соответствии с правилом кодирования недвоичного двуизбыточного корректирующего кода, исправляющего

20 ошибки в одном символе, добавляются еще два символа, в результате чего образуется кодовое полуслова этого байта, Длина каждого из этих кодовых полуслов равна четырем символам поля GF 2** (Ь/2) или 2Ь

25 двоичным разрядам. Кодовое полуслово первого байта поступает на входы 1 устройства, а кодовое полуслова второго байта— на входы 2.

При записи сразу обоих байтов на уп30 равляющий вход 35 ключей 3-10 подается низкий потенциал, в результате чего эти ключи замыкаются и данные с входов 1 и 2 поступают на входы блоков памяти. При этом на управляющий вход 37 регистров

35 11 — 18 подается высокий потенциал, в результате чего эти регистры находятся в режиме высокого выходного сопротивления, и значение сигналов на управляющих входах

33 и 34 коммутаторов 19-26 не играет роли.

40 Ь-разрядные сетки блоков памяти также разбиваются пополам, причем в одни их части записываются симвОлы кодового полуслова первого байта, а в другие их части— символы кодового полуслова второго байта.

45 Например, в первой части дополнительного блока 29 памяти записан третий-символ кодового полуслова первого байта, а во второй его части — третий символ кодового полуслова второго байта.

50 При записи только одного байта процедура разбивается на два этапа — предварительное считывание из блоков памяти и последующая запись в них, При этом на управляющий вход 35 ключей 3 — 10 поступа55 ет высокий потенциал, в результате чего они размыкаются и не оказывают влияния на дальнейший процесс, а на управляющий вход 37 регистров 11 — 18 — низкий потенциап, что запрещает им переходить в состояние высокого выходного сопротивления.

1711236

На вторые входы коммутаторов 19-22 поступает информация с выходов 38 корректора 31, а на вторые входы коммутаторов

23-26 — с выходов 39 корректора 32. В соответствии со структурой используемого корректирующего кода разрядная сетка выходов каждого блока коррекции разбита на четыре равные части, соответствующие четырем символам полы 6Р 2**(b/2), и каждая такая часть образует один из четырех

10 выходов этого блока коррекции. Разбиение производится в соответствии с правилом образования кодовых полуслов первого и второго байтов.

На коммутатор 19 поступает информация с первого выхода корректора 31, на коммутатор 20 — с второго выхода, на

15 коммутатор 21 — с третьего выхода, на коммутатор 22 — с четвертого выхода. Аналогично на коммутатор 23 поступает информация с первого выхода корректора 32, на коммутатор 24 — с второго выхода, на коммутатор

25 — с третьего выхода, на коммутатор 26— с четвертого выхода.

При возникновении случайного сбоя в одном из. блоков памяти после предвари- тельного считывания на коммутаторы 19 — 22 или 23-26 поступает верная информация, что ведет к ликвидации последствия такого

30 сбоя.

Рассмотрим случай записи первого байта. Во время предварительного считывания регистры 11 — 18 работают в режиме записи; что достигается подачей на их управляющий вход 36 низкого потенциала. При этом низкий потенциал подается на управляющий вход 33 коммутаторов 19 — 22, вследствие чего они пропускают на регистры 11-14 информацию с входов 1 устройства, а на подается высокий потенциал, и они пропускают на регистры 15-18 информацию с выходов блока 32 коррекции второго байта.

Таким образом, при предварительном считывании в регистры 11 — 14 записывается кодовое полуслова первого байта, а в регистры 15 — 18 записывается информация, считанная из вторых частей разрядов блоков

27-30 памяти и "пропущенная" через блок

32 коррекции. Если в одном из блоков памяти происходит случайный сбой, то при такой процедуре он исправлен, что ведет к допол50 нительному повышению надежности. После предварительного считывания происходит. запись в блоки 27 — 30 информации из реги - 55 стров 11 — 18, что осуществляется подачей на управляющий вход 36 регистров 11-18 вы сокого потенциала. При этом информация из регистров 11 — 14 записывается в первые части разрядов блоков 27-30 памяти, а инуправляющий вход 34 коммутаторов 23-26 40 формация из регистров 15-18 — во вторые части разрядов этих блоков. В итоге в первые части разрядов блоков памяти записывается кодовое полуслово первого байта и происходит перезапись информации с коррекцией возможного сбоя из вторых частей разрядов этих блоков.

Аналогично происходит операция записи второго байта. Разница состоит лишь в том, что при предварительном считывании на управляющий вход 33 коммутаторов 19—

22 подается высокий потенциал, а на управляющий вход 34 коммутаторов 23 — 26— низкий. В разряды вторых частей блоков памяти записывается кодовое полуслово второго байта, и происходит перезапись информации с коррекцией возможного сбоя из разрядов первых частей.

Как при записи слова, так и при записи полуслова при исправной работе всех блоков памяти в их одноименных ячейках хранятся двэ кодовых полуслова.

Неисправность одного из блоков памяти может привести к ошибке лишь в одном символе в каждом из этих кодовых полуслов.

При считывании информация из разрядов первых частей всех блоков памяти поступает на соответствующие разряды входа блока 31 коррекции первого байта, а из разрядов вторых частей — на соответствующие разряды входа блока 32 коррекции второго байта, При.неисправности одного из блоков памяти или при их правильной работе на выходах 38 блока 31 коррекции первого байта получают кодовое полуслово первого байта, а на выходах 39 блока 32 коррекции второго байта — кодовое полуслово второго байта, Следовательно, при неисправности одного из блоков памяти не происходит нарушения работоспособности ЗУ, т.е. сохраняется исходная отказоустойчивость, Указанный алгоритм работы ЗУ обеспечивается подачей на управляющие входы

33-37 описанной выше последовательности сигналов переключения режимов работы ключей, коммутаторов и регистров. Эти сигналы могут вырабатываться, например, в

ЭВМ .на основании написанной по этому алгоритму прогpBMMbl, С помощью ЭВМ может также производиться кодирование первого и второго байтов.

Таким образом, изобретение по сравнению с прототипом позволяет расширить область применения устройства зэ счет обеспечения записи информации как в виде слова, так и полуслова при.сохранении его отказоустойчивости и добиться дополнительного повышения надежности путем ликвидации последствий последовательно возникающих сбоев.

1711236. за

45

Составитель M.Ëàïóøêèí

Техред М.Моргентал Корректор Л. Патай

Редактор Т.Юрчикова

Заказ 344 Тираж Подписное, ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101

Формула изобретения

Резервированное запоминающее устройство с байтовой записью, содержащее два рабочих и два дополнительных блока памяти, два блока коррекции, выходы которых являются информационными выходами устройства, отл ича ю щееся тем, что, с целью расширения области применения за счет обеспечения записи информации как в виде слова, так и полуслова, в него введены блоки управления по числу полуслов, причем каждый из блоков управления содержит регистр, коммутатор и ключ, информационный вход которого является одним из информационных входов устройства и соединен с первым информационным входом коммутатора, выход которого соединен с информационным входом регистра, выход ко5 торого соединен с выходом ключа и подключен к соответствующему информационному входу соответствующего блока ггамяти, выход которого соединен с входом соответствующего блока коррекции, соот10 ветствующий выход которого соединен с вторым информационным входом коммутатора, управляющие входы регистра, коммутатора и ключа являются управляющими входами устройства.