Устройство временной коммутации биимпульсных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике цифровой коммутации. Цель - повышение помехозамещенности. Устройство содержит блок 1 памяти информации, элемент ИЛИ 2, первый 3, второй 4, третий 5 элемент И, первый 6, второй 7, третий 8 инверторы, регистр 9, блок 10 распределения, блоки 11 выдачи сигналов, блок 12 коммутации служебных сигналов, счетчик 13 синхронизации . Цель достигается за счет преобразования бинарных сигналов, поступающих от источника, в биимпульсные, а также циклической передачи вводимой информации в течение времени, задаваемого источником. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН 1) Н 04 М 9/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И AST0PCHOINY СВИДЕТЕЛЬСТВУ уу

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

Il0 ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4757035/09 (22) 04,08.89 (46) 07.02.92, Бал. И 5 (72) В.П.Чуркин (53) 621.395.4(088.8) (56) Авторское свидетельство СССР

N 773955, кл. H 04 М 9/00 1979. (54) УСТРОЙСТВО ВРЕМЕННОЙ КОММУТАЦИИ

БИИМПУЛЬСНИХ СИГНАЛОВ (57) Изобретение относится к технике цифровой коммутации. Цель - повышение помехозамещенности ° Устройство содержит блок 1 памяти информации, .,Я0„„1711344 A 1

Ф элемент ИЛИ 2, первый 3, второй 4, третий 5 элемент И, первый 6, второй 7, третий 8 инверторы, регистр

9, блок 10.распределения, блоки 11 выдачи сигналов, блок 12 коммутации служебных сигналов,.счетчик 13 синхронизации. Цель достигается за счет преобразования бинарных сигналов, поступающих от источника, в биимпульсные, а также циклической передачи вводимой информации в течение времени, задаваемого источником.

2 ил.

1711344

10!

Изобретение относится к технике связи и может использоваться в цифровой коммутации.

Цель изобретения - повышение помехозащищенности.

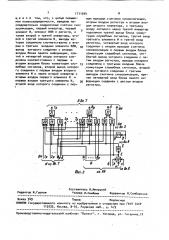

На фиг.1 изображена структурная электрическая схема устройства временной коммутации биимпульсных сигналов, на Фиг. 2 — структурная электрическая схема регистра, Устройство временной коммутации биимпульсных сигналов содержит блок

1 памяти информации, элемент ИЛИ 2, первыйй 3, второй 4 и третий 5 элементы И, первый 6, второй 7 и третий 8 инверторы, регистр 9, блок 10 распределения, блоки 11 выдачи сигналов, блок 12 коммутацйи служебных сигналов, счетчик. 13 синхронизации.

Регистр 9 содержит восемь четвертых элементов И 14 -14, девять пятых элементов И 154-15, шестой эле" мент. И 16, четвертый, 17 и пятый 18 инверторы, блок 19 сравнения, восемь седьмых элементов И 20 -20я, девять вторых элементов ИЛИ 214 - 2!я .

Устройство работает следующим образом.

Во временных интервалах адресноинформационной магистрали (АИИ) параллельным кодом передается информация в сопровождении адресов (номеpO8) исходящих JlNHHH CBRSH KQTOpblH эта информация принадлежит. Информация представляет собой коды. фронтов коммутируемых биимпульсных сигналов и код времени, определяющий моменты .времени выдачи биимпульсных сигналов в йсходящие линии связи. При этом кодом "!". кодируется передний фронт сигнала., а кодом "0" - задний фронт, Блок 1, работающий синхронно с

АИИ, принимает слова и, используя адрес линий связи, записывает информацию в соответствующие ячейки памяти. При этом каждая исходящая линия связи имеет свою ячейку памяти в блоке l. Номера линий связи и ячеек памяти совпадают.

Далее информация из ячеек памяти блока циклически считывается с помощью адреса А исходящих линий и тактов Ф, поступающих из счетчика

13, и выдается во временных интервалах электрической, цепи на вход блока 10, который обеспечивает запись биимпупьсного сигнала на блок 11.

55 выхода блока 11 биижпульсный сигнал поступает в исходящую линию связи. Таким образом, биимпульсные сигналы при транзитной коммутации поступают из входящих линий связи к выдаются с помощью устройства временной коммутации импульсных сигналов в соответствующие исходящие линии.

Однако служебные сигналы, поступающие на устройства управления (УУ) коммутационной системы, записываются в ячейки памяти блока 12 в бинарном (двоичном) коде, поэтому прежде чем выдать эти сигналы, в блок 1 их необходимо преобразовать из двоичного кода в биимпульсный.

Коммутация восьмиразрядных служебных,сигналов в исходящие линии связи осуществляется блоком 12, имеющим и ячеек памяти, закрепленных за исходящими линиями связи, т.е, блоки

1 и 12 аналогичны. Каждая исходящая линия. связи имеет свою ячейку памяти в блоке 12, в которую записывается код служебного сигнала из УУ.

На управляющие входы регистра 9 поступают бинарные восьмиразрядные

1 сигналы вместе с сигналами о = 1 и о = 1, а также с адресами А (номерами) исходящих линий связи, в которые эти сигналы после их преобразования в биимпульсный код необходимо выдать.

Запись бинарных сигналов и сигнала э из УУ через регистр 9 в блок 12 производится с помощью блока 19 сравнения и элементов И 15, ИЛИ 21 и инвертора 18. Блок 19 срав-! нения с помощью сигнала g = 1 осуществляется сравнение двух адресов А исходящих линий, поступающих из УУ и из счетчика 8. При совпадении этих адресов блок 19 вырабатывает сигнал, Я = 1, который открывает пятые элементы И 15 -15у пропуская сигнал

Д 1 и восемь разрядов служебного сигнала через вторые элементы ИЛИ 21 в соответствующую ячейку памяти блока !2. При этом с помощью четвертого инвертора 17 вырабатывается сигнал

f = 0, запрещающий передачу в блок 12 других сигналов через седьмые 20, четвертые 14 и шестой 16 элементы И, Информация, адрес и сигнал oC = сохраняются на входе регистра 9 ровно в течение одного цикла работы блока 1.2, что соответствует обслуживанию всех! 71I 344

ll ячеек памяти блока 12 и обеспечива" ет запись поступившей информмции в требуемую ячейку памяти блока 12 °

Запись и считывание информации в блок 12 коммутации служебных сигналов осуществляются"циклически с помощью тактов 1; и адреса А (фиг.1), поступающих, из счетчика 13 синхронизации. При этом на. одно обращение к блоку 12 (аналогично к блоку 1 памяти информации) производится вначале считывание информации из i-й ячейки памяти, а затем запись в эту .же i-ю ячейку памяти, что обеспечивает обслуживание одной (i-й) исхополовин каждого бита (разряда) бинарного восьмиразрядного сигнала в соответствующие импульсы биимпульсного сигнала производится с помощью элементов И 3-5,.ИЛИ 2, инверторов 7

6 и 8, а также блока 12 и счетчика 13.

При выдаче каждого нового биимпульсного БИ-кода с выхода элемента.

ИЛИ 2 на блок 1 памяти информации этот новый код записывается также в

50 тельно, ячейки памяти блока 12 имеют по 10 разрядов и хранят восьмиразрядные служебные сигйалы, сигнал и . одноразрядный биимпульсный БИ-код.

Сигнал в = 1 сопровожлает биимпульсный БИ-код при выдаче его в блок I, обеспечивая запись этого кода в ячейку памяти блока 1 по ад-. ресу А, поступающему из счетчика 13.

55 дящей линии связи. За и обращений к блоку 12, что соответствует циклу его работы, осуществляется обслуживание всех п исходящих линий связи.

Счетчик 13 синхронизации вырабатывает также с помощью своего самого,старшего разряда сигнал Р, который в течение нечетных циклов работы блока синхронизации равен "1" (P = 1), а в течение четных циклов = О. Это связано с тем, что каждый разряд восьмиразрядного двоич-.. ного служебного сигнала преобразуется в биимпульсный код за два цикла работы блока 12 и счетчика 13 синхронизации, причем(вначале пре-,, образуется первая половина импульса (разряда) бинарного сигнала при

1, а затем - вторая половина при f3 = О.

Преобразование первой и второй соответствующий разряд ячеек памяти блока 12 через регистр Я. Следова5 !

О I5

Сигнал Я = 1 запрещает запись информации в ячейки памяти блока 1 из адресно-информационной магистрали, а вместо нее записываются биимпульсный код БИ с выхода элемента ИЛИ 2 и нулевой код времени, т.е. код, состоящий из одних нулей. И пользование нулевого кода времени объясняется тем, что служебные сигналы выдаются в исходящие линии синхронно, т.е. цикл работы равен длительности одного импульса (бита) биимпульсного служебного сигнала.

Преобразование бинарных (двоичных) восьмиразрядных служебных сигналов,в биимпульсные осуществляется последовательно разряд за разрядом, начиная с первого (младшего) разряда, После преобразования очередного разряда служебный сигнал записывается в свою ячейку памяти блока 12 со сдвигом на один разряд в сторону младших разрядов. Поскольку каждый двоичный разряд преобразуется за два цикла работы блока 12 коммутации служебных сигналов, то в первом цикле, .когда преобразуется первая половина импульса, запись двоичного восьмиразрядного сигнала в i-ю ячейку памяти блока 12 осуществляется при P = 1 через седьмые элементы И 20, вторые элементы ИЛИ

21 без сдвига разрядов, а во втором цикле, когда преобразуется вторая половина (середина) двоичного импульса (разряда), запись служебного сигнала в i-ю ячейку памяти осу- ществляется при P = О с помощью сигнала P= с выхода четвертого инвертора !7 через четвертые элементы И !!!, вторые элементы ИЛИ 21 со сдвигом на один разряд,. Запись сигналао в соответствующий разряд ячеек памяти блока 12 осуществляется без сдвига сигналом =. = с выхода пятого инвертора 18 через шестой элемент

И 16 и второй элемент ИЛИ 12.

Формула и з о б р е т е н и я

Устройство временной коммутации биимпульсных сигналов, содержащее последовательно соединенные блок коммутации служебных сигналов, блок памяти информации и блок распределения, каждый из выходов которого соединен с входом соответствующего блока выдачи сигналов, о т л и ч а ю1711344

Составитель A.Èìêóöêèé техред Л.Олийнык Корректор. М. Самборская

Редактор И.Горная

Заказ 349 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина,10 щ е е с я тем, что, с целью повышения помехозащищенности, введены последовательно соединенные счетчик синхронизации, первый инвертор, первый элемент И, элемент ИЛИ и регистр, а

5 также второй и третий инверторы, второй и третий элементы И, выходы которых Соединены соответственно с вторым и третьим входами элемента ИЛИ, выход которого соединен с вторым входом блока памяти информации, третий и четвертый входы которого соединены соответственно с первым и вторым входами блока коммутации служебных сигналов, второй выход которого соединен с первым входом второго элемента И и через второй инвертор с вторым входом первого элемента И и первым входом третьего элемента И, щ второй вход которого соединен с пер- .

5 вым выходом счетчика синхронизации, вторым входом регистра и вторым входом второго инвертора, к третьему входу которого через третий инвертор подключен третий выход блока коммутации служебных сигналов, третий вход третьего элемента И и третий вход регистра, четвертый вход которого соединен с вторым выходом счетчика синхронизации и первым входом блока коммутации служебных сигналов, четвертый выход которого соединен с пятым входом регистра, выходы которого соединены с третьими входами блока коммутации служебных сигналов, второй вход которого соединен с третьим выходом счетчика. синхронизации, причем четвертый вход блока памяти информации соединен с шестым входом регистра.