Формирователь частотно-модулированных сигналов

Иллюстрации

Показать всеРеферат

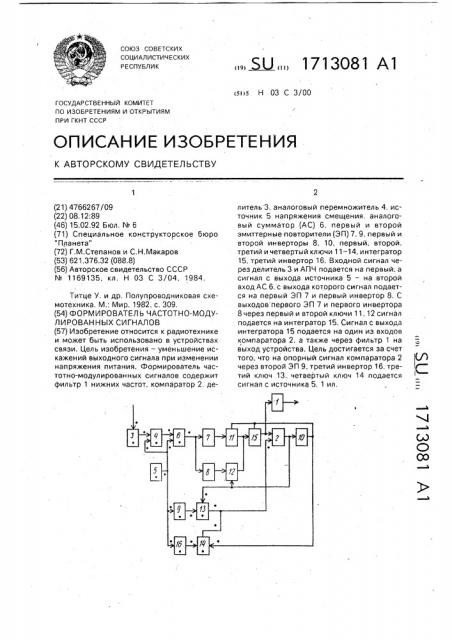

Изобретение относится к радиотехнике и может быть использовано в устройствах связи. Цель изобретения - уменьшение искажений выходного сигнала при изменении напряжения питания. Формирователь частотно-модулированных сигналов содержит фильтр 1 нижних частот, компаратор 2. делитель 3, аналоговый перемножитель 4. источник 5 напряжения смещения, аналоговый сумматор (АС) 6, первый и второй эмиттерные повторители (ЭП) 7, 9, первый и второй инверторы 8, 10, первый, второй, третий и четвертый ключи 11-14, интегратор 15, третий инвертор 16. Входной сигнал через делитель 3 и АПЧ подается на первый, а сигнал с выхода источника 5 - на второй вход АС 6, с выхода которого сигнал подается на первый ЭП 7 и первый инвертор 8. С выходов'первого ЭП 7 и первого инвертора 8 через первый и второй ключи 11,12 сигнал подается на интегратор 15. Сигнал с выхода интегратора 15 подается на один из входов компаратора 2, а также через фильтр 1 на выход устройства. Цель достигается за счет того, что на опорный сигнал компаратора 2 через второй ЭП 9, третий инвертор 16. третий ключ 13,- четвертый ключ 14 подается сигнал с источника 5. 1 ил.Ё

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4766267/09 (22) 08.12:89 (46) 15.02.92 Бюл, ¹ 6 (71) Специальное конструкторское бюро

"Планета" (72) Г.M,Ñòåïàíîâ и С.Н.Макаров (53) 621.376.32 (088.8) (56) Авторское свидетельство СССР

¹ 1169135, кл, Н 03 С 3/04, 1984.

Титце У. и др, Полупроводниковая схемотехника, М.: Мир, 1982, с. 309. (54) ФОРМИРОВАТЕЛЬ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ (57) Изобретение относится к радиотехнике и может быть использовано в устройствах связи. Цель изобретения — уменьшение искажений выходного сигнала при изменении напряжения питания. Формирователь частотно-модулированных сигналов содержит фильтр 1 нижних частот. компаратор 2. де„„SU „„1713081 Al литель 3, аналоговый перемножитель 4, источник 5 напряжения смещения. аналоговый сумматор (АС) 6, первый и второй змиттерные повторители (ЭП) 7, 9, первый и второй инверторы 8, 10, первый, второй, третий и четвертый ключи 11 — 14, интегратор

15, третий инвертор 16. Входной сигнал через делитель 3 и АПЧ подается на первый; а сигнал с выхода источника 5 — на второй вход АС 6, с выхода которого сигнал подается на первый ЭП 7 и первый инвертор 8, С выходов первого ЭП 7 и первого инвертора

8 через первый и второй ключи 11, 12 сигнал подается на интегратор 15. Сигнал с выхода интегратора 15 подается на один из входов компаратора 2, а также через фильтр 1 на выход устройства. Цель достигается за счет того, что на опорный сигнал компаратора 2 через второй ЭП 9, третий инвертор 16, третий ключ 13,. четвертый ключ 14 подается сигнал с источника 5. 1 ил.

1713081

Изобретение относится к радиотехнике и может быть использовано в устройствах связи.

Цель изобретения — уменьшение искажений выходного сигнала при изменении 5 напряжения питания, На чертеже приведена структурная электрическая схема предложенного формирователя, Формирователь содержит фильтр 1 10 нижних частот, компаратор 2, делитель 3 напряжения, аналоговый перемножитель 4, источник 5 напряжения смещения, аналоговый сумматор 6, первый эмиттерный повторитель 7, первый инвертор 8, второй 15 эмиттерный повторитель 9, второй инвертор 10, первый, второй, третий и четвертый ключи 11 — 14, интегратор 15 и третий инвертор 16.

Формирователь частотно-модулиро- 20 ванных сигналов работает следующим образом.

Входной сигнал через делитель 3 и аналоговый перемножитель 4 подается на первый, а сигнал с выхода источника 5 — на 25 второй вход аналогового сумматора 6, с выхода которого суммированный сигнал. попадает на входы первого эмиттерного повторителя 7 и первого инвертора 8. С выходов первого эмиттерного повторителя 7 и 30 первого инвертора 8 через соответственно первый 11 или второй 12 ключи этот сигнал подается на вход интегратора 15 в такой фазе, чтобы обеспечить перезаряд его емкости в требуемом направлении. Сигнал с 35 выхода интегратора 15 подается на один из входов компаратора 2, а также через фильтр

1 на выход формирователя частотно-модулированного сигнала, С того же источника 5 через второй эмиттерный повторитель 9, 40 третий инвертор 16 и третий 13 или четвертый 14 ключи сигнал в противофазе к входному сигналу интегратора 15 подается на второй вход компаратора 2.

При сравнении напряжений на обоих 45 его входах компаратор 2 переключается и, управляя непосредственно или через второй инвертор 10, первым, вторым, третьим и четвертым ключами 11 — 14, обеспечивает подачу сигналов на входы интегратора 15 и 50 компаратора 2 в требуемой фазе, Это обеспечивает формирование на выходе интегратора 15 треугольного сигнала с частотой, соответствующей уровню входного сигнала формирователя частотно-модулированных 55 сигналов. Фильтр 1 низких частот задерживает высшие гармонические составляющие сигнала, обеспечивая синусоидальную с изменяющейся частотой форму выходного сигнала.

Изменение напряжения питания неизбежно приводит к изменению выходного сигнала источника 5, Однако поскольку используется общий источник 5, по указанным причинам смещения центральной частоты не произойдет. Одновременно при изменении выходного сигнала источника 5 пропорционально изменяется коэффициент передачи аналогового перемножителя 4.

Это позволяет сохранить неизменным отношение изменения выходного сигнала аналогового сумматора 6, вызванного изменением входного сигнала, к значению выходного сигнала источника 5, а следовательно, сохранить значениедевиации частоты на заданном диапазоне изменения

ВходнОГО сиГнала.

Формула изобретения

Формирователь частотно-модулированных сигналов, содержащий последовательно соединенные первый эмиттерный повторитель, первый ключ, интегратор и фильтр нижних частот, последовательно соединенные первый инвертор и второй ключ, выход которого:подключен к входу интегратора, последовательно соединенные компаратор и второй инвертор. выход которого подключен к управляющему входу первого ключа, при этом вход первого эмиттерного повторителя соединен с входом первого инвертора, выход компаратора подключен к управляющему входу второго ключа, выход интегратора подключен к первому входу компаратора, о т л.и ч а ю шийся тем, что, с целью уменьшения искажений выходного сигнала при изменении напряжения питания, введены последовательно соединенные делитель напряжения, аналоговый перемножитель и аналоговый сумматор, выход которого подключен к входу первого эмиттерного повторителя, последовательно соединенные второй эмиттерный повторитель и третий ключ. выход которого подключен к второму входу компаратора, последовательно соединенные третий инвертор и четвертый ключ, выход которого подключен к второму входу компаратора, источник напряжения смещения, выход которого подключен к входам второго эмиттерного повторителя и третьего инвертора, а также к вторым входам аналогового перемножителя и аналогового сумматора, управляющие входы третьего и четвертогр ключей подключень: к выходам соответственно компаратора и второго инвертора, при этом вход делителя напряжения является входом формирователя частотно-модулированных сигналов.