Устройство для разъединения и объединения цифровых каналов

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ . РЕСПУ6ЛИК

ГОСУДАРСТВЕ ННЫИ КОМИТЕТ

ПО ИЗО6РЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

©

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 ,.(21) 4809420/09 (22) 02.04.90 . (46) 15.О2.92. Sen. hk 6 (71) Центрайьнйй научно-.исследователь-. скйй mew Связи

P2) ГЛ 1. Абугов, В.H. Литвиненко и А;М. Рах- ман (53) 621 395 376(088.8) (56) SHgN0Koll В.Д..и ggl. Ап таратуре уплотне- . ния ЙКМ-12М для сельской связи.М.; Связь, 1976, с. 45-53;

{54) VCTPOACf ВОДЛЯ РАЗЪЕДИНЕНИЯ И

ОБЪЕДИНЕНИЯ ЦИФРОВЫХ. КАНАЛОВ

„,5lJ,, 1713107 А1

2 (57) Изобретение относится к технике электрической связи. Цель изобретения— умейьшение временных искажений коммутируемых сигналов. С этой целью в устройстве коллектор. иереого транзистора 1 соединен через вы@ и аторой диоды 20 и

21с вйводами первмх обмотоктрансформатороа 22 и 23, вторые обмотки которых подключены к винам 27, 28 и 29, ЗО соответственно нервого и второго цифровог© канэл09. 1 ил.

1713107

Изобретение относится к технике электрической связи, а именно к устройствам для разъединения и объединения цифровых каналов.

Известна устройство для разъединения и объединения цифровых каналов, содержащее блоки разъединения и блоки объединения цйфровых каналов, включенные между входными шинами цифрового потока и шинами цифровых каналов.

Недостаток известного устройства разъединения и объединения цифровых каналов состоит в значительной сложности ега конструкции.

Известно также устройство для разъединения и объединения цифровых каналов, содержащее первый транзистор, эмиттер которого соединен с первым выводом первого резистора„база первого транзистора соединена с первым выводом первого конденсатора, второй резистор, третий резистор, первый вывод которого соединен с входной шиной цифровага потока, второй транзистор, база которого соедине- на с первым выводом четвертого резистора, эмиттер второго транзистора соединен с первым выводом пятого резистора, третий транзистор, база которого соединена с первым выводам шестого резистора. а эмиттер — с первым выводом седьмого резистора, второй вывод которого подключен к общей шине, которая соединена также с вторыми выводами первого. второго, пятага и васьмага резисторов, с вторым выводам первого конденсатора, с первыми выводами второго и третьего конденсаторов, первый и второй диод. первый и второй трансформаторы, выходную шину цифрового потока, которая соединена с первым выводом девятега рези, стора, десятый, одиннадцатый, двенадцатый и тринадцатый резисторы, первые и вторые шины первого и второго цифровых каналов, перву а и вторую входные шины импульсного питания, входную шину порогового напряжения и шину питания.

Недостаток устройства для разьединения и объединения цифровых каналов состоит в значительных временных искажениях коммутируемых сигналов.

Целью изобретения является уменьшение временных искажений коммутируемых сигналов.

С этой целью в устройстве для разъединения и объединения цифровых каналов, содержащем первый транзистор, эмиттер которого соединен с первым выводам первого резистора, база первого транзистора соединена с первым выводом первого конденсатора, втарбй резистор, третий резистор, первый вывод которого соединен с входной шиной цифрового потока, второй транзистор. база которого соединена с первым выводом четвертого резистора, эмиттер второго транзистора соединен с первым

5 выводом пятого резистора, третий транзистор, база которого соединена с первым выводом шестого резистора, а эмиттер — с первым выводом седьмого резистора, второй вывод которого подключен к общей ши10 не,, которая соеДинена также с вторыми выводами первого, второго, пятого и восьмого резисторов, с вторым выводом первого конденсатора, с первыми выводами второго и третьего конденсаторов, первый и второй

15 диоды, первый и второй трансформаторы, выходную шину цифрового потока, которая соединена с первым выводом девятого резистора, десятый, одиннадцатый, двенадцатый и тринадцатый резисторы, первые и

20 вторые шины первого и второго цифровых каналов, первую и вторую входные шины импульсного питания, входную шину порогового напряжения и шину питания, коллектор первого транзистора соединен с

25 вторыми выводами восьмого и девятого резисторов и с катодами первого и второго диодов, аноды которых соединены соответ- ственно с первыми выводами десятого и одиннадцатого резисторов и с первыми вы3О водами первых обмоток соответственно второго и nepeoro трансформаторов, вторые выводы которых соединены с вторыми выводами соответственно девятого и одиннадцатого резисторов и соответственно с первой

Э5 и второй входными шинами импульсного питания, вторые обмотки первого.и второго трансформаторов подключены первыми выводами к шине питания, а вторыми выводами — к первым шинам соответственно

4п первого и второго цифровых каналов. пер-. вые выводы третьих обмоток первого и второго трансформаторов соединены с вторыми шинами соответственно первого и второго цифровых каналов, вторые выводы

4 третьих обмоток первого и второго трансформаторов соединены с вторыми выводами соответственно третьего и еТорого конденсаторов, коллекторами соответственно третьего и второго транзисторов и ц) первыми выводами соответственно тринадцатого и двенадцатого резисторов, вторые выводы которых соединены с эмиттерами соответственно третьего и второго транзисторовв, вторые выводы четвертого и шесто55 го резисторов подключены к входной шине порогового напряжения, а вторые выводы второго и третьего резисторов подключенык базе первого транзистора.

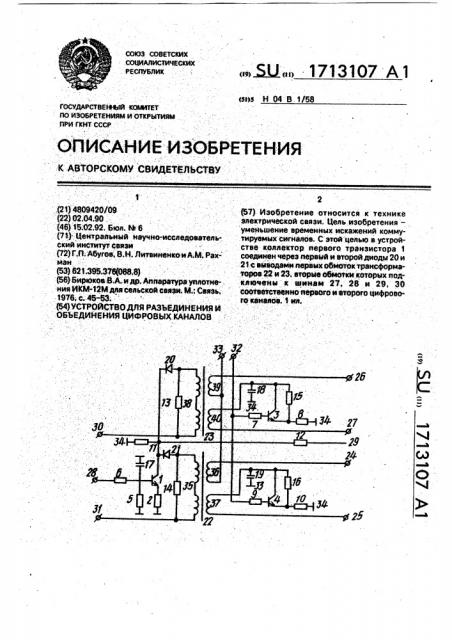

На чертеже изображен один из возможных вариантов предлагаемого устройства

1713107 для разъединения и объединения цифровых го 23 трансформаторов подключены первыканалов. ми выводами к шине 33 питания. Вторые

Устройство содержит первый транзи- обмотки 36 и 39 первого 22 и второго 23 стор 1, эмиттер которого соединен с первым трансформаторов подключены также вторывыводом первого резистора 2, второй 3 и. 5 ми выводами к первым шинам 24 и 26сооттретий 4 транзисторы, с второго по тринад- ветственно первого и второго цифровых цатый резисторы 5-16, первый 17; второй 18 каналов. Первые выводы третьих обмоток 37 итретий19конденсаторы,первый20ивто- и 40 первого 22 и второго 23 трансрой 21 диоды, первый 22 и второй 23 транс- форматоров соединены с вторыми шийами форматоры, первую 24 и вторую 25 шины 10 27 и 25 соответственно второго и первого первого цифрового канала, первую 26 и вто- цифровых каналов, Вторые выводы третьих рую 27 шины второго цифрового канала, обмоток 37 и 40 первого 22 и второго 23 входную 28 и выходную 29 шины цифрового трансформаторов соединены с вторыми выпотока, первую 30 и вторую 31 входные ши- водами соответственно третьего и второго ны импульсного питания, входную шину32 15 конденсаторов 19 и 18, с коллекторами порогового напряжения, шину 33 питания и соответственно третьего 4 и второго 3 транобщую шину 34; При этом первый трансфор- зисторов и с первыми выводами соответстматор 22 выполнен с первой 35, второй 36 и венно тринадцатого 16 и двенадцатого 15 третьей 37 обмотками, а второй трансфор- резисторов. 8торые выводы тринадцатого матор 23 — с первой 28, второй 39 и третьей 20 16 и двенадцатого 15 резисторов соединены

40 обмотками. с эмиттерами соответственно третьего 4 и

В устройстве база первого транзистора второго 3 транзисторов. При этом вторые

1 cоединена с первым выводом первого кон- выводы четвертого 7 и шестого 9 резисторов денсатора 17, а первый вывод третьего ре- подключены к входной шине 32 порогового эистора 6 соединен с входной шиной 28 25 напряжения, а вторые выводы второго 5 и цифрового потока. База второго транзисто- третьего 6 резисторов подключены к базе ра 3 соединена с первым выводом четверто- первого транзистора 1. го резистора 7. Эмиттер второго Устройство для разъединения и объедитранзистора 3 соединен с первым выводом нения цифровых каналов работает следуюпятого резистора 8. База третьего транзи- 30 щим образом. стара 4 соединена с первым выводом шес- Цифровой поток со скоростью передачи того резистора 9. Эмиттер третьего 64 кбит/с с входной шины 28 цифрового транзистора 4 соединен с первым выводом потока подается на базу первого транзистоседьмого резистора 10, второй вывод кото- ра 1 посредством третьего 6 и второго 5 рого подключен к общей шине 33, которая 35 резисторов, образующих делитель напрясоединена также с вторыми выводами пер- жения, При этом третий резистор 6 и первый вого 1, второго 5, пятого 8 и восьмого 11 конденсатор 17 образуют интегрирующую резисторов, с вторым выводом первого кон- цепь, обеспечивающую снижение крутизны денсатора 17 и с первыми выводами второго импульсов цифрового потока.

18 и третьего 19 конденсаторов. При этом 40 flo первой 30 и второй 31 входным шивыходная шина 29 цифровая потока соеди- нам импульсного питания подается импульнека с первым выводом девятого резистора оное питание, обеспечивающее разделение

12., цифрового потока со скоростью передачи 62

8 устройстве. кроме того, коллектор кбит/с на два-цифровых канала со скоропервого транзистора 1 соединен G вторыми 45 стью передачи 32 кбит/с. Если импульсное выводами восьмого 11 и девятого 11 рези- питание появляется на первой входной ши- . сторов и с катодами первого 20 и второго 21 не 30 импульсного питания, то информация диодов. Аноды первого 20 и второго 21 дио- проходитчерез второй трансформатор 23 на дов соединены с первыми выводами соот- первую 26 и вторую 27 шины второго цифветственно десятого 13 и одиннадцатого 14 50 рового канала. Если импульсное питание резисторов и с первыми выводами первых появляется на второй входной шине 31 имобмоток 38 и 35 соответственно второго 23 пульсного питания, то информация прохои nepsoro 22 трансформаторов. Вторые вы- дит через первый трансформатор 22 на . воды первых обмоток 38 и 35 второго 23 и первую 24 и вторую 25 шины первого цифпервого 22 трансформаторов соединены с 55 рового канала. Ответные сигналы, поступавторыми выводами соответственно десято- ющие по первым 29 и 25 и вторым 26 и 27 го 13 и одиннадцатого 14 резисторов соот- шинам первого и второго цифровых каналов ветственно с первой 30 и второй 31 после преобразования с.помощью первого входными шинами импульсного питания. 22 и второго-23 трансформаторов суммируВторые обмотки 36 и 39 первого 22 и второ- ются в точке соединения первого 20 и вто7

1713107 рого 21 диодов, а результат суммирования проходит через девятый, резистор 12 на выходную .шину 29 цифрового потока, При этом через вторые обмотки 36 и 39 первого

22 и второго 23 трансформаторов с шины 33 питания поступает дистанционное питание цифровых телефонных аппаратов. Третий транзистор 4 совместно с шестым 9, седьмым 10 и тринадцатым 16 резисторами и второй транзистор 3 совместно с.четвертым

7, пятым 8 и двенадцатым 15 резисторами обеспечивают предотвращение потребления тока при котором замыкании первых шин 24 и 26 первого и второго цифровых каналов и вторых шин 25 и 27 первого и второго цифровых каналов. На базу третьего транзистора 4 через шестой резистор 9 с шины 32 порогового напряжения поступает напряжение, при коротком третий транзистор 4 находится,в режиме насыщения, если ток нагрузки в первом цифровом канале не превышает максимального тока потребления цифрового телефонного аппарата. При этом ток ограничивается седьмым резистором l0. В случае увеличения тока третий транзистор постепенно закрывается за счет напряжения на седьмом резисторе 10, а через тринадцатый резистор 16 начинает и ротекать ток. При полном закрывании третьего транзистора 4 ток ограничивается седьмым 10 и тринадцатым 16 резисторами.

Работа второго транзистора 3 совместно с четвертым, пятым и двенадцатым резисторами 7, 8 и l5 происходит аналогично работе третьего транзистора 4 совместно с шестым 9, седьмым 10 и тринадцатым 16 транзисторами, Формула изобретения

Устройство для разьединения и объединения цифровых каналов, содержащее первый транзистор, эмиттер которого соединен с первым выводом первого резистора. база первого транзистора соединена с первым выводом первого конденсатора, второй резистор,третий резистор, первый вывод которого соединен с входной шиной цифрового потока, второй транзистор. база которого соединена с первым, выводом четвертого резистора. эмиттер второго транзистора соединен с первым выводом пятого резистора, третий транзистор, база которого соединена с первым выводом шестого резистора, а

10

50 восьмого и девятого резисторов и с катодами первого и второго диодов, аноды которых соединены соответственно с первыми выводами десятого и одиннадцатого резисторов и с первыми выводами первых обмоток соответственно второго .и первого трансформаторов, вторые выводы. которых соединены с вторыми выводами соответственно десятого и одиннадцатого резисторов и соответственно с первой и второй входными шинами импульсного питания, вторые обмотки nepaoro и второго трансформаторов подключены первыми выводами к шине питания, а вторыми выводами — к первым шинам соответственно первого и второго цифровых каналов, первые выводы третьих обмоток первого. и второго трансформаторов соединены с вторыми шинами соответственно первого:и второго цифровых каналов, вторые выводы третьих обмоток первого и второго трансформаторов соединены с вторыми выводами соответственно третьего и второго конденсаторов, коллекторами соответственно третьего и второго транзисторов и первыми выводами соответственно тринадцатого и двенадцатого резисторов, вторые выводы которых соединены с эмиттерами соответственно третьего и второго транзисторов, вторые выводы четвертого и шестого резисторов подключены к входной шине порогового напряжения, а вторые выводы второго и третьего резисторов подключены к базе первого транзистора. эмиттер- с первым выводом седьмого резистора, второй вывод которого подключен к общей шине; которая соединена также с вторыми выводами первого, второго, пятого и восьмого резисторов, с вторым выводом первого конденсатора. с первыми выводами второго и третьего конденсаторов, первый и второй диоды, первый и второй трансформаторы, выходную шину цифрового потока, которая соединена с первым выводом девятого резистора, десятый, одиннадцатый, две. надцатый и тринадцатый резисторы, первый и вторые шины первого и второго цифровых каналов, первую и вторую входные шины импульсного питания, входную шину порогового напряжения и шину пита.ния,отличающееся тем,что,с целью уменьшения временных искажений коммутируемых сигналов, коллектор первого транзистора соединен с вторыми выводами