Устройство для программного управления технологическим оборудованием

Иллюстрации

Показать всеРеферат

Изобретение относится к системам программного управления и может быть использовано в автоматизированных системах для управления технологическим оборудованием. Цель изобретения - повышение быстродействия и расширение области применения КС. Устройство для программного управления технологическим оборудованием 'содержит микропроцессор 1, тактовый генератор 2, системный контроллер 3, буферные усилители 4, дешифратор 5 адреса, блок 6 постоянной памяти программ, блок 7 оперативной памяти данных. шинный формирователь 8 оперативнойa,.LZ.2

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (g1)g G 05 В 19/18

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЬЛ ИЯМ

IlPH ГННТ СССР (21) 4702553/24

,(22) 03. 05.89 (46) 23.02.92. Бюл. Р. 7 (72) В.С.Харченко, Б.О.Сперанский, С.ш.Тюрин, В.П.Улитенко, Г.Н.Тимонь, кин, CH.Têà÷åíêo и Д.З.Крюков (533 621.503.55(088.8) (56) Авторское свидетельство СССР

V .1012205, кл. G 05 В 19/18, 1983.

Авторское свидетельство СССР

1418653, кл. G 05 В 19/18, 1988., Алексенко А.Г., Галицин А.А., Иванников A.Ä. Проектирование радиоэлектронной аппаратуры на микропроцессорах. - M.: Радио и связь, l984.

Коффрон Дж. Технические средства микропроцессорных систем. - M.: Мир, 1983.

ЯХ 17 l4575 А1

2 (54) УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УП"

РАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВА"

НИ ЕМ (57} Изобретение относится к системам программного управления и может быть использовано в автоматизированных системах для управления технологическим оборудованием. Цель изобретенияповышение быстродействия и расширение области применения КС. Устройство для программного управления технологическим оборудованием содержит микропроцессор 1, актовый генератор 2, системный контроллер 3, буФерные усилители 4, дешиФратор 5 адреса, блок 6 постоянной памяти программ, блок 7 оперативной памяти данных. шинный формирователь 8 оперативной

4 памяти, дешифратор 9 устройств вводавывода, шинный формирователь 1.0 вво да-вывода, шесть элементов ИЛИ 11- 16, два элемента И 17 и 18 три тригге- 5 ра 19-21, шинный формирователь 22, регистр 23, схему 24 сравнения, приоритетный шифратор 25, мультиплекИзобретение относится к устройствам программного управления и может быть использовано в автоматизированных системах для управления техноло- гическим оборудованием, например, в системах числового программного управления производственны:." комплексов, роботов, манипуляторов и т.д.

Известно устройство программного управления, содержащее датчики состояний, генератор импульсов, триггеры, дешифраторы, счетчики единиц и десятков, блок набора программ,, 2S элемент;. И, ИЛИ, НЕ, Его недостатком являетсл низкая произаодлтельность.

Наиболее близким к предлагаемому является устройство для программного управления технологическими процессами, состоящее из микропроцессора, тактового генератора, системного контроллера, дешифратора адреса памяти, оперативнои памяти, постоянной памяти, шинного формирователя памяти, дешифратора адресов ввода-вывода, шинных формирователей ввода-вывода, трех шинных формирователей, триггера, регистра, схемы сравнения, четырех схем И, — ðåõ схем ИЛИ.

Недостатком его является низкое быстродействие и узкая область применения. Это обусловлено следующими обстоятельствами.

Технические средства прототипа обеспечивают многоальтернативное ветвление по значению логических условий, поступакщих от датчиков, в строго определенные моменты времени, при подключении соответствующей подпрограммы основной программой. При этом заранее неизвестен факт изменения логических условий т.е. если они не изменились, то многоальтернативное ветвление будет проведено вхолостую - сформируется управляющий

55 сигнал такой же, как и в предыдущем ветвлении. Если логические условия уже изменились, а время их опроса сор 26, элемент 27 задержки. Цель достигается за счет реализации режима логического прерывания. Новыми в системе являются три элемента ИЛИ 14-16, два триггера 20 и 2 1, приоритетный шифратор 25, мультиплексор 26, эле" мент 27 задержки. 2 табл., 4 ил. еще не подошло, то это приводит к снижению времени реакции, понижающему быстродействие при многоальтернативном ветвлении относительно скорос; ти изменения логических условий; к невозможности использования известно". го устройства в тех задачах реального времени, которые требуют максимальной реакции, например в аварийных ситуациях технологического обору" дования, с которых сигнализирует не один датчик, а несколько (причем в ряде случаев необходим учет и предистории процесса).

Все это снижает быстродействие известного устройства и снижает область его применения.

Цель изобретения - повышение быстродействия и расширение области применения.

Сущность изобретения заключается в повышении быстродействия и расширении области применения устройства для программного управления технологичес". ким оборудованием путем введения дисциплины логического прерывания - прерывания с формированием автоматных отображений, старшего по приоритету обычных прерываний; в программной за" писи в регистр исходного состояния входов логических условий; в программном разрешении логического прерывания путем вывода логической единицы в первый триггер; в формировании обычных прерываний, а также прерываний при изменении состояния входов логических условий, старших по приоритету, чем обычные прерывания; в смещении адресов постоянной памяти для адресацли программ реакции на логическое прерывание, которая для микропроцессора расположена по тем же адресам, что и адреса подпрограмм (векторов) обычных прерываний; в программном Формировании автоматных отображений лля обработки изменения состояния входов логических условий

1714575 (реализация последовательностного или комбинационного автомата) с выдачей упра вляющих воздействий на инФормационные выходы; в программном снятии смещения адресов постоянной памяти после считывания микропроцессором команды возврата из логическоg го прерыванияв основнуюпрограмму, а также записи в регистр нового состо- 10 яния логических условий.

Введение второго триггера и соответствующих ему связей позволяет смещать адресное пространство блока постоянной памяти программ, переключить 15 мультиплексор по сигналу подтверждения прерывания, если значения логи" ческих условий изменились, а также записывать в регистр измененное значение логических условий при реализации новой дисциплины - логического прерывания - с формированием авто-. матных отображений.

Введение третьего триггера и соответствующих ему связей позволяЕт 25

Формировать запрос прерывания как при обычном прерывании, так и при логическом прерывании - с формированием автоматных отображений.

Введение приоритетного шифратора и соответствующих ему связей позволяет формировать код запроса, старшего по приоритету,и сигнал наличия запроса при обычных прерываниях, младших по приоритету логического прерывания, с формированием автоматных отображе35 ний, Введение мультиплексора и соответствующих ему связей позволяет формировать вектор прерывания как при обычных прерываниях, так и при логическом прерывании с формированием автоматных отображений.

Введение элемента задержки и соответствующих ему связей позволяет 45 обнулять второй триггер после считывания микропроцессором команды возврата из логического прерывания с целью устранения смещения блока постоянной памяти программ вторым триг- $Q герои.

Введение четвертого элемента ИЛИ и соответствующих ему связей позволяет обнулять второй триггер при начальном сбросе и по сигналу элемента задержки - no окончанию логического прерывания.

Введение пятого элемента ИЛИ и соответствующих ему связей позволяет устанавливать третий триггер для формирования запроса на прерывание как при обычном прерывании, так и при логическом прерывании.

Введение шестого элемента ИЛИ и соответствующих ему связей позволяет обнулять третий триггер после перехода микропроцессора в цикл обработки прерывания.

При использовании предлагаемого изобретения может быть получен положительный эффект, состоящий в повышении быстродействия и расширении области применения.

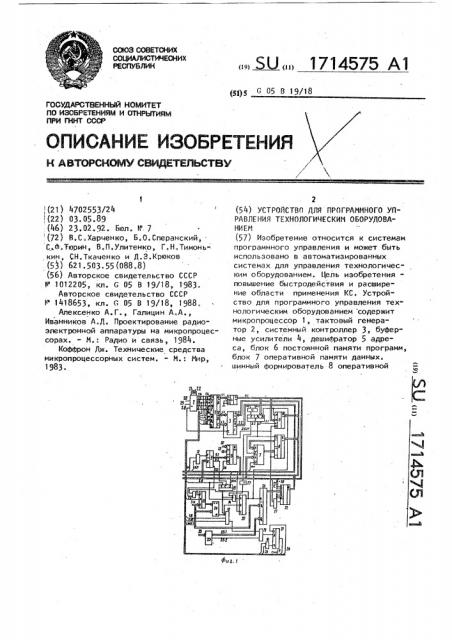

На Фиг.1 изображена функциональная схема системы для программного управления; на фиг.2 — фрагмент временной диаграммы реакции системы на обычное прерывание; на фиг.3 - то же, реакции на логическое прерывание с формированием автоматных отображений; на фиг.4 — граф последовательного автомата из примера конкретного выполнения системы.

Устройство для программного управления технологическим оборудованием содержит микропроцессор 1, содержащий выходы 1.1 адреса, группу входов-выходов 1.2 данных, выходы 1.3 управления записью и приемом данных, тактовые входы первой 1.4 и второй 1.5 фаз, входы сброса 1,6, готовности 1,7, выход 1.8 синхронизации, вход 1.9 запроса прерываний, выход

1,10 разрешения прерывания, тактовый генератор 2, соде ржащий входы 2.1 и 2.2 подключения кварцевого резонатора, вход 2.3 синхронизации, тактовые выходы первой 2.4 и второй 2.5 фаз, выход 2.6 сброса, выход 2.7 готовности, выход 2,8 синхронизации, системный контроллер 3, содержащий первую группу информациОнных ВхОдОВ выходов, вторую группу информационных выходов-входов 3.1 данных, являющуюся шиной данных устройства, выходы 32 управления чтением памяти, записью в память, управления вводом в устройстве ввода, выводом в устройстве вывода, подтверждения преры1 вания, являющиеся шиной управле- ния устройства, буферные усилители 4, содержащие выходы 4.1, являющиеся.шиной адреса устройства, дешифратор 5. адреса памяти, содержащий выход 5.1 подключения блока 6 постоянной памяти программ, блок 7 оперативной па" мяти данных, шинный формирователь 8

1714575 оперативной памяти, дешифратор 9 устройств ввола-вывода, содержащий группу выхолов 9.1 подключения устройств ввода-вывода, выходы 9.2 и 9.3 шинные формирователи 10 устройств ввода-вывода, шегть элементов ИЛИ 11-16, два элемента И 17 и 18; три триггера

19-21, шинный формирователь 22, регистр 23, схему 24 сравнения и приоритетный шифратор 25, имеющий информационные выходы 25.1 и выход 25.2 управления, мультиплексор 26, элемент 27 задержки, вход 28 сброса, вход 29 готовности, вход 30 захвата, и выход 31, информационные входы 32, информационные выходы 33, входы 34 логических условий, входы 35 запросов на прерывание.

Третий и четвертый входы тактового генера ора 2 являются входами сбро- са 28 ь ""ñ T-oBíocòè 29 устройства соответственно, Первый 2.4 и второй 2,5 тактовые выходы тактового генератора 2 подключены к первому 1,4 и Вто" рому 1..5 тктовым входам микропроцессора 1 соответственно. Третий 2,6 и четвертый 2,7 выходы тактового гене,ратора 2 подключены к входам сброса 1,6 и готовности 1.7 микропроцес g0 сора 1 соответственно. Пятый выход

2.8 тактового генератора 2 подключен к входу синхронизации системного контроллера

Адресные выходы 1.1 микропроцес-, сора 1 подключены к входам буферных усилителей 4, Группа входов-выходов

1.2 данных и выходы 1.3 управления записью и приемом данных микропроцессора 1 подключены к первой >-руппе информационных входов-выходов и входам управления записью и приемом данных системного контроллера 3 сооТ ветственно. Вход захвата микропроцессора 1 является входои 30 захвата системы. Выход ожидания микропроцессора 1 является выходом 31 ожидания

:системы. Выход управления приемом данных микропроцессора 1 подключен к .управляющим входам блока 6 постоянной "О памяти программ, шинного формирова.теля 8 оперативной памяти и к перво1 4, :му входу первого элемента И 17.

Объединенные инверсные выходы раз - 1

Ь5 решения буферных усилителей 4 подключены к отрицательной шине источника питания, выходы которых являются шиной 4.1 адреса устройства.

Вторая группа информационных входов-выходов системного контроллера 3 является шиной 3.1 данных устройства.

Выходы управления чтением памяти, записью в память, вводом, выводом, подl тверждения прерывания системного контроллера 3 являются шиной 3. 2 управле- ния устройства.

Группа информационных входов дешифратора 5 адреса памяти, выходы дешифратора 9 устройств ввода-вывода, адресные входы блока 7 оперативной памяти данных, блока.6 постоянной памяти программ подключены к шине 4.1 адреса устройства ° Вход разрешения дешифратора 5 адреса подключен к выходу первого элемента ИЛИ 1 1, первый и второй входы которого подключены к Bblxopàì управления чтения памяти и записи в память шины 3.2 управления соответственно, Первый выход

5.1 дешифратора 5 адреса подключен к первому входу разрешения блока 6 постоянной памяти программ. Второй выход 5.2 дешифратора 5 адреса подключен к входу разрешения шинного формирователя 8 оперативной памяти и к входу разрешения блока 7 оперативной памяти данных.

Информационные входы блока 7 оперативной памяти данных подключен к второй группе информационных входов" выходов шинного формирователя 8 one" ративной памяти. Информационные выходы блока 7 оперативной памяти данных подключены к третьей группе информационных входов-выходов шинного

Формирователя 8 оперативной памяти.

Вход разрешения дешифратора 9 устройств ввода-вывода подключен к . выходам управления вводом из устройств ввода и выводом в устройства вывода системного контроллера 3 че.рез элемент ИЛИ 12 соответственно.

Группа выходов 9.1 дешифратора 9 устройств ввода-вывода подключена соответственно к группе входов разрешения шинного формирователя 10 устройств ввода-вывода, вход разрешения которого подключен к выходу управления вводом из устройства ввода системного контроллера 3. Входы шинного формирователя 10 устройств ввода-вывода являются информационными входами 32 системы, а выходы - инФормационными выходами 33 устройства.

1714575

Выход первого элемента И 17 подключен к входу разрешения шинного формирователя 22.

Входы сброса регистра 23 и первого триггера 19 подключены к выходу

2.6 сброса тактового генератора 2.

Выходы регистра 23 подключены к первой группе входов схемы 24 сравнения, выход которой подключен к первому 10 входу второго элемента И 18, второй вход которого подключен к выходу перaoro триггера 19, информационный вход которого подключен к разряду шины 3.2 данных системы. Вход синхрони- 15 зации регистра 23 подключен к выходу третьего элемента ИЛИ 13, первый вход которого подключен к третьему выходу 9.3 дешифратора 9 устройства ввода-..вывода, а второй вход подклю- . 20 чен к выходу второго триггера 20, подключенному к адресному входу мультиплексора 26, старшему адресному входу блока 6 постоянной памяти про"

25 грамм и дополнительному информационному входу дешифратора 5 адреса. . Третий выход 5.3 дешифратора 5 адреса подключен к входу элемента 27 задержки, выход которого подключен к первому входу четвертого элемента З0

ИЛИ 14. Второй инверсный вход четвертого элемента ИЛИ 1 4 подключен к выходу первого триггера 19.Третий вход четвертого элемента ИЛИ 14 подключен к входу сброса первого триггера 19. Выход четвертого элемента ИЛИ 14 подключен к входу сброса второго триггера 20, информационный вход которого подключен к выходу схемы 24 сравнения, а выход синхронизации которого подклю- 40 чен к выходу подтверждения прерывания системного контроллера 3. Вход синхронизации первого триггера 19 подключен к второму выходу 9.2 дешифратора 9 устройств ввода-вывода. 45

Информационные входы регистра 23, вторая группа входов схемы 24 сравнения и. вторая группа входов мультиплексора 26 являются входами 34 логических условий системы. Второй вход первого элемента И 17 подключен к выходу подтверждения прерывания системного контроллера 3.

Третий вход второго элемента И 18 подключен к выходу 1.8 синхронизации микропроцессора 1, à его четвертый вход подключен к выходу 1.l0 разрешения прерывания микропроцессора 1.

:Выход второго элемента И 18 подключен к первому входу пятого элемента

ИЛИ 15, второй вход которого подключен к выходу 25.2 управления приоритетного шифратора 25.

Входы приоритетного шифратора 25 являются входам 35 запросов на пре" рывание системы. Информационные выходы 25.1 приоритетного шифратора 25 подключены к первой группе входов мультиплексора 26, выходы которого подключены к первой группе информационных входов шинного формирователя 22, к второй группе информационных входов которого подключены выходы блока формирователя команды векторного перехода, выполненного путем подключения соответствующих разрядов шинного формирователя через ограничительный резистор к положительному полюсу источника питания.

Выход пятого элемента ИЛИ 15 подключен к входу данных третьего триггера 2 1, вход сброса которого подключен к выходу шестого элемента ИЛИ 16.

Первый инверсный вход шестого элемента ИЛИ !6 подключен к выходу 1.10 разрешения прерывания микропроцессора 1, а второй его вход подключен к выходу 2.6 сброса тактового генератора 2. Выход третьего триггера 21 подключен к выходу 1.9 запроса прерывания микропроцессора 1. Вход синхронизации третьего триггера 21 подключен к тактовому выходу 2,4 первой фазы тактового генератора 2.

Микропроцессор 1 предназначен для выполнения программы, т.е. последовательности команд, используемой для реализации алгоритма управления и для управления системой с шиннойорганизацией. Микропроцессор воспринимает внешние тактовые сигналы и внешние

30-33 сигналы управления и генерирует сигналы адреса (1.1) данных (1.2) а также сигналы управления (1 3)

Микропроцессор 1 может быть реализован, например, на стандартной интегральной микросхеме КР580ИК89А.

Тактовый генератор 2 предназначен для формирования двух высоковольтных (12В) неперекрывающихся последовательностей тактовых импульсов (2.4, 2.5), формирования управляющих сигналов сброса (2.6) и готовности (2.7): по внешним сигналам системы (2.8, 2.9) и для формирования системного сброса (2.8) по синхроимпульсу (2.9), поступающему с микропроцессора 1, и

11 171457

f может быть реализован, например, на стандартной интегральной микросхеме

КР580ГФ24,(ножки 13,12 и 6 не задейст-, вуются).

Системный контроллер 3 предназначен для увеличения нагрузочной способности шины 3.1 данных и организации двунаправленной передачи данных, для фиксации слова управления микропроцессора 1, поступающего по шине данных в момент поступления системного строба (2.8) с тактового генератора 2, и формирования в соответствии со словом управления и сигналами

1 записи и приема данных (1.3) микропроцессора 1 шины 3.2 управления устройства для каждого машинного цикла. Г!ииа управления устройс — âà включает сигналы управления чтением памяти, записью в пано†ü,,вводом в устройство ввода, вь.водом из устройств вывода. подтверждения прерывания ° Системный контроллер 3 может быть оеализован, например, на стан- 25 дартно интегральной микросхеме !

УР580ВК28

Буферные усилители и шинные формирователи 8 и 10 предназначены для увеличения нагрузочной способности шины 3. 1 данных системы и для организации двунаправленной передачи данных по шине 3.1 данных (второй группы выходов-входов системного контроллера) к блокам памяти или из блоков памяти, к внешним устройствам или из

35 внешних устройств в зависимости от управляющих сигналов Е1 и Е2. При отсутствии управляющих сигналов выходы шинных Формирователей находятся ® в высокоимпедансном состоянии,т.е. отключены от шины данных. Шинные формирователи могут быть реализованы на стандартных интегральных микросхемах

589 Р.П1о.

Шинный формирователь 8 блока оперативной памяти данных, предназначен для увеличения нагрузочной способности шинных данных 3.1, для подключения выходов блока 7 оперативнои па" мяти к шине 3.1 данных в режиме чте ния, для подключения входов данных

:блока 7 оперативной памяти к шине 3.1 данных в режиме записи.

Шинные формирователи 10 вводавывода предназначены для увеличения ,нагрузочной способности шины 3.1 дан" ных и для подключения к шине 3,1 данных информационных входов 32 в ре12 жиме ввода из устройств ввода, для подключения шины 3.1 данных к информационным выходам 33 в режиме вывода в устройства вывода.

Буферные усилители 4 предназначены для усиления нагрузочной способности шины 4,1 адреса системы, а также для перевода своих выходов в высо" коимпедансное состояние при активиро вании разряда "Подтверждение захвата" выходов 1.3 управления микропроцес- сора 1.

Дешифратор 5 адреса предназначен для дешифрации адреса, выставленного на шине 4.1 адреса системы в том случае, если активирован выход элемента

ИЛИ li. Для подключения блока постоянной памяти программ возбуждается выход 5.1 дешифратора 5, для подключения блока 7 оперативной памяти данных и шинного Формирователя 8 оперативной памяти — выход 5.2.

Кроме того, дешифратор 5 адреса учитывает информацию на выходе триггера 20 и дешифрирует адреса команд возврата из программ обработки логического прерывания. При этом возбуждается выход 5.3. В обычном режиме работы дешифрация шины адреа производится с учетом нулевого состояния выхода триггера 20.

Дешифратор адреса может быть реализован, например, на стандартных интегральных микросхемах 155ИДЗ.

Дешифратор 9 устройств ввода-вы" вода предназначен для дешифрации ин" формации на шине 4.1 адреса системы в том случае, если активирован вы" ход элемента ИЛИ 12, для подключения шинных формирователей 10 вводы-вывода и инициализации системы на ло1 гическое прерывание. Для подключения шинных формирователей 10 ввода-вывода активируется один соответствующий разряд группы выходов 9.1 подключения внешних устройств. Для стробирования триггера 19, имеющего определенный адрес при выводе по этому адресу (ввод по этому адресу не ис- пользуется), активируется выход 9.2.

Для стробирования триггера 23 через элемент ИЛИ 13 таким же образом возбуждается выход 9.3. . Дешифратор 9 устройств ввода-вывода может быть реализован, например на стандартных интегральных микросхе-, мах 155 ИДЗ.

1.714575

Первый элемент ИЛИ 11 предназначен для формирования разрешающего сигнала

Е1 дешифратора 5 адреса памяти. по наличию на шине 3.2 управления одного из управляющих сигналов чтения памяти или записи в память.

Второй элемент ИЛИ 12 предназначен для формирования разрешающего сигнала для дешифратора 9 устройств ввода-вы- 10 вода при наличии на шине 3,2 управления одного иэ управляющих сигналов ввода из устройства ввода или вывода в устройство вывода.

Третий элемент ИЛИ 13 предназначен 15 для управления входом синхронизации регистра 23 как выходом 9.3 дешифратора 9, так и выходом второго триггера 20 для записи в регистр 23 или начального состояния логических условий входов 34, либо для записи иэмененного и уже обработанного значения логических условий входов 34.

4етвертый элемент ИЛИ 14 предназначен для управления входом обнуления 25 второго триггера 20 либо при начальном сбросе с выхода 2.6 генератора 2, либо сигналом с выхода элемента 27 задержки по окончанию логического прерывания - после считывания команды возврата микропроцессором 1, либо если отсутствует разрешеwe на логическое прерывание (обнулен первый триггер 19).

Пятый элемент ИЛИ 15 предназначен для управления входом данных третьего триггера 21 для формирования запроса на прерывание либо сигналом с выхода 25.2 приоритетного шифратора 25 (обычное прерывание) либо сигналом с второго элемента И 18 (логическое прерывание).

Шестой элемент ИЛИ 16 предназначен для управления входом сброса третьего триггера 21 либо при начальном сбросе - сигналом (2.6) тактового генератора 2, либо при обнулении,выхода 1. 10 разрешения прерывания микропроцессора 1. При активировании выхода элемента ИЛИ 16 триггер 21 обнулен независимо от информации на. его выходе данных и синхронизации.

Первый элемент И 17 предназначен для управления входом разрешения шинного формирователя 22 для подключе- . ния его выходов к шине 3.1 данных в том случае, если на шине 3.2 управления имеется управляющий сигнал подтверждения прерывания, а на выходах

1.3 управления микропроцессора 1 сигнал приема данных, т.е. когда микропроцессор считывает вектор прерывания с шины 3.1 данных.

Второй элемент И 18 предназначен для управления пятым элементом ИЛИ 15 при формировании запроса на логическое прерывание в том случае, если активирован выход схемы 24 сравнения (изменились логические условия), прерывания разрешены (активирован выход 1.10 микропроцессора 1), поступил синхроимпульс с выхода 1.8 микропроцессора 1 и установлен первыЙ триггер 19.

Ф

Первый триггер 19 предназначен для управления вторым элементом И 18 и четвертым элементом ИЛИ 14 с целью разрешения дисциплины логического прерывания. Если таковы запрещены, то элемент И 18 заблокирован, а триггер 20 через элемент ИЛИ 14 удерживается в нулевом состоянии.

Первый триггер 19 устанавливается в нулевое состояние начальным сбросом по своему асинхронному входу обнуления, устанавливается и обнуляется разрядом шины 3,1 данных по переднему фронту сигнала на выходе 9.2 дешифратора 9.

Первый триггер 19 может быть реализован, например, на стандартной интегральной микросхеме 155ТИ2.

Второй триггер 20 предназначен для управления старшим разрядом адреса блока 6 постоянной памяти программы, входом адреса мультиплексора 26 и третьим элементом ИЛИ 13 при реализации логического прерывания.

Второй триггер 20 устанавливается по переднему фронту управляющего сигнала подтверждения прерывания шины 3.2 управления, если активирован выход схемы 24 сравнения. Это необходимо для обеспечения приоритета изменений логических условий входов 34 по отношению к запросам на входах 35. Таким образом, даже если запрос на пре" рывание (1.9) вызван поступившим ранее запросом по входам 35, но логические условия уже изменились, либо запросы поступили одновременно, установится второй триггер 20 при формировании подтверждения прерывания, переключит мультиплексор 20, обеспечит смещение адресов постоянной памяти 6., т.е. обеспечит реализацию логического прерывания. Если прерыва15 1714575 16 ния запрещены программно, триггер 20 та ИЛИ 13. Регис р 3 у та ИЛИ 13. Регист 23 обнуляется на" никогда не установится, так как бу- чальным стробом - выходом 2,6 генерадет отсутствовать сигнал подтвержде- тора 2. Регистр 23 выдает хранимый ия прерывания, синхрониэируюший его. код постоянно на схему 24 ср юения.

Второй триггер 20 обнуляется через Регистр 23 может быть реализован, элемент ИЛИ 14 либо начальным сбро< например, на стандартных интегральсом, либо по окончанию логического ных микросхемах 155ИР13. и ерывания, либо удерживается в нуле- Схема 24 ср р д м 24 с авнения предназначена вом состоянии выходом первого триг- 10 для сравнения текущего кода логических условий на входе 34 с исходным гера 19.

Второй триггер 20 может быть ре- кодом, либо с последним обработанным алиэован, например, на стандартно ин - кодом, хранимым в рег р 3. р тегральной микросхеме 155ТИ2. несравнении возбуждается ее выход

Т етий триггер 21 предназначен 15 для управления эл в ения элементом И 18 и триг"

Р ом 20. для формирования запроса на прерыва- гером 0. ние на соответствующий вход тв ющий вход 1 9 микоп оцессора t при возбуждении его лиэована, например, на стандартных входа данных выходом пятого элемента интегральных микр сх 533

ИЛИ 16 по синхроимпульсу на входе щ Приоритетный шифратор 5 предназl,4 микропроцессора i. .Триггер 21 об- начен для шифрации с приоритетом обычнуляется через элемент е ." г ИЛИ 16 на- ных запросов на пребывание по входам 35. и формирует на выходах 25 ° 1 в нулевом состоянии при запрете на код номера ус р "с, р т ой тва старшего по прерывание. При снятии этого запрета 25 приоритету иэ всех устройств, выста(при обнулении выхода ИЛИ 16), если вивших логические единицы íà вхо5 П и наличии хотя бы одного поступили очередные запросы (активи- дах 35. При наличии х я д рован выход элемента ИЛИ 15), третий запроса на входах 35 возбуждается вытриггер 21 установится в состояние ход 25.2 приоритетного шифратора 25. логической единицы по синхроимпульсу g0 Приоритетны" фр р

П ио итетный шиф атор 25 может быть выхода 2.4 и сформирует очередной за- реализован например на стандартных прос прерывания . интегральных микросхемах 155ИВ1.

Третий триггер 21 может быть реализован, например, на стандартных подключения к шинному формироватеинтегральных микросхемах 155ТЮ . - лю 22 ли блинный формирователь 27 предназна- по приоритету) с выходов 25.1 приори31 нн тетного шифратора 25 (обычное прерыкода команды вектора прерь.вания, име- вание), либо собственно логических ющего-„я на выходе мультиплексора 26„ условий с входов 34 (логическое пре, ак ивировании его входа разреше- рывание). Управление адресным входом ния первым элементом И 1/. осуществляется выходом триггера 20 формирователь команды векторного Если он обнулен, то на выход мультиперехода реализуется путем подключе- плексора передается информация с выния разрядов входов 7,6,0 1 2 шинно ходов 25.1 приоритетного шифратора 25, го формирователя 22 к положительно- <5 если установлен - с входов 34. му полюсу источника питания через Мультиплексор 26 может быть реалиограничительный резистор, как это зован, например, на стандарных интегуказано на фиг ° l. Разряды 3-5 подклю ральных микросхемах 155К01 чены к выходам, мультиплексора 26. Элемент 27 задержки предназначен щинный формирователь 22 может быть для задержки сигнала, формируемого н например на стандартных на выходе 5,3 дешифратора 5 адреса

20 интегральных микросхемах . ы микросхемах 589 АП16. памяти, с целью обнуления триггера

Регистр 23 предназначен для эапи- после надежного считывания микропроси и хранения кода логических усло-. цессором 1 адреса возврата в основную вии входов . - ли

34 - либо исходного кода

ы программу иэ логического прерывания, ли о кода, б обработанного в последнем так как эта команда записана в блологическом прерыва м прерЫвании Информация с ке 6 постоянной памяти программ по входов 34 заносится в ре. гистр 23 зад" адресу с единицей в старшем разр е, ним фронтом сигнал ф сигнала на выходе элемен- активируемом выходом второго тригге1 71 4 >75

18 ра 20, а основная программа расположена по адресам с нулем в этом старшем разряде. Когда микропроцессор 1 считает команду возврата (при этом на ее адресе возбуждается выход 5,3 дешифратора 5), начнет операцию по извлечению из стэка адреса возврата (внутренние операции без обращения к памяти), тогда импульс на выходе элемента 27 задержки через элемент

ИЛИ 14 обнулит триггер 20.

Элемент 27 задержки может быть реализован, например, на четном количестве последовательно соединенных инверторов.

Вход 28 сброса предназначен для приема сигнала начального сброса системы.

Вход 29 готовности предназначен для приема внешнего сигнала готовности (например, с медленных носителей информации при загрузке блока 7 оперативной памяти).

Вход 30 захвата предназначен для . 25 приема сигнала захвата, например, с внешних быстродействующих носителей информации для инициирования прямого доступа в память.

Выход 31 ожидания предназначен для gp выдачи сигнала ожидания, если на входе 29 готовности - логический ноль.

Информационные входы 32 предназначены для приема информационных сигналов состояния оборудования, проверяемых программно без использования прерываний.

Информационные выходы 33 предназначены для выдачи управляющих сигналов на исполнительные органы, в том числе и сигналов, Ьрмируемых в обычном и логическом прерывании. В обычном прерывании часть этих выходов обнуляет флажки устройств, вызвавших прерывание после их обслуживания.

Входы 34 логических условий предназначены для приема логических условий, состояния дискретных датчиков технологического оборудования, изменения которых обрабатываются с использованием логического прерывания о формированием автоматных отображений от этих сигналов. Информация на входах 34 изменяется не быстрее времени выполнения логического прерыва- ния с учетом ожидания окончания обычного прерывания, если оно уже началось.

Входы 35 запросов на прерывание предназначены для приема сигналов запроса на прерывание (флажков устройств типа дисплея, клавиатуры, пульта оператора и пр.). Устройство выставляет на соответствующем разряде входов 35 логическую единицу триггером, принадлежащим техническим средствам этого устройства, который обнуляется в конце программы обслуживания данного устройства.

Устройство для программного управления работает следующим образом.

Обычное прерывание.

В этом режиме устройство программно разрешает прерывания. При этом на выходе 1. 10 разрешения прерывания микропроцессора устанавливается логическая единица (фиг.1 и 2). При появлении на входах 35 хотя бы..одной единицы, на выходе 25,2 приоритетного шифратора устанавливается логическая единица, которая, через элемент

ИЛИ 15 устанавливает триггер 21 по синхровходу 2,4, выходной сигнал которого подает на вход !.9 запроса прерывания микропроцессора логическую единицу. Микропроцессор 1 s последнем такте последнего цикла текущей команды, обнаружив запрос прерывания, устанавливает свой внутренний триггер прерывания и сбрасывает триггер разрешения прерывания и переходит в цикл обработки прерывания. В связи с этим, на выходе 1.10 устанавливается логический нуль, который по инверсному входу элемента ИЛИ 16 сбрасывает и блокирует триггер 21, запрещая установку по синхровходу 2.4. Код уст-. ройства, сформировашего запрос, установлен на выходе 25,1 приоритетного шифратора 25. После перехода микропроцессора 1 в цикл обработки прерывания в первом его цикле выдается слово состояния в системный контроллер 3 и возбуждается сигнал подтверждения прерывания (INTA на фиг. 1 и 2) шины 3,2 управления, Затем возбуждается управляющий сигнал приема (DBXN на фиг.1 и 2) шины 3,2 управления и возбуждается выход элемента И 17, активирующий вход разрешения шинного формирователя 22. С выходов 25.1 через мультиплексор 26 и шинный формирова" тель 22 на шину 3.1 данных выдается код вектора прерывания (КБТ на фиг.2) с помощью формирователя команды векторного перехода. Далее, микропро19 171 цессор организует запись,в стек адреса возврата (содержимое счетчика команд: СК на фиг.2) в точку прерван. ной программы и переходит к выполнению программы по адресу, соответствующему введенному коду вектора прерывания (RST) и снимает сигнал подтверждения. Программа обработки прерывания может включать запись в стек с последующим извлечением информации всех регистров, обработку информации с устройства, вызвавшего его, обязательно — обнуление триггера запроса прерывания этого устройства (с выходов 33, этот триггер относится к внешнему оборудованию и не указан на фиг.1). Поэтому снимается логическая единица с входов 35„ выходы 25,2 приоритетного шифратора 25. В заключение программно устанавливается внутренний триггер разрешения прерывания микропроцессора 1, поэтому на выходе

1,10 устанавливается логическая единица, и выполняется команда возврата к прерванной программе.

Если другое устройство установит на входах 35 логическую единицу,то процесс прерываний повторится аналогично, только B соответствии с Но вым кодом на выходах 25.1 приоритетного шифратора будет обслужено устройство, вызвавшее прерывание.

Если одновременно требуют обслуживания несколько устройств, то на выходе 25. приоритетного шифратора будет установлен код старшего по приоритету устройства (старшей единицы). По окончанию программы обслуживания этого устройства последовательно будут обслужены прерывания от младших по приоритету устройств.

Таким образом, обработка обычного прерывания, вызванного флажками внешних устройств, требующих обслуживания, в предлагаемом устройстве ана.логична известной дисциплине прерываний в системах програамного управления.

Прерывание с Формированием автоматных отображений (логическое прерывание).

Если одновременно с поступлением запросов на входы 35 (до перехода выхода 1.10 в состояние логического йуля, или в отсутствие таковых изменится информация на входах 34 логических условий, то на выходе схемы 24 сравнения установится логическая

4575

55 единица по синхроимпульсу выхода 1,8

I микропроцессора 1. Так как триггер 19 предварительно установлен (при инициализации) и прерывания разрешены, то по импульсу на выходе 1.8 микро" процессора 1 активируется выход weмента И 18, устанавливающий через элемент ИЛИ 15 триггер 21 по синхроимпульсу выхода 2.4 (синхроимпульс выхода 1.8 перекрывает выход 2.4) °

Если триггер 21 уже установлен - чуть раньше поступил сигнал с выхода 25.2 приоритетного шифратора 25, но еще не обнулился выход 1.10 микропроцессора 1, то состояние триггера 21, сформировавшего уже з