Многовходовое последовательное суммирующее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычисли-' тельной технике и может быть использовано при построении последовательных умножителей двоичных кодов. Цель изобретения - сокращение количества оборудования» ycTpofictBO содержит

СООЗ СОВЕТСНИХ

ССЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (! 9) (11) (5)) С 06 Г y/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

Н ASTOPCHOMY СВИД.:ТЕЛЬСТВУ (21) 4821214/24 (22) 09.04.90, ,(46) 23.02.92. Ьюл. 1(7 ,(72) И.И.Татур, С.П.Яцкевич, Н.В.Фурашов и Л.Ь.Авгуль

l(53) 681.325..5(088.8)

;(56) Самофалов К.Г. и др. Цифровые .ЭВИ, -. Киев: Вища школа, 1989,с.251. . Nellado И.,Cachего А.M. Alique I.R.

Summadores de entrada multiple.

Апа1ев de fisica. Real Sociedad

Бврайо1а de fisica g quimica, 1972, то1., 66, Nums. 1, 49-59, fig. 5.

2 (54) ИНОГОВХОДОВОЕ ПОСЛЕДОВАТЕЛЬНОЕ

СУММИРУЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычисли- тельной технике и может быть исполь" зовано при построении последовательHblx умножителей двоичных кодов. Цель изобретения - сокращение количества оборудования, Устройство содержит ,(2n-1)-входовой одноразрядный сумма тор 6, содержаций трехвходовые одно разрядные сумматоры 2, образующие дерево сумматоров (n — число входов 1 устройства), и (и-1)-разрядный буферный регистр 3. Выход суммы сумматора

6 соединен с выходом 5 устройства, а выходы переноса — с входами регистра 3. 1 ил.

1714589

Изобретение относится к вычислительной технике и может быть использовано при построении последовательных умножителей двоичных кодов.

Известен многовходовой сумматор последовательного действия, содержащий дерево полных сумматоров, каждый из которых двумя входами соединен с выходами сумм предыдущего каскада, а третий с выходом триггера запоминания переноса. Недостатком устройства является большая глубина схемы, что снижает быстродействие .

Наиболее близким к изобретению является многовходовое последовательное суммирующее устройство, содержащее (2п-1)-Входовый одноразрядный

СумндТОр (и ЧИСЛО ВХОДОВ уСтрОЙСТ ва) и (n-1) -разрядный буферный регистр, причем Входы устройства и выходы (n-1)-разрядного буферного ре-

Гистра соединены с Входами (2n 1)-ВХО-, дового сумматора. Недостаткок - сложность устройсlBd, 25

Цель изобретения - сокращение количе=тва оборудования, Поставленная цель достигается тем, что многовходовое последовательное суммирующее устройство, содержащее п входов, (2n-1)-входовый одноразрядный сумматор и (n-1)-разрядным буферный регистр содержит в одноразрядном сумматоре íà (2n-1) Вход два комбинационных дерева сумматоров, причем

35 и входов устройства соединены с п входами сумматоров первого дерева, выход первого дерева является выходом устройства, входы Второго дерева сое40 динены с и-1 Выходами триггеров регистра„ а выход соединен с одним из входов сумматора старшего ранга первого дерева, все выходы переносов

n"1 сумматоров соединены с входами триггеров буферного регистра запоминания переносов.

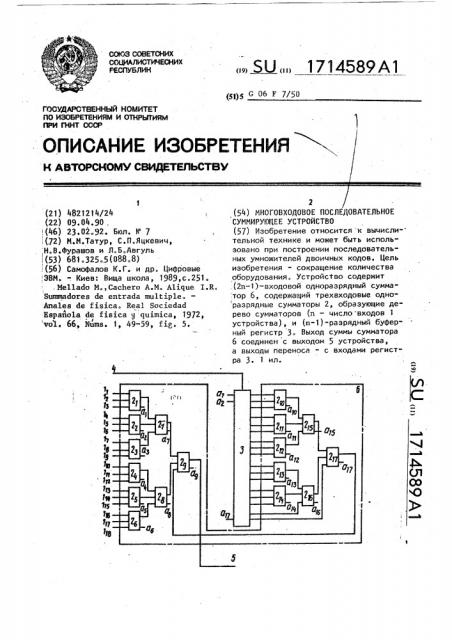

На чертеже показана функциональная схема многовходового сумматора последовательного действия для п=18.

Устройство содержит входы li (i

1,18), трехвходовые одноразрядные сумматоры 21 (j = 1,17), разрядный буферный регистр 3, вход 4 управления записью в регистр, выход 5 уст55 ройства. Сумматоры 2j образуют 35-входовый одноразрядный сумматор 6.

Устройство работает следующим обра эом.

На входы li подаются 18 чисел последовательным кодом. С выходов переносов сумматора 21-2 сигналы переносов записываются в девять разрядов регистра 3. На следующем такте число переносов суммируется по модулю "2" и результат складывается на сумматоре 2 . При этом с выходов переносов сумматора 2,0-21т сигналы переносов записываются в регистр 3. С выхода 5 снимается очередная цифра результата суммирования. формула изобретения

Иноговходовое последовательное суммирующее устройство, содержащее (2n-1)-Входовый одноразрядный сумматор (п - число входов устройства) и (n-1)-разрядный буферный регистр, причем входы устройства и выходы (n-1)-разрядного буферного регистра соединены с входами (2n-1)-входового одноразрядного сумматора, выход суммы которого соединен с выходом устройства, а выходы переноса с первого по (п-I)-й соединены с соответствующими

Входами (n-1)"разрядного буферного регистра, отличающееся тем, что, с целью сокращения количества оборудования, (2n-1)-входовый одноразрядный сумматор содержит трехвходовые одноразрядные сумматоры, образующие дерево сумматоров, причем входы трехвходовых одноразрядных сумматоров первой строки дерева сумматоров соединены со входами (2n-1)входового одноразрядного сумматора, входы трехвходовых одноразрядных сумматоров каждой следующей строки дерева сумматоров соединены с выходами суммы трехвходовых одноразрядных сумматоров предыдущей строки дерева сумматоров, выход суммы трехвходового одноразрядного сумматора последней строки дерева сумматоров соединен с выходом суммы (2п-1)-входового одноразрядного сумматора, выходы пе- реноса которого соединены с выхода-, ми всех трехвходовых одноразрядных сумматоров дерева сумматоров.