Цифровое устройство для управления инвертором

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике. Целью мзобретенйя язля1бтся повы1дение надежности. Высокочастотные импульсы с задающего генератора 1 поступают на входы элементов И 9.10, на другие входы которых поступаюУ сигналы череэ элементы ,И-НЕ 8. ИСКЛЮЧАЮЩЕЕ ИЛИ 7и распределитель 2 с низкочастотного выхода задающего генератора 1. На выходе элемента И 9 формируется сигнал, поступающий на суммирующий вход реверсивного счетчика импульсов 11, а на выходе элемента И 10 - сигнал, поступающий на вычитающий вход реверсивного счетчика импульсов 11vвыпoлняющий роль формирователя треугольного напряжения. Число А с выходов счетчика 11 поступает на одни входы блока 12 сравнения кодов, на другие входы которого поступает число В с аналого-цифрового преобразователя 3. В момент времени, когда число А разно числу В и равно нулю, на вход расширения блока 12 поступает сигнал логической единицы. На его выходе формируется кратковременно сигнал логической единицы, и триггеры 15, 16 продолжают переключаться. Таким образом устройство нормально функционирует при нулевых Значениях входной величины. 2 ил..СОс©i^a?4^ VI VI Ы>& ГО

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

{61) 1647812 (21) 4661479/07 (22) 13.03;88 (46) 23,02.92. Бюл. М 7 (71) Научно-исследовательский институт автоматики и электромеханики при Томском институте автоматизированных систем уп.. равления и радиоэлектроники (72) А. Я. Лысенко и Г. И, Цветков (63} 621,316.727(088.8) (56) Авторское свидетельство СССР

М 1647812, кл. Н 02 М 7/48, 1988, (54) ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ УП. РАВЛЕНИЯ ИНВЕРТОРОМ (57) Изобретение относится к электротехнике. Целью изобретения является повышение надежности. Высокочастотные . импульсы с задающего генератора 1 поступают на входы элементов И 9, 10, на другие входы которых поступаюг сигналы через элементы И-НЕ 8, ИСКЛЮЧАЮЩЕЕ ИЛИ 7

„„53J„„1714773 А2 (s1)s Н 02 М 77//4488, Н 02 Н 7/122 и распределитель 2 с низкочастотного выхода задающего генератора 1. На выходе элемента И 9 формируется сигнал, поступающий на суммирующий вход реверсивного счетчика импульсов 11, а на выходе элемента И 10 — сигнал. поступающий иа вычитающий вход реверсивного счетчика импульсов 11, выполняющий роль формирователя треугольного напряжения. Число А с выходов счетчика 11 поступает на одни sxoды блока 12 сравнения кодов, на другие входы которого поступает число В с аналого-цифрового преобразователя 3. В момент времени, когда число А разно числу В и равно нулю, на вход расширения блока 12 поступает сигнал логической единицы. На

его выходе формируется кратковременно сигнал логической единицы, и триггеры 15, 16 продолжают переключаться, Таким образом устройство нормально функционирует при нулевых значениях входной величины.

2 ил.

1714773

Изобретение относится к электротехнике, может быть использовано для управления однофаз ными и многофазными инверторами и является усовершенствованием устройства по авт. св. М 1647812. 5

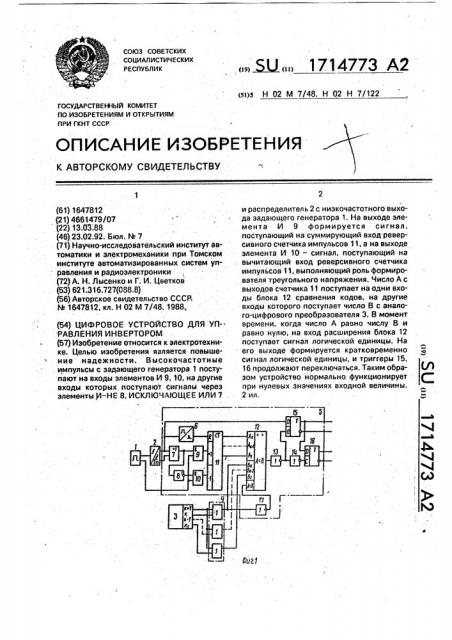

Целью изобретения является повышение надежности, На фиг. 1 представлена функциональная схема устройства (изображен только один канал управления); на фиг, 2 — времен- 10 ные. диаграммы, поясняющие его работу.

Устройство содержит задающий генератор 1 с встроенным делителем частоты, распределитель 2, аналого-цифровой преобразователь 3, элементы ИЛИ 4, один ка- 15 нал 5 управления. Канал 5 управления содержит. формирователь 6 коротких импульсов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, элемент НЕ 8, элементы И S и 10, реверсивный счетчик 11, блок 12 сравнения кодов, 20 элементы НЕ 13 и 14, два D-триггера 15 и 16 и элемент НЕ 17.

Низкочастотный выход задающего генератора 1 подключен к входу распределителя, высокочастотный выход — к одному из 25 входов элементов И 9 и 10. Другой вход элемента И 10 соединен с выходом элемента HE 8, вход которого соединен с другим входом элемента И 9 и йодключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7. Входы 30 этого элемента подключены к первому и второму выходам распределителя 2. Выходы элементов И 9 и 10 подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика 11, вход ус- 35 тановки которого соединен с выходом формирователя 6, Выходы. реверсивного счетчика 11 подключены к одним входам блока 12, другие входы которого подключеньгк выходам элементов ИЛИ 4. Одни входы 40 элементов ИЛИ 4 объединены и подключены к выходу старшего (K+1j-разряда аналого-цифрового преобразователя 3, остальные К разрядов которого подключены к другим входам элементов ИЛИ 4 соответ- 45 ственно. Тактовый вход первого триггера 16

- подключен к выходу элемента НЕ 14, а управляющий вход соединен с прямым выходом триггера 15, тактовый вход которого соединен с входом элемента HE 14 и через 50 элемент HE 13 подключен к выходу блока

12, Управляющий вход триггера 15 соеди-, нен с входом формирователя 6, с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и с первым выходом распределителя 2, Вход 55 элемента НЕ 17 подключен к выходу той схемы элементов ИЛИ 4, один из входов которой подключен к выходу К-разряда аналого-цифрового преобразователя 3, так как на выходе К-разряда код наиболее ствбилен. Выход элемента НЕ 17 соединен с входом расширения блока 12, Также принципиально возможно подключение входа элемента НЕ 17 к одному из выходов реверсивного счетчика 11 импульсов.

На фиг. 2 показаны: 18 — сигнал на высокочастотном выходе задающего генера-. тора 1; 19, 20- сигналы на первом и втором выходах распределителя 2; 21 — сигнал на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7;

22 — сигнал на выходе элемента НЕ 8; 23, 24 — импульсы на суммирующем и вычитающем входах реверсивного счетчика 11; 25 — сигнал на выходе формирователя 6; 26 — код А на выходах реверсивного счетчика 11; 27— код В на выходах элементов ИЛИ 4; 28— сигнал на выходе блока 12; 29 — сигнал на выходе элемента НЕ 13, 30 — сигнал на прямом выходе триггера 15; 31 — сигнал на прямом выходе триггера 16; 32 — выходное напряжение однофазного инвертора.

Задающий генератор 1 содержит последовательнс соединенные собственно задающий генератор и делитель частоты.

Распределитель 2 импульсов представляет собой счетчик Джонсона.

Устройство работает следующим образом, Высокочастотные импульсы 18 поступают на одни входы элементов И 9 и .10, Импульсы с частотой в 2п раза выше выходной частоты инвертора поступают на вход распределителя 2. На первом выходе распреде- лителя 2 формируется сигнал 19, на втором его выходе — сигнал 20, сдвинутый относительно сигнала 19 на 90О.Частота сигналов

19 и 20 равна выходной частоте инвертора.

Сигналы 19 и 20 поступают на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7, на выходе которого формируется сигнал 21, который поступает на один из входов элемента И 9 и на вход элемента НЕ 8, на выходе которого формируется сигнал 22, который поступает иа один из входов элемента И 10. На выходе элемента И 9 формируется сигнал 23, который поступает на суммирующий вход реверсивного счетчика 11 импульсов, и на выходе элемента И 10 формируются импульсы 24. которые поступают на вычитающий вход счетчика 11. В результате число А на выходах счетчика 11 возрастает в первой половине и уменьо аетсМ во второй половине каждого полупериода синхронизирующего сигнала 19, т.е. реверсивный счетчик 11 в данном случае выполняет роль формирователя треугольного напряжения 27. На вход установки счетчика 11 поступает сигнал 25 с выхода формирователя 6 коротких импуль- . сов, который сбрасывает счетчик 11 в конце каждого полупериода, тем самым начало ра5 1714773 6

< боты счетчика 11 жестко привязывается к чит, что на выходе блока 12 сравнения кодов нчл ачалу каждого полупериода что повышает буДет постоянно сигнал, соответствующий

1 надежность работы устройства путем иск- уровнюлогического нуля, итриггеры 15и 6 лючения сбоев, возникших в предыдущем не переключаются, что, в свою очередь, выполупериоде. Число А (сигнал 26) с выходов 5 зывает аварию в инверторе. В момент вресчетчика 11 по тупает на одни входы блока мени и. когда число А равно числу В и равна

12 сравнения кодов, на другие входы кото- нулю, на вход расширения блока 12 посту рогоп ого поступает число В (сигнал 27) с знало- пает сигнал логической единицы, а это энаго-цифрового преобразователя 3, На чит, что на его выходе формируется выходе блока 12 сравнения кодов сигнал 10 кратковременно сигнал логической едини- логической единицы существует тогда и цы,итриггеры15и16продолжаютпереклютолько тогда, когда число А меньше числа чаться. Таким образом, предлагаемое

В(А В) во всех других случаях сигнал на его устройство нормально функционирует при выходе соответствует уровню логического нулевых значениях входной величины. нуля. В нормальном режиме (фиг, 2, интер- 15 Для управления m-фазным инвертором вал времени ц), когда число А станет больае необходимо иметь п-каналов, подобных каВ, на выходе блока 12 сравнения кодов фор- налу 5 управления. Распределитель должен мируется сигнал 28 логического нуля, кото- иметь четное количество входов 2п. Сдвиг

ый инвертируется элементом HE 13 и по фазе между выходными сигналами двух поступает(сигнал 29) натактовый входтриг- 20 соседних выходов в таком распределителе гера 15. По фронту сигнала 29 переключает- равен 180/2п эл,град: В общем случае входы ся триггер 15, на прямом выходе которого любого канала управления подключаются к формируется сигнал 30. Сигнал 29 инверти- 1-му и j-му выходам распределителя, причем . р ется элементом НЕ 14 и поступает на так- j=l+n, так как именно эта пара выходов фор. руется л м товый вход триггера 16, который 25 мирует две однофазные последовательнопереключается по. срезу сигнала 29 и фор- сти импульсов, сдвинутые одна мирует на прямом выходе сигнал 31. При относительно другой на 90О. изменении числа В до максимально возможного первая последовательность управ- Формула изобретения ляющих импульсов 30 сдвигается 30 Цифровоеустройстводляуправленияинотносительно синхронизирующего сигнала вертором.по авт. св, М 1647812, о т л и ч а ю19 а угол а в сторону отставания, а вторая щ е е с я тем, что, с целью повышения надежн последовательность управляющих импуль- . ности, в каждый канал управления введе сов 31 - на тот же самый угол в сторону четвертый элемент НЕ, а блок сравнения

35 кодов снабжен дополнительным входом, НЕ иПусть в момент времени tg код В умень- причем вход четвертого элемента НЕ соедшается до нуля. Тогда в известной схеме не нен с выходом одного из элементов ИЛИ, а существует ни одного момента времени, выход — с дополнительным входом блока когда выполняется условие А В, а это зна- сравнения кодов. I

1714773

Составитель О.Г.Мещеряковэ

Техред М.Моргентал Корректор В.Гирняк

Редактор С.Пекарь

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Заказ 702 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5