Генератор логико-динамического теста

Иллюстрации

Показать всеРеферат

Генератор логико-динамического текста относится к цифровым генераторам логических последовательностей. Цель изобретения - повышение диагностических способностей теста. Генератор логико-динамическогй теста содержит генератор 1 полного логического теста, элемент ИЛИ 7, две линии задержки 5,6 на один такт, N линий задержки 2.1-2.N на два такта и N эле- :ментов ИСКЛЮЧАЮЩЕЕ ИЛИ 3.1-3.N, входящие -в состав N узлов 4.1-.N формирования разрядов выхода. Поставленная цель достигается за счет введения элемента ИЛИ, линий задержки, на один такт, N узлов формирования разряда выхода, 1 ил., 1 табл. S (Л

СОЮЗ СОВЕТСКИХ

AUW%0

- РЕСПУБЛИК.(,1)5 с 06 F l/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОЬЙГ СВИДЕТЕЛЬС ГВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

IlO ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ CGCP

1 (21) 4784397/24 (22) 19.01 ° 90 (46) 29 02.92. Бюл. и 8 (71) Московский институт электронной техники (72) Д.О.Левицкий и В.М.Кривошапко (53) 681.325(088.8) (56) Авторское свидетельство СССР

N 1138799, кл., G 06 F 1/02, 1984:

Гутников В.С. Интегральная электроника в измерительных устройствах.

Л.: Энергоатомиздат, Ленинградское отделение, 1988, с. 161-168. (54) ГЕНЕРАТОР ЛОГИКО-ДИНАМИЧЕСКОГО

ТЕСТА

Ф

Изобретение относится к генераторам цифровых последовательностей и может быть использовано в блоках контроля (как встроенных, так и внеш" них) для создания полного логико-. динамического теста.

Целью изобретения является повы1 шение диагностических способностей теста.

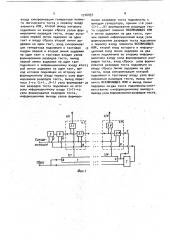

На фиг. 1 представлена схема генератора логико-динамического теста; на фиг. 2 - таблица, поясняющая ра- боту устройства для 0=3.

Устройство содержит генератор 1: полного логического теста, линии за-:держки 2. 1,...,2Л на два такта со входом сброса и тактовым входом в совокупности с элементами ИСКЛЮЧАЮ-

ЩЕЕ ИЛИ 3.1-3.N входящие в узлы. „,SU„„>716497 А1

2 (7) Генератор логико-динамического текста относится к цифровым генераторам логических последовательностей.

Цель изобретения — повышение диагностических способностей теста ° Генератор логико-динамического теста содержит генератор l полного логического теста, элемент ИЛИ 7, две линии за" держки 5, 6 на один такт, N линий задержки 2.1-2.N на два такта и и эле ментов ИСКЛЮЧАЮЦЕЕ ИЛИ 3.1 3.N, вхо- . дящие в состав N узлов. 4.1-4.Б формирования разрядов выхода. Поставленная цель достигается за счет введения элемента ИЛИ, линий задержки, на один такт, N узлов формирования разряда Я выхода. 1 ил., 1 табл.

4.1,...,4.N формирования разрядов теста, линию задержки 5 на один такт, линию задержки 6 на один такт, имеющую вход сброса и тактовый вход, элемент ИЛИ 7, тактовый вход "Синхронизация", вход "Сброс".

Генератор работает следующим образом.

Вход "Сброс" на первом (установочном) такте устанавливается в "1" (это приводит к тому, что все устройство устанавливается в исходное состояние). При этом, поскольку

"Сброс" подключен ко входу D генера-,Ъ тора l полного логического теста, то генератор 1 устанавливается в исходное состояние, и на- его вьixopax появляется первый логический тест, а поскольку "Сброс" подключен ко входу

17)6497 элемента ИЛИ 7, а элемент ИЛИ 7 подключен ко входам сброса линий задержки 2.1-2.N на два такта и входу сброса второй линии задержки 5 на один такт, все эти линии задержки сбрасываются в "0". Кроме того выход элемента ИЛИ 7 подключен ко входу установки первой линии задержки 6, которая устанавливается в "1". На всех последующих тактах (рабочих так" тах) вход "Сброс" должен быть установлен в "0".

На вход "Синхронизация" постоянно подается импульсный сигнал, задающий тактовую частоту работы устройства.

Этот сигнал поступает на тактовые входы всех линий задержки на два такта 2.1,...,2.N, а также на тактовый вход первой линии задержки 5 на один 0 такт,и на тактовый вход второй линии задержки 6 на один такт. Таким образом, тактовая частота обеспечи. вает непрерывное продвижение информации от первой линии задержки 5 на 25 один такт до выхода последней N-й линии задержки.2.N на два такта.

Переключение генератора 1 полного логического теста 1 на очередной тест происходит только при выработке сигнала "Переключить генератор" (появление единицы на выходе S), одновременно этот сигнал через элемент ИЛИ

7 вызывает сброс линий задержки

2.1-2.N на два такта и второй линии задержки 6 на один такт в нулевое состояние, а первая линия задержки 5 на один такт устанавливается в "1".

° Сигнал "Переключить генератор" появляется только тогда, когда "1", записанная в линии 5, пройдет через .вторую линию задержки 6 на один такт и через все линии задержки 2.1-2. N на два такта всех разрядов. Продвижение этой "1" обеспечивается тактовыми „5 импульсами, подаваемыми через вход

"Синхронизация".

При отсутствии "1" в каком-либо

:разряде соответствующий разряд генератора полного логического теста передается на выход без изменений. При появлении Чн на входе линии задержки

2.п (на входе очередного разряда n) и на входе элемента, ИСКЛЮЧАЮЩЕЕ ИЛИ

3,п на соответствующий выход А/и по55 ступает инвертированный сигнал соответствующего разряда i/n генератора полного логического теста. На следующем такте "1" уходит вглубь линии задержки $.n, на входе элемента ИСКЛЮЧАЮЦ ЕЕ ИЛИ З.п восстанавливается

"0" и, следовательно, соответствующий сигнал 1/п генератора полного логического теста поступает на выход А/и, снова не инвертированный. На следующем такте указанная "1" появляется уже на выходе линии задержки 2.п текущего разряда, т.е. на входе следующего разряда n+i. Линии задержки

5 и 6 на один такт обеспечивают начальную установку и выдачу сначала неизмененного логического теста на выходы устройства.

Для доказательства правильности функционирования нужно показать, что функция устройства совпадает с определением полного логико-динамического теста. По определению, полный логикодинамический тест должен содержать все переключения во всех возможных логических состояниях. Перебор всех возможных логических состояний обеспечивается генератором полного логического теста. Поскольку в одном и том же логическом состоянии генератора 1, т.е. между двумя сигналами

"Переключение генератора", все разряды данного логического теста поочередно меняют свое значение на инверсное и возвращаются обратно, то получается, что предлагаемое устройство производит полный перебор всех возможных переключений в каждом логическом состоянии, т.е. предлагаемое устройство полностью удовлетворя-„ ет определению полного логико-динамического теста.

Формула и з о б р е т е н и я

Генератор логико-динамического теста, содержащий генератор полного логического теста, причем вход сброса генератора подключен ко входу генератора полного логического теста, отличающийся тем, что, с целью повышения диагностических способностей тес а, в него введены элемент ИЛИ, две линии задержки на один такт, Й узлов формирования разрядов теста, причем выходы генератора полного логического теста подключены к первым .информационным входам соответствующих узлов формирования разрядов теста, выход переноса N-го (где N— число разрядов генератора) узла формирования разрядов теста подключен ко

1716497

° ° 0

° ° °

° ° ° входу синхронизации .генератора полного логического теста,и первому входу элемента ИЛИ, второй выход которого подключен ко входам сброса узлов фор5 мирования разрядов теста, входу установки первой линии задержки на один такт и входу сброса второй линии задержки на один такт, вход синхронизации генератора подключен к тактовым ip входам первой и второй линий задержки на один такт и тактовым входам узлов формирования разрядов теста, выход первой линии задержки на .один такт подключен к информационному входу вт035 рой линии задержки на один такт, вЫ- ход которой подключен ко второму ин-, формационному еходу первого узла формирования разрядов теста, выход переноса i-ro (i=i...N-1) узла формирова- 20 ния разрядов теста подключен ко второму информационному входу (i+1)-ro узла формирования разрядов теста, .информационные выходы узлов формирования разрядов теста подключены к выходам генератора, причем i-й узел (i=>...È) формирования разрядов теста содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и линию задержки на два такта, причем первый информационный вход узла формирования разрядов теста подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, второй вход которого и информационный вход линии задержки на два такта подключены ко второму информа-: ционному входу узла формирования раз рядов теста, вход сброса узла форми- рования разрядов теста подключен ко входу сброса линии задержки на два такта, вход синхронизации которой подключен к тактовому входу узла формирования разрядов теста, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выход линии задержки на два такта подключены соответственно кинформационному выходу И выходу узла формирования разрядов теста.