Устройство для ввода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано дл я, сбора и экспресс-обработки информации от аналоговых и цифровых датчиков . Цель изобретения -- повышение надежности устройства. Устройство позволяет вводить и обрабатывать информацию от аналоговых и цифровых датчиков. Блок сбора и обработки данных, входящий в состав устройства, выполняет побайтный анализ входной информации; например экстремальный , статистический или отсев сбойной информации. Зил.

(19) (11) СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (sl)s G 06 F 3/05, 3/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И. ОТКРЫТИЯМ

ПРИ .ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ: СВИДЕТЕлbCTSY

1 (2 1 ) 43.75984/24 (22) 05;01,88 (46) 29;02.92. Бюл. М.8

Р2) В.М.Панов, О.H.Ëèííèêîâ; Б.А.Юфряков.

8.И.Суворов, .Н.П,Катомин, А.Н.Андрюхин, 8.À.Øëûê. С;Н.Косарев и А;А.Федорушков: (53) 681.327.2 (088.8) (56) Авторское свидетельство СССР

М 1310796, кл, G 06 F 3/05, 1985.

Авторское. свидетельство СССР

1к 1298734, кл. G 06,F 3/05, 1985. (54) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМА. ЦИИ

Изобретение относится к автоматике:и вычислительной. технике и может быть. :.использовано для сбора:и экспресс-обработки информации от айалоговых.и цифровых датчиков, Целью изобретения является повйеение надежности устройства.

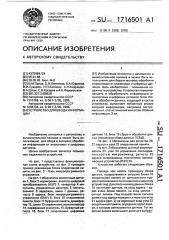

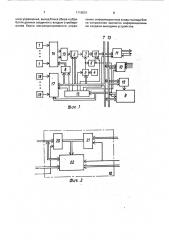

На фиг. 1. представлена. функциональная схема устройства; на фиг. 2 приведен пример реализации блока оперативной: памяти; на фиг. 3 — блок микропрограммного управления.

На фиг. 1 обозначены аналоговые датчики 1..блок 2 нормировки, аналого-цифровой преобразователь (АЦП) 3, генератор 4. импульсов, управляемый делитель 5 частоты; элемент 6 задержки. шина 7 данных, регистр. 8 адреса, блок микропрограммного управления. (БМУ) 9, блок 10 оперативной памяти. блок 11 буферной памяти, деаифрвтор 12,.шина 13 управления, мультиплекмр

14, парафазный усилитель 15, буферный регистр 16; блок 17 сопряжения, цифровые

2 (57) Изобретение относится к автоматике и вычислительной технике -и может быть использовано для.сбора и экспресс-обработки информации от аналоговых и цифровых дат- чиков. Цель изобретения — .повышение надежности устройства. Устройство позволяет вводить и обрабатывать информацию от аналоговых и цифровых датчиков. Блок сбора и обработки данных, входящий в состав устройства; .выполняет побайтный анализ входной информации, например экстремальный, статистический или отсев сбойной информации. 3 ил. датчики 18, блок 19 сбора и обработки данных (процессор сбора данных ПСБД).

На фиг, 2 обозначены два регистра 20, 21 адреса и узел.22 оперативной памяти.

На фиг. 3 обозначены шинный формирователь 23, узел 24 управления .последовательностью микрокоманд, регистр 25 адреса микрокоманд, постоянное запоминающее устройство (ПЗУ) 26.

Устройство работает следующим образом, .

Прежде чем начать процедуру сбора данных, осуществляется загрузка блока 10 оперативной памяти от центрального процессора (внешнего по отношению к данному устройству); Для этого на входданных блока

10 поступают. данные; на вход. адреса — адрес ячеек блока памяти, на вход записи— сигнал записи. Под воздействием сигнала записи код адреса передается через регистр

21 адреса (фиг, 2) на адресный вход узла 22 оперативной памяти, определяя адрес ячейки, в которую записываются данные. Тот же сигнал записи записывает данные в выбран1716501 ную ячейку. Регистр 21 с тремя состояниями на выходе отключается от адресного входа узла>22 в отсутствие сигнала записи. В качестве блока 10 оперативной памяти может быть использовано постоянное запоминающее устройство (ПЗУ), тогда операция начальной загрузки отсутствует, Информация блока 10 определяет порядок опроса каналов, режим подавления синфазных помех, тип опрашиваемого канала(аналоговый или цифровой), частоту дискретизации АЦП 3, режим работы блока 2 нормировки. Порядок работы устройства определяется программной работы БМУ 9. Эта программа зашита в ПЗУ 26 (фиг. 3) и содержит инструкции для работы блоков устройства. В начальный момент регистр -25 адреса микрокоманд сбрасывается в ноль, указы, вая на нулевую ячейку памяти блока 26, С нулев; о адреса ПЗУ 26 располагается программа, по которой процессор.19 сбора данных опрашивает определенную ячейку блока 10 и. анализирует один из ее битов.

Если бит установлен, что говорит о завершении процедуры начальной загрузки, то процессор 19 формирует на выходе нулевого результата сигнал, получив который, узел 24 изменит. содержимое регистра 25. Таким образом, как только блок 10 памяти заполнен, блок 9 микропрограммного управления переходит на другую программу работы— программу сбора и экспресс-обработки. В качестве узла 24 может быть использована микросхема К1804ВУ4, а блока 19

К1804В С1.

Поясним работу. устройства по программе сбора и экспресс-обработки. Работа начинается с чтения константы из блока 10 оперативной памяти, Для этого БМУ 9 выставляет на шину 13 управления адрес блока 10, который дешифрируется дешифратором 12. Дешифратор 12 формирует импульс записи, поступающий в блок 10 оперативной памяти. Кроме этого, БМУ 9 выставляет для процессора 19 команду записи, по котораи содержимое одного из его внутренних регистров, в котором хранится адрес текущей ячейки блока 10, выдается на шину данных. Содержимое регистра поступает по шине данных на вход регистра 20 адреса и записывается в него- по фронту импульса записи. С выхода регистра 20 адоес подается на адреснь1й вход узла 22 оперативной памяти. На следующем шаге БМУ

9 выставляет на шину 13 команду чтения для блока 19 и сигнал чтения для блока 10. Блок

10 оперативной памяти выставляет на шину данных содер>кимов ячейки, адрес которой записан в регистр 20, а блок 19 читает эти данные с tu«÷û 7 данных. После этого блок один из блоков 2, 5, 8 или 17, определяя режим его работы. Цикл, начинаюЩийся чтением константы из блока 1О оперативной памяти, заканчивается после того, как реги20 стры всех вышеназванных блоков будут загружены, Константа, записанная в регистр блока 2 нормировки, согласует динамический диапазон сигнала на входе блока 2 (амплитуда и смещение относительно нуля) с динамическим диапазоном АЦП 3, а в регистр делителя 5 — однозначно определяет временной интервал между предыдущим и последующим интервалами запуска АЦП 3, в регистр 8 — номер подключенного аналогового канала или номера двух каналов в ре>киме подавления синфазных помех, в регистр блока 17 сопряжения — номер подклю30 ченного цифрового канала. Если частота

35 дискретизации сигналов всех датчиков 1 одинакова-, то загрузить регистр управляемого делителя 5 частоты следует всего один раз перед началом работы. То же самое относится к блокам 2, 8 или 17. если соответственно одинаков динамический диапазон сигналов всех опрашиваемых аналоговых

40 датчиков, подключается лишь один аналоговый канал, один цифровой. канал, Сигнал от датчика, подключенного к выбранному в данный момент каналу, преобразованный в блоке 2 нормировки, поступает на вход АЦП 3. С приходом импульса запуска с выхода управляемого делителя 5 частоты на выходе АЦП 3 появляется

50 цифровой код, пропорциональный напряжению сигнала на входе. Импульс запуска, задержанный элементом 6задержки на время преобразования АЦП, записывает этот код в буферный регистр 16 (например, 1533

ИР 33), одновременно импульс,с выхода элемента 6 задержки поступает на БМУ 9, оповещая о готовности данных;

Под управлением БМУ 9 процессор 10 считывает по шине 7 данных цифровой код из буферного регистра 16. Если программа

19 под управлением БМУ 9 начинает анализировать принятые данные. Данные содержат информацию о том, какой из элементов

2, 5„8, 17 программируется. О завершении

5 анализа блок 19 сообщает БМУ 9 по.выходу нулевого результата. После этого БМУ 9 выставляет на вход дешифратора 12 адрес одного из блоков 2, 5, 8 или 17 и команду записи для блока 19, по которой процессор

10 сбора данных выставляет на шину 7 константу (в простейшем случае ту же, что и считана из блока 10 оперативной памяти), В зависимости от того, какой блок дешифрирован, на одном из выходов дешифратора

15 12 появляется строб-импульс, по фронту которого код с шины данных будет записан в

1716501 работы БМУ 9 не предусматривает никаких действий над данными, то под управлением блока 9 процессор 19 записывает этот код в блок 11 буферной памяти. При этом на выходе блока 11 буферной памяти появляется сигнал готовности, оповещающий внешний процессор о том, что в устройстве появились данные для считывания.

Режим работы с цифровыми каналами

10 так же задается информацией, записанной в блоке 10 оперативной памяти. При этом нет необходимости записывать коды управления в регистр 8, блоки 2 и 5. Следует лищь запрограммировать работу блока 17 сопряжения. Для этого блок 9 выставляет на шину

1.5

13 управления адрес этого блока и команду записи для процессора 19. После дешифра- ции импульсом записи с выхода дешифратора 12 данные выставления процессором 19

20 будут записаны в блок 17, определяя режим его работы. Если устройство осуществляет сбор данных только. от одного датчика цифровой информации, то программирование блока 17 осуществляется только один раз перед началом работы. В качестве блока 17: 25 может быть использована микросхема

5809855, которая обладает качеством двунаправленной передачи данных, Таким образом, имеется воэможность адаптивного управления теми процессами.и устройства-. ми, к которым подключены аналоговые и цифровые датчики. Для этого часть цифровых датчиков следует заменить приемниками цифровой информации (в простейШем

35 случае цифроаналоговыми преобразователями). Схема адаптивного управления выглядит следующим образом: сбор данных от аналоговых и цифровых датчиков, контроль параметров входной информации, которая пропускается через процессор 19, и, в слу- 40 чае необходимости, выдача команд или уггравляющих кодов внешним исполнительным элементами устройства, подключенным вместо некоторых цифровых датчиков.

Применение процессора t9 для побайтного анализа входной информации.(экстремальный анализ, отсев сбойной информации, статистический анализ) повышает надежность устройства, сочетание в одном усрасширяет возможную область его применения.

Формула изобретения

Устройство для ввода информации, содержащее мультиплексор, блок нормировки, аналого-цифровой преобразователь; блоки буферной и оперативной памяти, блок микропрограммного управления, дешифратор, управляемый делитель частоты, генератор импульсов. элемент задержки и тройстве аналоговых и цифровых каналов 50 регистр адреса. выходы которого соединены с адресными входами мультиплексора, информационные входы которого являются информационными аналоговыми входами устройства, выход блока нормировки соединен с информационным входом аналогоцифрового преобразователя, выход генератора импульсов соединен с тактовым входом управляемого делителя частоты, выход которого соединен с входом запуска аналого-цифрового преобразователя и входом элемента задержки, первый, второй и третий выходы дешифратора соединены cooTB6TGTB8HHo "со стробирующими входами регистра адреса, блока нормировки и управляемого делителя частоты, входы установки регистра адреса, блока нормировки и управляемого делителя частоты обьединены двунаправленной шиной данных с информационными входами-выходами блока микропрограммного управления и блока оперативной памяти, информационные выходы, вход чтения и выход готовности блока буферной памяти являются соответственно информационными выходами, входом чтения и выходом готовности устройства, информационные входы, адресные входы первой группы и вход записи блока оперативной памяти-явля, ются соответственно информационными входами, адресными входами и входом записи устройства, о т л ич а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит блок сопряжения, парафазный усилитель, буферный регистр и блок сбора и обработки данных, .адресные входы которого через двунаправленную шину управления объединены с адресными входами второй группы блока оперативной памяти, адресными входами блока сопряжения, входами дешифратора и управляющими входами блока микропрограммного управления, выходы аналого-цифрового преобразователя соединены е информационными входами буферного регистра, выходы которого через двунаправленную шину данных соединены с информационными входами блока буферной памяти, информационными входамивыходами блока сбора и обработки данных, информационными входами-выходами блока сопряжения, первый и второй выходы мультиплексора соединены с входами парафазного усилителя, выход которого соединен с информационным входом блока нормировки, четвертый, пятый, шестой и седьмой выходы дешифратора соединены соответственно с входами стробирования блока сопряжения, буферного регистра, входом записи блока буферной памяти и входом готовности блока микропрограмм1716501 ного управления, выход блока сбора и обра- ления, информационные входы-выходы блоботки данных соединен с входом стробиро- ка сопряжения являются информационныванйя блока микропрограммного управ- ми входами-выходами устройства.

1716501

Составитель 8.Файзразманов

Редактор Т.Лошкарева Техред М;Моргентал Корректор Т. Малец

Заказ 613 Тираж Подписное

8НИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород. ул,Гагарина, 101