Устройство для контроля сдвига фаз двух сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении контрольно-измерительной аппаратуры и для контроля сдвига фаз между двумя гармоническими сигналами. Отличительной особенностью устройства является то, что оно позволяет сократить время контроля за счет одновременного измерения периода входного сигнала в счетчике 15 и времени сдвига фаз в счетчике. Целью изобретения является сокращение времени контроля. Поставленная цель достигается за счет введения компаратора, коммутаторов , счетчиков, элемента ИЛИ. 4 ил.

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (54)5 G 06 F 11/16

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4675633/24 (22) 11.04.89 (46) 29.02.92. Бюл. гв 8 (72) В.Е. Николаенко; В.H. Пуцков, Н.H. Новиков и Ю.А, Романенко (53) 681.3(088.8) (56) Авторское свидетельство СССР

N -1415198, кл. G 01 В 25/10, 1987.

Авторское свидетельство СССР

N 1325487, кл. 6 06 F 11/26, 1985. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СДВИГА ФАЗ ДВУХ СИГНАЛОВ

Изобретение относится к вычислительной технике и может быть использовано при построении контрольно-измерительной аппаратуры для измерения сдвига фаз между двумя гармоническими сигналами.

Целью изобретения является сокращение времени контроля.

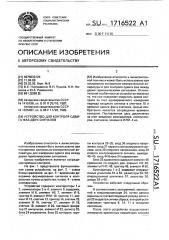

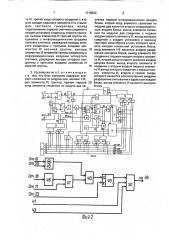

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 — схема блока сравнения; на фиг. 3 — временная диаграмма формирования сигналов в контрольных точках устройства; на фиг. 4 — схема компаратора.

Устройство содержит компараторы 1 и

2, коммутаторы 3 и 4, элемент 5 задержки, элемент И 6, элемент НЕ 7, элемент И 8, триггер 9, элемент ИЛИ 10, триггер 11, элемент И 12, счетчик 13, триггер 14, счетчик 15, элемент И 16, счетчик 17, элемент И 18, счетчик 19, элемент И 20, тактовый генератор 21 импульсов, элемент И 22, регистр 23, блок 24 управления. блок 25 контроля, груп,, Я2„„1716522 А1 (57) Изобретение относится к вычислительной технике и может быть использовано при построении контрольно-измерительной аппаратуры и для контроля сдвига фаз между двумя гармоническими сигналами. Отличительной особенностью устройства является то, что оно позволяет сократить время кон.троля за счет одновременного измерения периода входного сигнала в счетчике 15 и времени сдвига фаэ в счетчике. Целью изобретения является сокращение времени контроля. Поставленная цель достигается эа счет введения компаратора, коммутаторов, счетчиков, элемента ИЛИ. 4 ил. пы контроля 26-35, вход 36 опорного напряжения, вход 37 первого контролируемого сигнала, вход 38 опорного напряжения, вход 39 второго контролируемого сигнала, выходы

40-43, вход 44 блока 24 управления.

Блок 25 сравнения содержит элемент 45 сравнения по модулю два, элемент HE 46, элементы И 47, 48, триггер 49, элемент И 50. . Компараторы 1 и 2 содержат операционные усилители 51 и 52; резисторы 53-56,. операционный усилитель 57, резистор 58, диоды 59 и 60.

Устройство работает следующим образом.

В соответствии с программой, записанной в микропроцессоре 24. путем записи единицы в соответствующий разряд регистра 23 выдается сигнал сброса, который устанавливает триггеры 9, 14, 11 в исходное состояние.

После этого устройство осуществляет измерение временных параметров сигнала

1716522

50

55 контроля, образующегося при поступлении входного сигнала на входы измерителя.

Измерение осуществляется следующим образом.

Блок 24 производит запись: в счетчик 13 импульсов обратного кода, соответствующего количеству периодов сигналов контроля, эа которое осуществляется измерение времени периодов в счетчике 15 импульсов, времени длительности импульса в счетчике

17, времени длительности паузы в счетчике

19, Измерение времени за N периодов производится с целью увеличения измеряемого временного интервала.

Затем блок 24 путем записи в счетчики

15, 17, 19 нулевого кода производит их обнуление. После этого микропроцессор записывает единицу в соответствующий разряд регистра 23, тем самым обеспечивается выдача команды "Пуск". По этой команде триг.гер 9 перебрасывается в единичное состояние. Его выходной сигнал обеспечивает прохождение контролируемого сигнала через элемент И 12 в счетчик 13 импульсов и на триггер 11.

При поступлении контролируемого сигнала триггер 11 перебрасывается в единичное состояние. Его выходной сигнал обеспечивает прохождение импульсов опорной частоты с генератора 21; в счетчик

15 импульсов через элемент И 16 для измерения времени периода контролируемого сигнала; в счетчик 17 импульсов через элемент И 18 для измерения времени контролируемого сигнала; в счетчик 19 импульсов через элемент И 20 для измерения паузы контролируемого сигнала.

По прохождении периодов контролируемого сигнала счетчик 13 выдает импульс переполнения. Он поступает на вход установки в единицу триггера 14, устанавливая

его в единичное состояние. 8ыходной сигнал с триггера 14 свидетельствует об окончании измерения.

Этот выходной сигнал поступает íà установочный вход триггера 9 и через элемент

ИЛИ 10 на установочный вход триггера 11, приводя их в исходное состояние. Прекращается прохождение импульсов с генератора 21 в счетчики 15; 17, 19 и контролируемого сигнала в счетчик 13.

Одновременно блок 24 управления считывает сигнал "Конец измерения" с выхода триггера t4 через элемент И 22. При наличии сигнала "Конец измерения" блок 24 производит считывание информации, записанной в счетчиках 15, 17, 19 импульсов, После этого блок 24 осуществляет контроль наличия сбоев в работе счетчиков 15, 17, 19 импульсов путем проверки соотношения

Мста= 4ст,+Л1ст„, (1) где Мст — количество импульсов. соответствующее времени N периодов контролируемого сигнала, записанное в счетчике 15 импульсов;

N T — количество импульсов, соответствующее времени N импульсов контролируемого сигнала, записанное в счетчике 17 импульсов; йст„- количество импульсов, соответствующее времени пауз контролируемого сигнала, записанное в счетчике 19 импульсов.

При невыполнении соотношения (1) блок 24 производит повторные измерения и контроль этого соотношения. При повторном невыполнении соотношения (1) микропроцессор 26 прекращает процесс измерения и выдает информацию на блок 29 индикации о наличии неисправности.

При выполнении соотношения (1) блок

24 осуществляет контроль функционирования устройства путем контроля величины времени задержки (тзадержки) сигнала элементом 5 задержки.

Контроль осуществляется проверкой микропроцессором 26 соотношения тмин доп — тзадержки — Смакс дол (2) где 1задержки — измеряемое время задержки, которое будет определяться количеством импульсов, записанных в счетчике 17 импульсов; тмии доо минимально допустимое время задержки; тмакс дол — максимально допустимое вре-, мя задержки, Максимальное и минимальное значения времени задержки устанавливаются исходя из допустимой величины времени задержки контролируемых сигналов, вносимых входными элементами устройства, включая и элемент 5 задержки.

При невыполнении соотношения (2) дальнейшие измерения прекращаются, Блок 25 контроля (фиг. 2) контролирует значение выходных функций на выходе элементов И 16 и 20 в тот момент времени, когда триггер 11 находится в единичном состоянии, а с выхода элемента И 18 снимается сигнал, эквивалентный логическому нулю. Если в этот момент времени сигналы на выходе элементов И 16, 20 будут противоположны, триггер 49 устанавливается в единичное состояние.

Блок 24 управления может быть выполнен на микропроцессоре К580ИК80.

Формула изобретения

1. Устройство для контроля сдвига фаз двух сигналов, содержащее два компарато1716522 ра, первый коммутатор, элемент задержки, семь элементов И, десять групп элементов

И, элемент НЕ, три триггера, два счетчика, тактовый генератор, регистр и блок управления, причем первый вход первого компаратора соединен с первым информационным входом первого коммутатора и является входом первого контролируемого сигнала, выход равенства компаратора соединен с первым входом первого элемента И, выход равенства второго компаратора соединен с входом элемента задержки, выход которого соединен с вторым входом первого элемента И, выход которого соединен с первым входом второго элемента И, с входом элемента НЕ, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с первым выходом регистра,.второй выход которого соединен с первым входом сброса в ноль первого триггера, с входом сброса в ноль второго триггера, выход которого соединен с вторым входом сброса в ноль первого триггера, с первым входом четвертого элемента И, выход которого соединен с первым входом группы входов блока управления, первый выход которого соединен с первыми входами элементов И первой, второй, третьей, четвертой и пятой групп, второй выход блока управления соединен с первыми входами элементов И шестой, седьмой, восьмой, девятой и десятой групп и с вторым входом четвертого элемента И, выходы с первого по десятый первой группы выходов блока управления соединены с вторыми входами элементов И групп соответственно с первой по десятую, одиннадцатый выход первой группы выходов блока управления соединен с третьим входом четвертого элемента

И, вторая группа выходов блока управления соединена с входами элементов И первой, второй, третьей, четвертой и пятой групп, выходы элементов И шестой, седьмой, восьмой. девятой и десятой групп соединены с группами входов соответственно первой, второй, третьей, четвертой и пятой группы входов блока управления, выходы элементов И первой группы соединены с информационными входами первого счетчика, разрядные выходы которого соединены с третьими входами элементов И шестой группы, выходы элементов И второй группы соединены с информационнми входами второго счетчика, разрядные выходы которого соединены с третьими входами элементов И седьмой группы, выходы элементов И пятой группы соединены с информационными входами регистра, группа выходов которого соединена с группой входов элементов И десятой группы, выход.тактового генерато45 дом четвертого счетчика и с вторым информационным входом блока контроля, выход

:третьего элемента И соединен с входом установки в единицу первого триггера, выход которого соединен с синхровходом третьего

50 триггера, выход которого соединен с вторым входом пятого элемента И, с первым входом шестого элемента И и с первым входом седьмого элемента И, выход элемента

ИЛИ соединен с входом сброса в ноль треть55 его триггера, второй выход регистра соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго триггера, выход первого элемента И соединен с входом установки в единицу третьего . триггера и с вторым входом шестого элемен30

55 ра соединен с первым входом пятого элемента И, выход первого триггера соединен с вторым входом второго элемента И, выход которого соединен со счетным входом первого счетчика, синхровход первого триггера соединен с шиной единичного потенциала устройства,отличающееся тем,что,c целью сокращения времени контроля, в устройство введен элемент ИЛИ, второй коммутатор, третий и четвертый счетчики и блок контроля, причем вход запуска блока сравнения соединен с выходом третьего триггера, вход начальной установки блока контроля соединен с вторым выходом регистра, вход разрешения контроля блока контроля соединен с выходом шестого элемента И и со счетным входом третьего счетчика, первый информационный вход задания блока контроля соединен с выходом седьмого элемента И и. со счетным входом второго счетчика, вход разрешения считывания блока контроля соединен с первыми входами элементов И шестой группы, второй вход девятой группы блока управления соединен с адресным входом блока контроля, выход блока контроля соединен с вторым входом группы входов блока управления, второй информационный вход первого коммутатора является входом второго контролируемого сигнала устройства, первый информационный вход второго коммутатора соединен с вторым входом первоro компаратора и является первым входом опорного напряжения устройства, второй информационный вход второго коммутатора соединен с вторым входом опорного напряжения устройства, третий выход регистра соединен с управляющими входами первого и второго коммутаторов, выходы первого и второго коммутаторов соединены соответственно с первым и вторым входами второго компаратора, выход элемента НЕ соединен с вторым входом пятого элемента

И, выход которого соединен со счетным вхо1716522 та И, третий вход которого соединен с вторым входом седьмого элемента И и с выходом тактового генератора, выход переполнения первого счетчика соединен с входом установки в единицу второго триггера, выходы элементов И третьей группы соединены с информационными входами третьего счетчика, разрядные выходы которого соединены с третьими входами элементов И восьмой группы, выходы элементов И четвертой группы соединены с информационными входами четвертого счетчика, разрядные выходы которого соединены с третьими входами элементов И девятой группы.

2. Устройство по п.1, о т л и ч à ю щ е ес я тем, что блок контроля содержит элемент сложения по модулю два, элемент НЕ, два элемента И, триггер, причем первый вход элемента сложения по модуля два является первым информационным входом блока, второй вход элемента сложения по модулю два является вторым информационным входом блока, выход элемента сложе5 ния по модулю два соединен с первым входом первого элемента И, выход которого соединен с входом установки в единицу триггера, вход сброса в ноль KoTopGIQ является входом начальной установки блока, 10 вход элемента HE является входом разрешения контроля блока, выход элемента HE соединен с первым входом второго элемента И, второй вход которого является входом запуска блока, выход второго элемента И

15 соединен с вторым входом первого элемента И,выход которого соединен с первым входом элемента И, второй и третий входы которого являются соответственно входами разрешения считывания и адресным входом

20 блока, выход элемента И является выходом блока.

1716522 л ла

Составитель H,Òîðoïîàà

Техред М.Моргентал Корректор М.Пожо

Редактор С.Лисина

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 614 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35; Раушская наб„4/5