Вычислительное устройство с совмещением операций

Иллюстрации

Показать всеРеферат

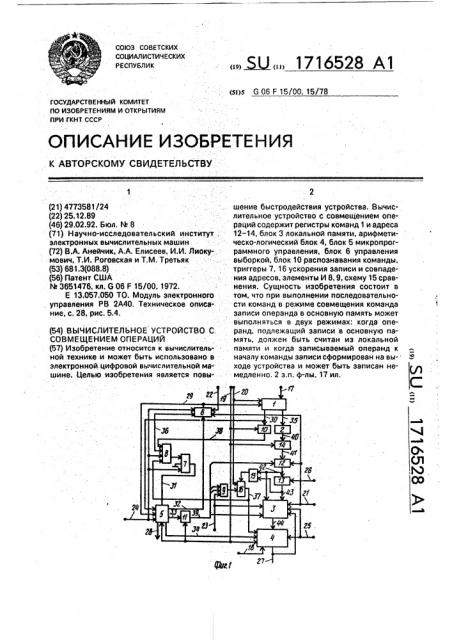

Изобретение относится к вычислительной технике и может быть использовано в электронной цифровой вычислительной машине . Целью изобретения является повышение быстродействия устройства. Вычислительное устройство с совмещением операций содержит регистры команд 1 и адреса 12-14, блок 3 локальной памяти, арифметическо-логический блок 4, блок 5 микропрограммного управления, блок 6 управления выборкой, блок 10 распознавания команды, триггеры 7,16 ускорения записи и совпадения адресов, элементы И 8,9, схему 15 сравнения . Сущность изобретения состоит в том, что при выполнении последовательности команд в режиме совмещения команда записи операнда в основную память может выполняться в двух режимах: когда операнд , подлежащий записи в основную память , должен быть считан из локальной памяти и когда записываемый операнд к началу команды записи сформирован на выходе устройства и может быть записан немедленно . 2 з.п. ф-лы, 17 ил. (Л С о ел ю 00 Фиг.1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)ю G 06 F 15/00, 15/78

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ. СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ . К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4773581/24 (22) 25.12.89 (46) 29.02.92. Бюл. N- 8 (71) Научно-исследовательский институт .. электронных вычислительных машин (72) В.А. Анейчик, А.А. Елисеев, И.И. Лиокумович. Т.И. Роговская и Т.М. Третьяк (53) 681.3(088.8) (56) Патент США

N 3651476, кл. 6 06 F 15/00, 1972.

Е 13.057.050 ТО. Модуль электронного управления PB 2A40. Техническое описа-. ние, с. 28, рис. 5.4. (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С.

СОВМЕЩЕНИЕМ ОПЕРАЦИЙ (57) Изобретение относится к вычислительной.технике и может быть использовано в электронной цифровой вычислительной машине. Целью изобретения является повы„„5LI„„1716528 А1 шение быстродействия устройства. Вычислительное устройство с совмещением операций содержит регистры команд 1 и адреса

12-14, блок 3 локальной памяти, арифметическо-логический блок.4, блок 5 микропрограммного управления, блок 6 управления выборкой, блок 10 распознавания команды, триггеры 7, 16 ускорения записи и совпадения адресов, элементы И 8, 9, схему 15 сравнения. Сущность изобретения состоит в том, что при выполнении последовательности команд в режиме совмещения команда записи операнда в основную память может выполняться в двух режимах: когда операнд, подлежащий записи в основную память, должен быть считан из локальной памяти и когда записываемый операнд к началу команды записи сформирован на выходе устройства и может быть записан немедленно. 2 з.п. ф-лы, 17 ил.

1716528 памяти, блок арифметическо-логический, 35

Изобретение относится к вычислительной технике и может быть использовано в электронной цифровой вычислительной машине.

Известно вычислительное устройство с совмещением операций, содержащее блок локальной памяти.

В известном устройстве при совмещенной обработке команд обнаружение конфликта по обращению к регистрам общего назначения ЕС ЭВМ вызывает.выход иэ режима совмещения, что приводит к потерям времени. Недостатком известного устройства является низкая производительность.

Известно также вычислительное устройство с совмещением операций, содержащее регистр команды, блок дешифрации команд. В известном устройстве выполняется сравнение адреса операнда, считываемого командой считывания, с адресом операнда, записываемого предыдущей командой записи. Это позволяет обеспечить разрешение конфликта по считывания операнда, причем предотвращается использование операнда, запись которого предыдущей командой еще не завершилась.

Недостатком известного устройства является низкое быстродействие при выполнении команды записи, т.к. не обеспечивается возможность доступа к операнду, подлежащему записи.

Известно также вычислительное устройство с совмещением операций, содержащее регистр команды, блок локальной блок микропрограммного управления. В известном устройстве предусмотрена воэможность приема в блок арифметическологического результата выполнения предыдущей команды из блока локальной памяти или с выхода блока арифметическологического, что позволяет ускорить выборку операнда.

Недостатком известного устройства является низкое быстродействие при выполнении команды записи, Наиболее близким к предлагаемому устройству по технической сущности является вычислительное устройство с совмещением операций, содержащее регистр команды, блок дешифрации команд, блок управления выборкой, блок локальной памяти, блок а рифметическо-логический, блок микропрограммного управления. В известном устройстве обеспечивается убыстрение доступа к операнду, если перед командой, считывающей этот операнд из блока локальной памяти, выполняется команда, записывающая этот же операнд в блок локальной

30 памяти, т.е. обеспечивается доступ к операнду, минуя блок локальной памяти.

Недостатком известного устройства является низкое быстродействие при выполнении записи операнда.

Целью изобретения является повышение быстродействия.

Сущность изобретения состоит в том, что при выполнении устройством последовательности команд в режиме совмещения команда записи операнда в основную память может выполняться в двух режимах: в обычном, когда операнд, подлежащий записи в основную память, должен быть предварительно считан из блока локальной памяти, и в ускоренном, когда записываемый операнд к началу команды записи сформирован на выходе данных устройства и может быть немедленно записан в основную память, Введение в устройство блока микропрограммного управления позволяет обеспечить два адреса ветвления для микропрограмм команд записи в основную память: один адрес для микропрограммы, выполняемой в обычном режиме и содержащей полную последовательность микрокоманд, другой адрес — для короткой, более быстрой микропрограммы, выполняемой в ускоренном режиме. Кроме того, введение в устройство блока микропрограммного управления позволяет обеспечить аппаратурную выработку сигналов микроопераций для микропрограммы команды записи. выполняемой в ускоренном режиме.

Введение в устройство блока распознавания команды позволяет определить начало выполнения устройством команды, производящей запиСь в основную память.

Введение в устройство трех адресных регистров, регистра микроопераций, схемы сравнения, второго элемента И и триггера совпадения адресов позволяет обнаружить ситуацию, когда равны адреса записи и считывания информации для блока локальной памяти, т.е. когда информация, подлежащая считыванию из блока локальной памяти, имеется на выходе данных устройства.

Введение в устройство первого элемента И и триггера ускорения записи позволяет обнаружить ситуацию, когда перед командой записи в основную память некоторого операнда выполняется команда. формирующая этот операнд и.записывающая его по тому же адресу в блок локальной памяти, из которого его должна извлечь команда записи в основную память.

Таким образом, введение в устройство новых блоков позволяет обеспечить ускорение выполнения команды записи в основную память, когда записываемый операнд

1716528 формируется командой, предшествующей этой команде записи.

На фиг. 1 представлена структурная блок-схема вычислительного устройства. с совмещением операций; на фиг. 2 — схема блока формирования адреса; на фиг. 3— схема блока локальной памяти;на фиг, 4схема арифметическо-логического блока; на фиг. 5 — схема блока микропрограммного управления; на фиг. 6 — схема блока управления выборкой; на фиг, 7 — схема блока распознавания команды; на фиг. 8 — диаграмма блока микрокоманды; на фиг. 9 —. блок-схема микропрограммы выполнения команды L; на фиг. 10 — блок-схема микропрограммы выполнения команды LE; на фиг. 11 — блок-схема микропрограммы выполнения команды ST; на фиг. 12 — блок-схема микропрограммы выполнения команды

STE; на фиг. 13- блок-схема последовательности микрокоманд, выполняемой при обработке последовательности команд L(0), ST(2) или LE(0), STE(2); на фиг, 14- бло -схема последовательности микрокоманд, выполняемой при обработке последовательности команд ЦО), ST(0) или LE(0), STE(0): на фиг; 15 — временная диаграмма работы вычислительного устройства при обработке последовательности команд L(0), ST(2) или LE(0),.

STE(2); на фиг. 16 — временная диаграмма работы вычислительного устройства nðè обработке последовательности команд L(0) или $Т(О), LE(0), STE(0); на фиг, 17 — временная диаграмма работы блока локальной па-. мяти при выполнении последовательности иэ трех микрокоманд с адресами 350, 058(078), 050(070), выполняемой при отработке следующих последовательностей команд: L(0), ST(2); LE(0), STE(2), L(0), ST(0), LE(0), STE(0).

На фиг. 1-7 обозначены: регистр 1 команд, блок 2 формирования адреса, блок 3 локальной памяти, арифметическо-логический блок 4, блок 5 микропрограммного управления, блок 6 управления выборкой, триггер 7 ускорения записи. элементы И 8, 9, блок 10 распознавания команды, регистр

11 микроопераций, первый-третий адресные регистры 12-14, схема 15 сравнения, триггер 16 совпадения адресов, вход 17 команд устройства, вход 18 операндов устройства, первый-восьмой синхровходы 19:26 устройства, выход 27 данных устройства, выход 28 записи устройства, первый выход

29 блока управления выборкой, второй выход 30 регистра команд, выход 31 триггера ускорения записи, первый-третий выходы

32-34 микроопераций блока микропрограммногоуправления, первый выход 35 регистра команд, второй выход 36 блока

30 дов регистра и соединен с входом блока 2

50. формирования адреса. Второй выход 30 регистра 1 команд формируется из 1- 8 разря55

55

45 управления выборкой, выход 37 триггера совпадения адресов, выход 38 блока распознавания команд, выход 39 регистра микроопераций, выход 40 блока формирования адреса, выход 41 третьего адресного регистра, выход 42 первого адресного регистра, выход 43 второго адресного регистра, выход 44 данных блока локальной памяти, элемент НЕ 45, элемент

ИЛИ-НЕ 46, регистр 47, триггер 48, коммутатар 49, элемент И 50, накопитель 51 локальной памяти, регистры 52-56, коммутатор 57, арифметическо-логические элементы 58 — 60, коммутатор 61, регистры

62, 63, память 64 микропрограмм, элементы

ИЛИ 65-67, элементы И-НЕ 68, 69, триггеры

70, 71, элементы НЕ 72 — 76, элементы И 77, 78, триггер 79, Регистр 1 команды предназначен для приема в начале такта устройства информации, поступающей на его вход данных, при наличии единичного сигнала на его входе разрешения записи и хранения информации при нулевом сигнале на входе разрешения записи.

Для ЕС ЭВМ разрядность регистра 1 команды равна 12. Первый выход 35 регистра 1 команд формируется из 1,3,9-12 раэрядов регистра и соединен с входом блока 10 распознавания команд, в котором не используется 3 разряд выхода 30, и с адресным входом блока 5 микропрограммного управления.

Блок 2 формирования адреса предназначен для формирования адреса операнда в локальной памяти в такте поступления на

его вход командной информации. Выход 40 блока 2 формирования адреса соединен с входом третьего адресного регистра 14..

Данная реализация блока формирования адреса ориентирована на систему команд. EC ЭВМ. Для этой системы команд формирование адреса операнда, находящегося в локальной памяти, заключается в подмешивании к четырем разрядам номера регистра первого операнда одного разряда признака. Для команд с плавающей точкой (первая тетрада кода операции для этих команд равна 1, 3, 6 или 7 в шестнадцатеричной системе счисления) этот признак равен единице, для остальных команд — нулю. Таким образом формируется пятиразрядный адрес обращения к блоку 3 локальной памяти.

Блок 3 локальной памяти предназначен для хранения операндов команд устройства и выполняет операции считывания и записи

1716528 информации в зависимости от сигнала на входе записи. При наличии единичного сигнала на входе записи блок 3 локальной памяти выполняет запись информации, поступающей на вход данных, При нулевом сигнале на входе записи блок 3 локальной памяти выполняет чтение информации, s результате которого на выходе блока 3 локальной памяти формируется результат считывания. В качестве адреса для блока 3 локальной памяти при единичном значении сигнала на входе управления режимом используется информация с входа адреса записи, при нулевом значении сигнала на входе управления режимом блока 3 локальной памяти используется информация с входа адреса считывания.

Выход 44 данных блока 3 локальной памяти соединен с первым входом данных арифметическо-логического блока 4.

Арифметическо-логический блок 4 вредназначен для приема операндов, поданных на первый и второй входы данных в начале такта. устройства, и их арифметической и логической обработки в соответствии с сигналами, поданными на вход 34 операции арифметическо-логического блока 4. Результаты обработки формируются на выходе 27 блока 4 в начале следующего такта устройства. В случае, когда на входе 37 выбора блока 4 присутствует "1", в качестве первого операнда используется результат работы блока 4 в предыдущем такте устройства. В случае, когда на входе выбора блока

4 присутствует "О", в качестве первого операнда используется информация, имеющаяся на первом входе данных блока 4. Выход

27 блока 4 соединен с входом данных блока

3 локальной памяти и с выходом данных устройства.

Блок 5 микропрограммного управления предназначен для хранения микропрограмм, управляющих работой устройства; выбора адреса микрокоманды. подлежащей выполнению, и хранения кода микрокоманды s течение такта выполненияданной микрокоманды.

По сигналу на первом входе 29 кода условия блока .5 микропрограммного управления в качестве адреса следующей микракоманды используется информация на адресном входе блока 5 микропрограммного управления (при сигнале, равном единице) либо информация, сформированная самим блоком 5 микропрограммного управления(при сигнале, равном нулю). На выходах блока 5 микропрограммного управления формируется код микрокоманды, подлежащей выполнению, при этом на первый-третий выходы микроопераций выдаются микроопе10

30 динен с первым входом кода условия блока

40 5 микропрограммного управления и с входом разрешения записи регистра 1 команд.

55 рации, соответствующие данной микрокоманде. По единичному значению сигнала на втором входе 31 кода условия блока 5 микропрограммного управления формируются измененные код микрокоманды и код адреса следующей микрокоманды.

Формирование сигналов не изменяется при нулевом значении сигнала на входе 31.

Первый выход 34 микрооперации блока 5 микропрограммного управления соединен с входом кода операции арифметическо-логического блока 4, второй выход 32 микроопераций блока. 5 микропрограммного управления — с управляющим входом блока

6 управления выборкой, третий выход 33 микроопераций блока 5 микропрограммного управления соединен с входом регистра микроопераций. Выход 28 записи блока 5 микропрограммного. управления соединен с выходом записи устройства.

Блок 6 управления выборкой предназначен для выработки сигнала .на выполнение. следующей команды устройства.

Сигнал перехода на выполнение следующей команды. устройства возникает при поступлении единичного сигнала во втором разряде управляющего входа блока 6 управления выборкой и исчезает при поступлении единичного сигнала в первом разряде управляющего входа блока 6 управления выборкой.

Сигнал перехода на выполнение следующей команды формируется на первом выходе 29 блока 6 управления выборкой команды, на втором выходе 36 блока 6 управления выборкой в следующем такте устройства формируется задержанный сигнал переходе на выполнение следующей .команды, Первый выход 29 блока 6 управления выборкой соеВторой выход 36 блока 6 управления выборкой соединен с четвертым входом первого элемента И 8.

Первый элемент И 8 и триггер 7 yc«qpeния записи предназначены для формирования сигнала ускорения записи. Выход первого элемента И 8 соединен с входом установки триггера 7 ускорения записи. Выход 31 триггера 7 ускорения записи соединен с вторым входом кода условия блока 5 микропрограммного ускорения.

Блок 10 распознавания команд предназначен для формирования е начале такта. следующего за тактом поступления на его вход 30 командной информации, признака наличия на шинах его входа комбинации сигналов, соответствующей кодам операции команд. в которых осуществляется запись первого операнда в основную память

1716528

40

50

55 по адресу второго операнда. Выход 38 блока

10 распознавания команд соединен с вторым входом первого элемента И 8.

Регистр 11 микрооперации предназначен для запоминания микроопераций, поступающих на его информационный вход, на один такт. Выход 39.1 первого разряда регистра 11 микроопераций соединен с первым входом второго элемента И 9 и с входом записи первого адресного регистра 12. Выход 39.2 второго разряда регистра 11 микроопераций соединен с вторым входом второго элемента И 9 и с входом записи блока 3 локальной памяти.

Первый адресный регистр 12 предназначен для запоминания адреса, поступающего на информационный вход, на один такт устройства при наличии единичных сигналов на синхровходе и входе записи.: Выход 42 первого адресного регистра 12 соединен с информационным входом второго адресного регистра 13 и с входом адреса считывания блока 3 локальной памяти.

Второй и третий адресные регистры 13 и 14 предназначены для запоминания адресов, поступающих на информационные входы при наличии единичных сигналов на соответствующих синхровходах. Выход 43 второго адресного регистра 13 соединен с вторым входом схемы 15 сравнения и с входом адреса записи блока 3 локальной памяти. Выход 41 третьего адресного регистра 14 соединен с информационным входом перcoro адресного регистра 12.

Второй элемент И 9, схема 15 сравнения, триггер. 16 совпадения. адресов предназначены для формирования в середине такте выполнения микрокоманды с микрооперациями записи и считывания (единичные сигналы на первом и втором входах второго элемента И 9) при совпадении адресов записи и считывании, поступающих на первый и второй входы схемы 15 сравнения. единичного сигнала на выходе триггера 16 совпадения. Выход 37 триггера 16 cosnaдения соединен с первым входом первого элемента И 8 и с входом выбора арифметическо-логического блока 4. Выход второго элемента И 9 соединен с синхровходом триггера 16 совпадения.

Выход схемы 15 сравнения соединен с информационным входом триггера 16 совпадения.

Вход 17 команд устройства соединен с входом данных регистра. 1 команд, По входу

17 команд в устройство поступает информация обочередной команде, подлежащей выполнению, а именно код операции команды и адрес операнда, находящегося в локальной памяти.

Вход 18 операндов устройства соединен с вторым входом данных арифметическо-логического блока 4. По входу 18 операндов в устройство поступает второй операнд выполняемой команды.

Первый-синхровход 19 устройства соединен с синхровходами блока 5 микропрограммного управления, блока 10 распознавания команды, регистра 11 микроопераций, третьего адресного регистра

14 и блока 4.

Второй синхровход 20 устройства соединен с тактовым входом регистра 1 команд и с входом сброса триггера 16 совпадения.

Третий синхровход 21 устройства соединен с первым синхровходом блока 6 управления выборкой; с синхровходом первого адресного регистра 12 и с синхровходом блока 3 локальной памяти.

Четвертый синхровход 22 устройства соединен с вторым синхровходом блока 6 управления выборкой.

Пятый синхровход 23 устройства соединен с третьим входом второго элемента И 9 и с входом управления режимом блока 3 локальной памяти.

Шестой синхровход 24 устройства соединен с третьим синхровходом блока 6 управления выборкой, вторым синхровходом блока 5 микропрограммного управления, с синхровходом триггера 7 ускорения записи и третьим входом первого элемента И 8.

Седьмой синхровход 25 устройства соединен со стробирующим входом блока 3 локальной памяти и со стробирующим входом арифметическо-логического блока 4.

Восьмой синхровход 26 устройства соединен с синхровходом второго адресного регистра 13.

На схеме блока 2 формирования адреса (фиг.2) изображены элемент ИЛИ-НЕ 46 и элемент НЕ 45.

Первый разряд входа 35 блока соединен с первым входом элемента ИЛИ-НЕ 46, выход которого соединен с первым разрядом выхода 40 блока формирования адреса. Второй разряд входа 35 блока соединен с входом элемента НЕ 45, выход которого соединен с вторым входом элемента ИЛИ IE 46. С третьего по шестой. разряды входа

35 блока соединены с разрядами с второго по.пятый выхода 40 блока соответственно.

На схеме блока 3 локальной памяти (фиг. 3) изображены регистр 47, триггер 48, коммутатор 49, элемент И 50 и накопитель

51 локальной памяти. Вход 43 адреса записи блока соединен с информационным входом регистра 47, выход которого соединен с первым входом данных коммутатора 49, выход которого соединен с адресным входом

1716528 питель 51 локальной памяти из регистра 47). -55

На схеме арифметическо-логического блока 4 (фиг, 4}изображены регистры 52-56, коммутатор 57, арифметические элементы

58-60, На фиг. 4 арифметическо-логический элемент обозначен AL, его вход переноса накопителя 51 локальной памяти, выход которого соединен с выходом 44 блока локальной памяти, Вход 39 записи блока соединен с управляющим входом регистра 47 и с информационным входом триггера 48, выход которого соединен с вторым входом элемента И 50, выход которого соединен с входом управления обращением накопителя 51 локальной памяти, информационный вход которого соединен с входом 27 данных блока, Стробирующий вход 25 блока соединен с синхровходом триггера 48 и с синхровходом регистра 47. Синхровход 21 блока соединен с.первым входом элемента И 50. а вход 23 управления режимом соединен с управляющим входом коммутатора 49, второй вход данных которого соединен с входом 42 адреса считывания блока.

Пятиразрядный регистр 47 предназначен.для запоминания адреса обращения к накопителю 55 локальной памяти. Занесение информации в регистр 47 по информационному входу производится при наличии единичного сигнала на управляющем входе.

Накопитель 51 локальной памяти предназначен для хранения операндов команд устройства с фиксированной и плавающей точкой.. При наличии нулевого сигнала на входе управления обращением накопитель

51 локальной памяти работает в режиме считывания информации по адресу, присутствующему на адресном входе. При наличии единичного сигнала на входе управления обращением накопитель 51 локальной памяти работает в режиме записи информации по адресу, присутствующему íà его адресном входе, причем записи подлежит информация, имеющаяся на информационном входе накопителя. Накопитель 51 локальной памяти позволяет осуществлять в течение одного такта устройства одно обращение для считывания информации и одно обращение для записи.

Коммутатор 49 предназначен для выбора источника адреса обращения к накопителю 51 локальной памяти. При нулевом сигнале на управляющем входе коммутатора 49 он подключает на свой выход адрес с второго входа данных(адрес считывания накопителя 51 локальной памяти на входе 42 адреса считывания блока). При единичном сигнале на управляющем входе коммутатора 49 он подключает на свой выход адрес с первого входа данных (адрес записи в нэко5

СО, выход последовательного переноса С4, выход прохождения переноса Р, выходгенерации переноса G, разрядные входы первого операнда АО, А1, А2, АЗ, разрядные входы второго операнда ВО, В1, В2, В3, разрядные входы кода функции $0, $1, $2, $3, М, разрядные выходы результата РО, Г1, F2, F3.

Первый вход 44 данных блока соединен с первым входом данных коммутатора 57. выход которого соединен с входом данных регистра 53, разрядные шины выхода которого соединены с соответствующими разрядными входами первого операнда арифметическо-логических элементов 58-60, разрядные выходы результата которых соединены с соответствующими разрядными шинами входа данных регистра 55, выход которого соединен с вторым входом данных коммутатора 57 и с входом данных регистра 56, выход которого соединен с выходом 27 блока. Второй вход 18 данных блока соединен с входом данных регистра 54, разрядные шины выхода которого соединены с соответствующими разрядными входами второго операнда арифметическо-логических элементов 58-60, разрядные входы кода функции которых соединены с разрядными выходами с второго по шестой регистра 52, вход данных которого соединен с входом 34 кода операций блока. Первый разрядный выход регистра 52 соединен с входом переноса арифме гическо-логического элемента

58, выход последовательного переноса которого соединен с входом переноса арифметическо-логического элемента. 59, выход последовательного переноса которого соединен с входом переноса последующего арифметическо-логического элемента. Вход переноса арифметическо-логического элемента 60 соединен с выходом последовательноге переноса предыдущего эрифметическо-логического элемента.

Вход 37 выбора блока соединен с управляющим входом коммутатора 57. Синхровход

19 блока соединен с синхровходами регистров 52-56, Стробирующий вход 25 блока соединен с синхровходом регистра 55.

Разрядность регистра 52 — 6 битов, разрядность регистров 53-56 — 32 бита. При такой разрядности операндов требуется 8 арифметическо-логических элементов для их обработки. Коммутатор 57 предназначен для выбора источника данных, поступающих на вход данных регистра 53. При нулевом сигнале на управляющем входе коммутатора 57 он выдает на выход информацию, поступающую на его первый вход данных. При единичном сигнале на управляющем входе коммутатора 57 он выдает на

1716528

10 равляющем входе коммутатора 61 он выдает на выход информацию, поступающую на второй адресный вход. При единичном сигнале на управляющем входе коммутатора 61 он выдает на выход информацию, поступа15 ющую на первый адресный вход. Десятиразрядный регистр 62 предназначен для хранения адреса микрокоманды; Память 64 микропрограмм предназначена для хранения микропрограмм, управляющих работой

20 устройства. Каждой команде из набора команд, выполняемых устройством, соответствует определенная микропрограмма. В памяти 64 микропрограмм содержатся по крайней мере микропрограммы выполнения следующих команд из системы команд

ЕС ЭВМ (в скобках указано мнемоническое обозначение команды): загрузка (3 ), загрузка (короткие операнды) (Е), запись в память ($Т), 30 запись в память (короткие операнды) (STE).

Каждая микропрограмма состоит из одной или нескольких микрокоманд. Микрокоманды размещены в памяти 64 в

35 соответствии с их адресами., Если на входе памяти 64 задан код адреса некоторой микрокоманды, то на выходе памяти 64 формируется код этой микрокоманды.Каждая

40 микрокоманда состоит flo меньшей мере из

21 разряда. Шесть первых разрядов выхода памяти 64 составляют код функции арифметическо-логического блока 4 (может быть задан код любой функции из списка функций арифметическо-логических элементов 58, 45

59, 60). Существенными являются следующие: функция."Транзит первого операнда" с кодом 011111 и обозначением С-А и функция "Транзит второго операнда" с кодом

010101 и обозначением С-В

Седьмой разряд выхода памяти 64 микропрограмм задает микрооперацию "Считывание локальной памяти", обозначение которой ЧТЛП.

Восьмой разряд выхода памяти 64 мик-. 55 ропрограмм задает микрооперацию "Запись в локальную память", обозначение которой ЗПЛП.

Девятый разряд выхода памяти 64 микропрограмм задает микрооперацию "Завыход информацию, поступающую на его второй вход данных.

На схеме блока 5 микропрограммного управления (фиг. 5) изображены коммутатор

61, регистры 62, 63 и память 64 микропрог- 5 рамм, элементы ИЛИ 65-67. Коммутатор 61 предназначен для выбора источника информации, поступающей на вход данных регистра 62. При нулевом сигнале на уппрет выполнения следующей команды", обозначение которой ЗВСК.

Десятый разряд выхода памяти 64 микропрограмм задает микрооперацию "Разрешение выполнения следующей команды", обозначение которой РВСК.

Одиннадцатый разряд выхода памяти

64 микропрограмм задает микрооперацию

"Запись в основную память", обозначение которой ЗПОП.

Разряды с двенадцатого по двадцать первый выхода памяти 64 микропрограмм составляют сдрес следующей микрокоманды, подлежащей выполнению.

Двадцатиразрядный регистр 63 предназначен для хранения в течение одного такта процессора кода выполняемой в этом такте микрокоманды, Не подлежит запоминанию в регистре 63 микрооперация ЗВСК, используемая в конце такта процессора, предшествующего такту выполнения данной микрокоманды.

Адресный вход 30 блока соединен с разрядными входами с 3-ro по 10-й первого входа данных коммутатора 61, разрядные входы которого 1-й и 2-й соединены с шиной нулевого потенциала (" Земля" ), а первый вход 29 кода условия блока соединен с управляющим входом коммутатора 61, выход которого соединен с информационным входом регистра 62, выход которого соединен с входом 64 памяти микропрограмм, разряды с 1-ro по 8-й и с 10-го по 21-й выхода которой соединены с разрядами с 1-го по 20-й информационного входа регистра 63. Девятый разряд выхода 64 памяти микропрограмм соединен с первым разрядом второго выхода 32 микроопераций блока. Разряды с 1-го по 6-й выхода регистра 63 соединены с раз рядами с 1-го по 6-й первого выхода 34 микроопераций блока. 7-й и 8-й разряды выхода регистра 63 соединены с 1-м и 2-м разрядом третьего выхода 33 микроопераций. Девятый разряд выхода регистра 63 соединен с первым входом элемента ИЛИ 65, выход которого соединен с вторым разрядом второго выхода 32 микроопераций блока. Десятый разряд выхода регистра 63 соединен с первым входом элемента ИЛИ 66, выход которого соединен с выходом 28 записи блока. 11-й и с 13-ro по 20- и разряды выхода регистра 63 соединены соответственно с 1м и с 3-го по 10-й разрядными входами второго входа данных коммутатора 61.

Двенадцатый разряд выхода регистра 63 соединен с первым входом элемента ИЛИ 6?, выход которого соединен с вторым разрядным входом второго входа данных коммутатора 61. Второй вход кода условия 31 блока соединен с вторыми входами элементов

1716528

ИЛИ 65, 66, 67. Первый синхровход 19 блока соединен с синхровходом регистра 62. Второй синхровход 21 блока соединен с синхровходом регистра 63.

На схеме блока 6 управления выборкой (фиг. 6) изображены элементы И-НЕ 68, 69 и триггеры 70, 71. Первый разряд управляющего входа 32 блока соединен с входом элемента И-НЕ 68, выход которого соединен с входом установки триггера 70, инверсный выход которого соединен с информационным входом триггера 71 и с первым выходом

29 блока. Второй разряд управляющего входа 32 блока соединен с входом элемента

И-НЕ 69, выход которого соединен с входом сброса триггера 70. Третий синхровход 24 блока соединен с входом элемента И-HE 68.

Второй синхровход 22 блока соединен с входом элемента И-НЕ 69, Первый синхровход

21 блока соединен с входом элемента И-НЕ

69 и с синхровходом триггера 71, выход которого соединен с вторым выходом 36 блока.

На схеме блока.10 распознавания команды (фиг. 7) изображены элементы НЕ

72-76, элементы И 77, 78 и триггер 79. flepвый разряд информационного входа 30 блока соединен с входом элемента НЕ 76, выход которого соединен с входом элемента

И 78, выход которого соединен с входом элемента И 77, выход которого соединен с информационным входом (О) триггера 79, выход которого соединен с выходом 38 Gnoка.Второй и третий разряды информационного входа 30 блока соединены с входами элемента И 78. С 4-го по 7-й разряды информационного входа 30 блока соединены соответственно с входами элементов НЕ 72, 73, 74, 75. выходы которых соединены с входами элемента И 77. Синхровход 19 блока соединен с синхровходом (С) триггера 79.

Блок 10 распознавания команды формирует признак наличия íà его входе кода операции команд записи в основную память

ST и STE, коды операции которых 50 и 70 соответственно (в шестнадцатеричной системе счисления).

На диаграмме блока микрокоманды (фиг. 8) изображено распределение записей символических обозначений микроопераций в последовательных строках каждого блока.

В первой строке располагается обозначение функции арифметическо-логического блока. Вторая строка: в начале строки располагается обозначение микрооперации

"Считывание локальной памяти", в конце— обозначение микрооперации "Запись в локальную память". Третья строка: в начале строки располагается обозначение микро10

55 операции "Запрет выполнения следующей команды", в конце — микрооперации "Разрешение выполнения следующей команды".

Четвертая строка: в начале строки располагается обозначение микрооперации "3aпись в основную память", в конце строки располагается адрес следующей микрокоманды (ККК). Над блоком микрокоманды справа записывается адрес микрокоманды (MNN). Обозначение каждой микрооперации отличается от обозначения любой другой микрооперации, поэтому для упрощения на блок-схемах микропрограмм (фиг. 9-14) номера строк в блоках микрокоманд не проставляются.

Работа вычислительного устройства заключается в выполнении последовательности команд. Каждая команда состоит из кода операции, указывающего, какая операция должна выполняться, и кода, задающего операнды. Имеются два класса операндов: регистровые операнды и операнды в основной памяти. Каждая команда использует два операнда, причем первый операнд всегда находится в локальной памяти(регистровый операнд), а второй операнд может находиться также и в основной памяти. Адрес операнда в локальной памяти непосредственно указывается номером регистра. В определенном поле команды адрес операнда

s основной памяти формируется путем определенных действия над полями команды, отведенными для задания адреса.

8а адрес операнда в основной памяти накладывается следующее ограничение: он должен быть кратен количеству байтов в операнде (для 32-разрядных операндов, например. адрес должен быть кратен четырем). Разрядность операндов должна быть равна разрядности вычислительного устройства (для 32-разрядного вычислител ьного устройства операнды могут быть только

32-разрядными).

Команды. выполняемые вычислительным устройством, можно разделить на два типа.

К первому типу относятся команды, результат выполнения которых помещается в локальную память по адресу первого операнда. В EC ЭВМ к этому типу относятся такие команды форматов RR и RX, как сло-. жение, вычитание, умножение и т.п. При этом операндами могут быть 32-разрядные числа как с фиксированной, так и с плавающей точкой. В целях упрощения выполнение в устройстве команд данного типа рассмотрено на примере команды RX-формата "3aгрузка", обозначение которой L для операндов с фиксированной точкой и LE для операндов с плавающей точкой. Выполне17

1716528 ние команд L u LE заключается в помещении

32-разрядного слова, расположенного в основной памяти по адресу второго операнда, в локальную. память по адресу первого операнда.

Ко второму типу относятся команды, выполнение которых заключается в записи первого операнда в основную память по адресу второго операнда. В ЕС ЭВМ к таким относятся команды "Запись в память", обозначение которых ST u STE для операндов с фиксированной и плавающей точками соответственно.

Процесс выполнения команды можно 15 разделить на следующие этапы: выборка команды, формирование адреса второго операнда (для операнда s основной памяти), считывание операндов, обработка операндов, запись результата. Устройство работа- 20 ет в режиме совмещения операций, при этом все действия по выборке некоторой команды,.формированию адреса операнда и считыванию операнда производятся нэ фоне этапов обработки операндов и записи 25 результата предыдущих команд. В результате такого режима работы устройствоможет в каждом своем такте выполнять по одной команде, если обработка операндов и запись результатов выполняемых команд 30 может быть осуществлена за один такт работы устройства. Если этапы обработки oneрандов и записи результата некоторой команды требуют более одного такта рабо35 ты устройства, то выполнение последующих команд задерживается на необходимое количество тактов.

Не является существенным, как конкретно происходит выборка команды, поэтому соответствующие адресные цепи и 40 накопители информации не показаны. Ход операции очередной команды и ад