Устройство для селекции признаков объектов

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики, в частности к устройствам для селекции признаков объектов, и может быть использовано при распознавании входных сообщений. Цель изобретения - повышение, быстродействия устройства. Поставленная цель дости .гается путем селекции высокоприоритетных сообщений, что обеспечивается введением четырех групп триггеров, второй и третьей групп элементов И, трех элементов ИЛИ и двух элементов задержки. 2 ил.

СОЮЗ COBETCHHX

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК ов SU а>

А1 (51)5 G 06 К 9 36

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4496650/24 (22) 21. 10. 88 (46) 29.02.92. Бюл. № 8 (71) Каунасский политехнический институт им. A.Ñíå÷êóñà (72) В.И,Ветерис и P. — À.Â.Âåòÿðèñ (53) 681.327.12 (088.8) (56) Авторское свидетельство СССР

¹ 1242999, кл. С 06 K 9/36, 1984.

Авторское свидетельство СССР

¹ 1203569, кл. G 08 С 19)28, 1984.. (54) УСТРОЙСТВО ДЛЯ CEJIEKIQSI ПРИЗНАКОВ ОБЪЕКТОВ

Изобретение относится к автоматике, в частности к устройству для селекции признаков объектов, и может быть использовано в системах передачи и приема признаков объектов.

Цель изобретения — повышение быстродействия устройства путем селекции каналов с разными приоритетами.

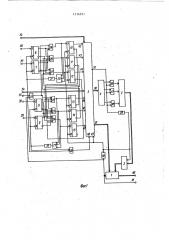

На Фиг. 1 представлена блок-схема устройства; на Фиг. 2 — коммутатор.

Устройство содержит первый 1 и второй 2 блоки памяти-, регистр 3;. де- шифратор 4, коммутатор 5, первую б и 7, вторую 8 и 9, третью 10-12 и четвертую 13-15 группы триггеров,пер-... вую 16-18, вторую 19-21 и третью 22.-

24 группы элементов И, первый элемент

25 ИЛИ, второй 26, третий 27 и четвертый 28 элементы ИЛИ, первый 29, второй 30, третий 3,1 и четвертью 32 элементы задержки.

На чертеже (Фиг.,1) также показа-. ны 33, 34 . — информационные входы сис-темы, 35 - синхронизирующий вход сис2. (57) Изобретение относится к области автоматики, в частности к устройст.вам для селекции признаков объектов, и может быть использовано при распознавании входных сообщений. Цель изобретения †повышение. быстродействия устройства. Поставленная цель достигается путем селекции высокоприоритетных сообщений, что обеспечивается введением четырех групп триггеров, второй и третьей групп элементов И, трех элементов ИЛИ и двух элементов задержки. 2 ил. темы, 36-39 .— управляющие входы системы, 40 - информационный выход системы, а выход 41 — синхронизирующий выход системы.

На Фиг. 1 и 2 также показаны входы коммутатора 42-44 и 45-47, являющиеся управляющими входами коммутатора первой и второй групп, первый 48 и.второй 49 синхронизирующие входы коммутатора, первый информационный выход

50, второй информационный выход 51 и синхронизирующий выход 52 коммутатора.

Коммутатор 5.(фиг. 2) содержит группы элементов И 53-58, группы 5961 элементов ИЛИ, регистр 62, элемент

63 задержки.

Работу системы рассмотрим на при-. мере обслуживания двух входных каналов передачи данных, представленных входами 33, 36, 37 и 34, 38 и 39.

Устройство работает следующим образом.

С приходом на входы 33 и 34 устройства двух сообщений различной ка1716551 тегории срочности на вход 33 поступает одно информационное сообщение, например, высшей категории срочности, а на вход 34 поступает другое инфор5, мационное сообщение, например, второй . категории срочности.

Категория срочности каждого входного сообщения фиксируется состоянием соответствующих триггеров срочности

6, 7 и 8, 9 в каждом из каналов по следующему правилу:

Категория срочности Код

Первая 1 1 Вторая 10 15

Третья 0 1

Четвертая 0 0

Для данного примера триггеры 6 и

7 первого канала будут находиться в единичном состоянии, а Во Втором ка- . 20 нале триггер 8 будет в единичном состоянии, а триггер 9 — в нулевой.

B результате этого комбинацией высоких потенциалов из трех элементов И второй группы будет открыт элемент 25

19 И, а указанной комбинации потенциалов в третьей группе будет соответствовать элемент 23 И.

Импульсом синхронизации с входа 35 система запускается в работу, благодаря чему этот импульс через элемент

25 ИЛИ поступает на импульсные входы всех элементов И второй и третьей групп.

Поскольку открыт высоким потенциалом будет элемент 19 И, то импульс синхронизации проходит через него на единичный вход триггера 10 и устанавливает его в единичное состояние, фиксируя факт поступления сообщения пер40 вой категории срочности.

Высоким потенциалом с единичного выхода через вход 42 триггер 10 открывает по потенциальному входу группу элементов 58 И, на другие входы которых подано информационное сообще45 ние с входа 33.

Параллельно с этим низким потенциалом с нулевого выхода триггера 10 блокируются по соответствующему входу все элементы 22-24 И второго канала, а импульс с выхода элемента 19 И проходит через элемент 26 ИЛИ и задерживается элементом 31 задержки на время установки триггера 10 в единичное состояние и затем, во-первых, возвра- 55 щает триггеры 6, 7 в исходное состояние, а, во-вторых, через элемент 28

ИЛИ поступает через вход 49 коммутатора на импульсные входы элементов

53 И, переписывая код информационного сообщения с входа 33 через элементы 53 И, 59 ИЛИ и 61 ИЛИ на информационные входы регистра 62, куда. код заносится этим же импульсом, поступающим на вход синхронизации регистра 62.

Признак сообщения, характеризующий

его вид, расшифровываЕтся дешифратором 4 с входа 50 и последний на одном из своих выходов выдает высокий потенциал на один из элементов 16-18

И, соответствующий виду полученного сообщения.

Тот же импульс синхронизации, задержанный элементом 63 задержки на время переходных процессов в регистре

62, поступает с выхода 52 коммутатора на импульсные входы элементов 16-18 И и проходит через открытый элемент 1618 И на вход считывания фиксированной ячейки памяти блока 2, выполненного в виде постоянного запоминающего устройства, где записан базовый адрес для записи входного сообщения.

Базовый адрес с выхода блока 2 поступает на информационный вход регистра 3, куда заносится синхроимпульсом с выхода элемента 29 задержки, который задерживает импульс синхронизации на время считывания базового адреса с блока 2 памяти.

В результате на адресном входе блока 1 устанавлИвается адрес записи приоритетного сообщения, которое с выхода 50 коммутатора 5 записывается в блок 1 импульсом записи с выхода элемента 30 задержки, который задерживает импульс синхронизации на время установки адреса в регистре 3.

Тот же импульс записи с выхода 41 системы выдается как импульс прерыва" ния на вход вычислительного комплекса, по которому последний переходит на подпрограмму приема и обработки полученного сообщения. !

Кроме того, с выхода элемента 29 задержки импульс поступает на нулевые входы триггеров 10-15, возвращая триггер 10 в исходное состояние и подтверждая нулевое состояние остальных, а также через вход 48 коммутатора — на сбросовый вход регистра 62, устанавливая его в нулевое состояние.

Импульс записи с выхода элемента

30 задержки поступает на другой вход

1716551 элемента 25 ИЛИ и далее на импульсные входы элементов 19-24 И.

Теперь открыт будет только элемент

23 И согласно коду 10, и прием сообщения второй категории срочности будет осуществлен описанным выше образом.

Таким образом, введение новых узлов и элементов позволило существенно повысить быстродействие устройства и расширить его функциональные возможности путем селекции каналов с высокоприоритетными сообщениями и их внеочередного обслуживания.

Формула изобретения

Устройство для селекции признаков объектов, содержащее первый блок па-, мяти, адресный вход которого соединен с выходом первого регистра, информационный вход подключен к первому выходу коммутатора, а выход является информационным выходом устройства, дешифратор, вход которого соединен с вторым выходом коммутатора, а выходы подключены к одним входам элементов И первой группы, другие входы которых соединены с третьим выходом коммутатора, а выходы подключены к входам считывания второго блока памяти, выход которого соединен с информационным входом первого регистра, первый элемент задержки, вход которого подключен к третьему выходу коммутатора, а выход соединен с синхронизирующим входом первого регистра, с. входом второго элемента задержки, выход которого является синхронизирующим выходом устройства и подключен к входу управления записью первого блока памяти, первый элемент ИЛИ, один вход которого является первым синхронизирующим входом устройства, а другой соединен с выходом второго элемента задержки, при этом первый синхронизирующий вход коммутатора подключен к выходу первого элемента задержки, а информационные входы коммутато-

I ра являются информационными входами устройства, о т л и.ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства путем селекции каналов с разными приоритетами, оно содержит первую и .вторую группы триггеров, единичные входы которых являются управляющими входами устройства, вторую и третью группы элементов И, один вход которых подключен к выходу первого элемента ИЛИ, а другие соединены с соответствующими выходами триг- геров первой и второй групп, второй элемент ИЛИ, входы которого соединены с выходами элементов И второй группы, третий элемент задержки, вход которого подключен к выходу второго элемента ИЛИ, а выход соединен с нулевыми входами триггеров первой группы, третий элемент ИЛИ, входы которого подключены к выходам элементов И третьей группы, четвертый элемент задержки, вход которого соединен с выходом

25 третьего элемента HJIH, а выход подключен к нулевым входам триггеров второй группы, третью группу триггеров, единичные входы которых соединены с выходами соответствующих элементов И второй группы, нулевые входы подклю- чены к выходу первого элемента задержки, прямые выходы соединены с управ" ляющими входами коммутатора первой группы, а инверсные выходы подключены к другим входам соответствующих элементов И третьей группы, четвертую группу триггеров, единичные входы которых соединены с выходами соответствующих элементов И третьей группы, нулевые входы подключены к выходу первого элемента задержки, прямые выходы соединены с управляющими входами ком- „ мутатора второй группы, а инверсные выходы подключены к другим. входам со-. ответствующих триггеров первой группы, L и четвертый элемент ИЛИ, входы которого соединены с выходами третьего и четвертого элементов задержки, а выход подключен к второму синхронизирующему входу коммутатора.

1716551

/

47иИ

1716551

Составитель Н.Давыдов

Техред А,Кравчук

Корректор М.Самборская

Редактор А.Долинич

Заказ 615 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101