Запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к запоминающим устройствам и может быть использовано для построения дублированных постоянных запоминающих устройств. Целью изобретения является повышение надежности работы устройства . Цель достигается тем, что устройство содержит п дополнительных сумматоров по модулю два, п схем сравнения ил блоков контроля с соответствующими связями, а также каждый из блоков контроля содержит два элемента И, один элемент ИЛИ и два инвертора. 1 з.п.ф-лы. 4 ил., 1 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 6 11 С 17/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ: (21) 4649561/24 (22) 13.02.89 (46) 29.02.92. Бюл. N 8 (72) Е.А.Брик и А.А.Крупский (533 681.327.66 (088.8) (56) Брик Е.А. Техника ПЗУ, M,: Советское радио, 1969, с.204.

Авторское свидетельство СССР ЬЬ

1635224, кл. 6 11 С 17/00, 1988.

Изобретение относится .к запоминающим устройствам (ЗУ) и, s частности, может быть использовано для построения дублированных постоянных запоминающих устройств.

Целью изобретения является повышение надежности работы устройства.

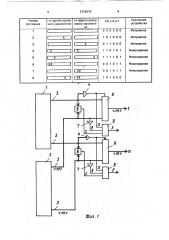

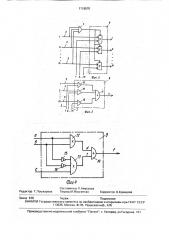

На фиг.1 показано предлагаемое устройство; на фиг.2 показана i-я группа мультиплексоров; на фиг.3- i-я схема сравнения;на фиг.4- одна из возможных модификаций блока контроля.

УСтройство состоит из основного 1 и резервного 2 накопителей, выходные шины

3 которых разделены на и групп по.m шин в группе, nm-входовых сумматоров 4 по моду-. лю два, nm мультиплексоров 5, разделенных Hà и групп 6 по m мультиплексоров 5 в группе, и дополнительных rn-входовых:.сум- маторов 7 по модулю два, и схем 8 сравнения, п трехвходовых блоков 9 контроля.

Каждый из nm мультиплексоров 5 работает по алгоритму 2-М, т.е. в зависимости от,, Ы„, 1716570 А1 (54) ЗАПОМИНАЮЩЕЕ. УСТРОЙСТВО (57) Изобретение относится к запоминающим устройствам и может быть использовано для построения дублированных постоянных запоминающих устройств. Целью изобретения является повышение надежности работы устройства. Цель достигается тем, что устройство содержит и дополнительных сумматоров по модулю два, и схем сравнения и и блоков контроля с соответствующими связями, а также каждый из блоков контроля содержит два элемента И, один элемент ИЛИ и два инвертора, 1 з.п.ф-лы, 4 ил., 1 табл. сигнала управления на своем управляющем входе пропускает на свой выход один из двух входных сигналов.

Каждая из и схем 8 сравнения при помощи m двухвходовых сумматоров 10 по модулю два и элемента ИЛИ 11 сравнивает два д

m-разрядных числа и при несовпадении хотя бы одного из разрядов вырабатывает на своем выходе сигнал несовпадения С.

Одна из возможных модификаций блока О

9 контроля состоит из первого 12 и второго И

13 элементов И, элемента ИЛИ 14 и первого 4

15 и второго 16 инверторов. О)

В таблице перечислены возможные состояния двух дублирующих друг друга групп выходных сигналов 3 основного и резервного накопителей. Сами группы в таблице условно обозначены прямоугольниками, а . одиночные ошибки в группах — значком X.

Буквами а, Ь, с, d, е, f в таблице и на рисунках обозначены соответственно выходные сигналы сумматора 4 по модулю два, дополнительного сумматора 7 по модулю два, схе1716570

55 мы 8 сравнения, первого элемента И 12, второго элемента И 13, блока 9 контроля.

Устройство работает следующим образом.

При исправности всех 2 m сигналов 3 1-й группы (состояние 1 в таблице) все сигналы а — f равны нулю. На выход устройства через группу 6 мультиплексоров 5 данной I-й группы проходят выходные сигналы 3 основного накопителя 1.

При состоянии 2 (одиночная ошибка в основной группе) сигналом а=1 переключаются мультиплексоры 5 I-й группы 6 и на выход устройства проходят исправные выходные сигналы 3 I-й группы резервного накопителя 2.

При состоянии 3 (одиночная ошибка в резервной группе) сигнал а=О и поэтому на выход устройства проходят исправные выходные сигналы основного накопителя 1.

При состояниях 1 — 3 сигнал f равен нулю, что указывает на исправность устройства в целом (несмотря на наличие одиночных ошибок при состояниях 2 и 3). При состояниях 4- 7 сигнал f. равен единице, что указывает на неисправность устройства. В этих случаях по сигналам f производится останов и последующий ремонт устройства.

Поэтому более сложные ошибки (тройные и т,д.) в первых семи состояниях в таблице не указаны и могут не рассматриваться. Предполагается, что сложные ошибки (в т,ч, и двойные) возникают в результате постепенного накопления одиночных ошибок запоминающих.элементов накопителей, т.е, что состояниям 4 или 5 предшествовало состояние 2 или 3, состоянйю 6 — состояние 2, состоянию 7 — состояние 3. При состоянии

7 на выход устройства проходят сигналы 3 исправной группы основного накопителя 1, тем не менее при этом состоянии устройство следует считать неисправным, так как в противном случае состояние 7 может перейти в более сложное состояние 8 с одной ошибкой в основной группе и с двумя прежними ашибкамй в резервной группе, которое не будет обнаружено (так как состояние

8 неотличимо от состояния 2).

Таким образом, устройство обеспечивает правильную работу при состояниях 1 -3, а также обнаруживает все состояния 4 — 7 и не допускает перехода в более сложные состояния. При состояниях 4-6 известное устройство будет вырабатывать неверные выходные сигналы.

Формула изобретения

1. Запоминающее устройство, содержащее сумматоры по модулю два, мультиплек5

35 соры, основной и резервный накопители, выходные шины каждого из накопителей состоят из п групп, где п Ы, по m шин в каждой группе, m выходных шин I-й (1=1,п) группы основного накопителя соединены с

m информационными входами 1-ro сумматора по модулю два и с первыми информационными входами мультиплексоров I-й группы мультиплексоров, m выходных шин

i-й группы (I=1,n) резервного накопителя соединены с вторыми информационными входами m мультиплексоров i-й группы мультиплексоров, выход I-го сумматора по модулю два соединен с управляющими входами m мультиплексоров 1-й группы, выходы

n-.m мультиплексоров являются информационными выходами устройства, о т л и ч а ющ е е с я тем, что, с целью повышения надежности работы устройства, оно содержит и дополнительных сумматоров по модулю два, и схем сравнения и п блоков контроля, m выходных шин I-й группы основного накопителя соединены с входами первой группы

i-й схемы сравнения, m-выходных шин i-й группы резервного накопителя соединены с входами второй группы .1-й схемы сравнения и.с m информационными входами I-го дополнительного сумматора по модулю два, выход i-го сумматора по модулю два соединен с первым информационным входом i-го блока контроля, вход 1-ro дополнительного сумматора по модулю два соединен с вторым информационным входом I-ro блока контроля, выход i-й схемы сравнения соединен с третьим управляющим информационным входом i-го блока контроля.

2. Устройство по п.1, о т л и ч а ю щ е ес я тем, что каждый из блоков контроля содержит два элемента И, один элемент .

ИЛИ и два инвертора, причем первый вход первого элемента И соединен с входом первого инвертора и является первым информационным входом блока контроля, выход первого инвертора соединен с первым входом второго элемента И, второй информационный вход блока контроля соединен с вторым входом первого элемента И и с входом второго инвертора, выход которого соединен с вторым входом второго элемента

И, третий информационный вход блока контроля соединен с третьим входом второго элемента И, выходы первого и второго элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого является выходом блока контроля.. 1716570

Фие. 2

f 2...m

Фис.8

Puz4

Составитель Л.Амусьева

Редактор Т.Лошкарева Техред M,Ìoðãåíòàë Корректор О.Кравцова

Заказ 616 Тираж Поднисное

8НИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород. ул.Гагарина, 101