Коммутатор

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматической коммутации и может быть использовано в цифровых электронных автоматических телефонных станциях для построения цифрового коммутационного поля, а также в сетях передачи данных. Цель изобретения повышение быстродействия и надежности путем анализа состояний входных и выходных каналов. Устройство характеризуется новым выполнением блока приема команд и блока передачи команд. Блок приема команд содержит мультиплексоры, память входных команд, память-указатель входных команд, память активности входных каналов , регистры. Блок передачи команд содержит мультиплексоры, память выходных команд, регистры, преобразователь кодов. Цель достигается путем выбора только исправных и подключенных портов, при этом в устройстве обеспечивается возможность реагировать на изменения состояний входных и выходных каналов в зависимости от внутреннего состояния коммутатора. 6 ил., 1 табл. Ё

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 04 Q 11/06

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1389011 (21) 4759490/09 (22) 20.11.89 (46) 29,02,92. Бюл. N 8 (71) Научно-исследовательский институт

"ВЭФ" (72).А.А.Гаврилов, В.А.Гаврилов и П.У.Морейн (53) 621.395.34 (088,8) (56) Авторское свидетельство СССР

N - 1389011, кл. Н 04 0 11/06, 1987, (54) КОММУТАТОР (57) Изобретение относится к автоматиче. ской коммутации и может быть использовано в цифровых электронных автоматическйх телефонных станциях для построения цифрового коммутационного поля, а также в се-. тях передачи данных . Цель изобретения—

Изобретение относится к автоматической коммутации и может быть использовано в цифровых АТС для построения цифрового коммутационного поля, а также в сетях передачи данных.

Цель изобретения — повышение быстродействия и надежности путем анализасостояуия входных и выходных каналов.

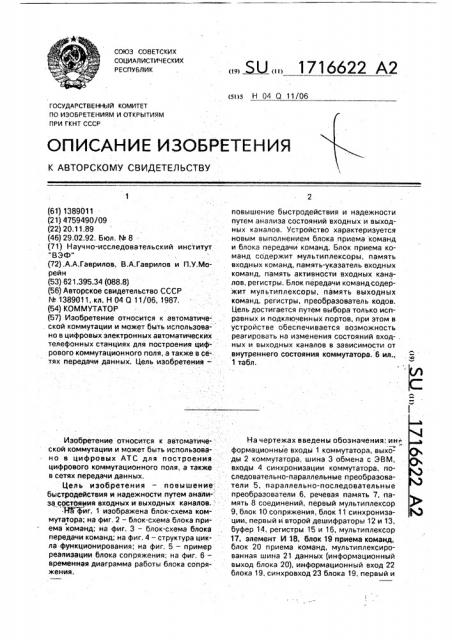

Нб фиг. 1 изображена блок-схема коммутатора; на фиг. 2 — блок-схема блока приема команд; на фиг. 3 — блок-схема блока передачи команд; на фиг. 4 — структура цикла функционирования; на фиг, 5 — пример реализации блока сопряжения; на фиг, 6— временная диаграмма работы блока сопряжения.

„„. Ж„„1716622 А2 повышение быстродействия и надежности путем анализа состояний входных и выходных каналов. Устройство характеризуется новым выполнением блока приема команд и блока передачи команд. Блок приема команд содержит мультиплексоры, память входных команд, память-указатель входных команд, память активности входных каналов, регистры. Блок передачи командсодержит мультиплексоры, память выходных команд, регистры, преобразователь кодов.

Цель достигается путем выбора только исправных и подключенных портов, при этом в устройстве обеспечивается возможность реагировать на изменения состояний вход- . ных и выходных каналов в зависимости от внутреннего состояния коммутатора. 6 ил., 1 табл, На чертежах введены обозначения, ин формационные входы 1 коммутатора, выходы 2 коммутатора, шина 3 обмена с ЭВМ, входы 4 синхронизации коммутатора, последовательно-параллельные преобразователи 5, параллельно-последовательные преобразователи .6, речевая память 7, память 8 соединений, первый мультиплексор

9, блок 10 сопряжения, блок 11 синхронизации, первый и второй дешифраторы 12 и 13, буфер 14, регистры 15 и 16, мультиплексор

17, элемент И 18, блок 19 приема команд, блок 20 приема команд, мультиплексированная шина 21 данных (информационный выход блока 20), информационный вход 22 блока 19, синхровход 23 блока 19, первый и

1716622 второй тактовые входы 24 и 25 блоков 19 и Функционирование коммутатора про20, третий выход 26 блока 20, второй выход исходит синхронно в соответствии со струк27 блока 20, второй адресный вход 28 бло- турой цикла по фиг. 4. ков 19 и 20, информационный вход 29 блока Цикл состоит из 32 временных интерва20 и информационный выход блока 19, пер- 5 лов. Каждый временной интервал разбит на вый и второй управляющие входы 30, 31 16 равных подциклов функционирования, в б к 19 и авляющий вход 32 блока 20, каждом из которых производится обслуживыход 33 записи блока 13, выход 34 номера вание соответствующего порт . д та. Каж ый канала блока 11, (первый адресный вход подцикл разбит на 4 такта ТО, Т1, Т2, ТЗ, в блоков 19 и 20), выход 35 загрузки блока 11, 10 которых выполняются определенные операвыход36 записи и выход 37 чтения блока 10, ции с блоками коммутатора, Блок 19 приема команд содержит пер- На фиг.4 C01 = С вЂ” 2, если P = О,= С— вый и второй мультиплексоры 38 и 39, па- -1, если РФО. С вЂ” 1, С+1, P P — 1 определяют мять 40 входных команд, память-указатель номера канала со смещением для компенса41 входных команд, память 42 активности 15 ции задержек в блоках 5, 6 и 15. входных каналов, второй и третий регистры Преобразователи 5 и 6 с двойной буфе43 и 44, первый дешифратор 45, первый ризацией обеспечивают последоэлемент ИЛИ 46, третий, первый, второй и вательно-параллельное и параллельчетвертый элементы И 47 — 50, первый и чет- но-последовател ьное и реоб разовертый регистры 51 и 52, первый преобра- 20 вание информации. Дешифратор 12 распрезователь кодов, деляет импульсы загрузки в

Блок 20 передачи команд содержиттре- преобразователи 6 и импульсы разрешения тий мультиплексор 54, память 55 выходных выхода преобразователей 5, команд, пятыи регистр, B егистр 56, второй элемент По импульсам загрузки последовательИЛИ 57, пятый и шестой элементы И 58, 59, 25 но для всех преобразователей 6 осуществдевятыи, восьмой, с д едьмой и шестой эле- ляется загрузка информации с шины 21-, менты И 60 — 63, второй и первый элементы которая поступает из памяти выходных коНЕ 64, 65, шестой регистр 66, второй преоб- манд или из речевой памяти, После загрузки разователь 67 кодов и четвертый мульти- всех преобразователей 6 сигналом загрузки плексор р 68. 30 с выхода загрузки блока 11 информация пеБлок 10 сопряжения содержит буферы регружается в выходные регистры сдвига

69, 70, 71, дешифратор 72, элемент ИЛИ 73 преобразователей 6, из которых она сигнаи 1К-триггеры лом с синхровыхода блока 11 сдвигается на

Коммутатор работает следующим обра- выходы 2 коммутатора, зом. 35 С входов 1 информация последовательНа входы коммутат

1 атора (ИКМ-тракты, но сигналом 23 вводится во входные регист- . в дальнейшем — порты) поступает входная ры сдвига преобразователей 5. После ввода информация по, например, 32-канальным 16 бит происходит загрузка в буферные региинтервалам в каждом IKM-тракте, Каждый стры преобразователей 5, выходы которых канал (пространственно-временное распо- 40 открываются сигналами с дешифратора 12, ложение информации) может находиться в Блок 11 обеспечивает синхронизацию одном из множества допустимых состояний работы коммутатора и смещение номеров (таблица}. Информация с входных каналов каналов в соответствии с фиг. иг. 4. поступает либо в память 40 входных команд Блок 19 приема команд обеспечивает либо в речевую память 7. Четыре старших 45 прием команд и состояний с входных канаазряда информации определяют состоя- лов коммутатора. Блок коммутации, реалиние канала, а остальные разряды могут со- зованный по стандартной схеме держать дополнительную информацию для пространственно-временного коммутатора уточнения типа команды управления, а так- и включающий речевую память 7 и память 8 же речевую информацию и сообщения. Ком- 50 соединений, обеспечивает коммутацию люмутатор реагирует нэ поступающую бого входного канала на любой выходной информацию установлением соединения, канал. Блок 20 передачи команд обеспечиразъединением, а также установлением на вает передачу на выходы 2 коммутатора совых одных каналах (на выходах 2) соответст- ответствующей информации (команды, печивующих состояний, к к с стояний, как реакции на входные 55 состояния). Блок 10 сопряжения обес состояния, Информация на выходы 2 комму- вает сопряжение с шиной 3. татора поступает либо из речевой памяти Блок 19 приема команд включает преоб(при установленном соединении). либо из разователь 53 кодов, задающий режим работы блока приема команд, память 42

1716622 активности входных каналов, память-указатель 41 входных команд, память 40 входных команд, Преобразователь 53 определяет режим работы блока 19 в зависимости от состояния входного канала (выходы регистра

51) — четыре старших разряда информации с шины 21. Мультиплексоры 38, 39 обеспечивают подачу на соответствующие памяти адреса в соответствии со структурой цикла.

Память 42 и регистр 52 представляют собой многоканальный двухразрядный регистр сдвига. Он обеспечивает фиксацию состояния активности для всех входных каналов, Активность устанавливается при поступлении команды управления, т,е. состояний "Нет связи" и "Неисправность.", а снимается по состоянию "Свободно" (второе поступление состояния "Свободно" );

Запись в память 42 разрешается через элемент И 48 сигналом с выхода преобразователя 53. Преобразователь 53 и память 42 выполняют функцию фильтра для памяти входных команд, Запись в память 42 происходит в такте Т1, а чтение — a такте ТЗ: активность включается по факту появления состояний "Неисправность", "Нет связи", "Команда", "Начало"; активность снимается по факту появления второго состояния

"Свободно".

Два разряда памяти 42 позволяют запоминать предыдущее состояние активности для каждого канала. Например, при появлении состояния "Команда" в регистре 51 разрешается запись "1" в память 42 (в памяти 42 — "01"). Информация на запись поступает от блока 53, Появление B регистре 51 состояния

"Свободно" приводит к записи "0" в память

42 (в памяти 42 — "10"), т,е, происходит сдвиг информации активности. Следующее состояние "Свободно" приведет к записи "1" в память 42 (в памяти 42 — "ОО").

Память-указатель 41 входных команд состоит из нескольких одноразрядных ОЗУ и содержит информацию о поступлении в память 40 команды управления или разъединения, а также состояний "Нет. связи" и

"Неисправность". Запись в память-указатель 41 (запись указателя — "1") осуществляется по разрядам, а чтение — одновременно для всех разрядов. Импульсы записи формируются на выходах дешифратора 45. "1" записывается при установке указателя (импульс на выходе элемента 48), "О" — при чтении из памяти 40 (импульс записи на выходе элемента 47).

Сигнал разрешения записи в память 42 и память 41, сигнал разрешения записи в память 40, входная информация на запись в память 42, входная информация на запись в память 41 поступают с выходов блока 53.

Запись "1" в память 41 происходит в такте

Т1 (вход 24 блока 19), запись "0" и чтение— в такте ТЗ (вход 25 блока 19), Указатель входных команд устанавливается по факту появления состояний: "Команда", если входной канал не был активирован; "Неисправность"; "Нет связи"; "Свободно", если входной канал был активирован, Указатель сбрасывается при чтении из соответствующей ячейки памяти входных команд.

Памчть 40 входных команд обеспечивает прием команд и состояний входных каналов. Разрешение записи в память 40 формируется на выходе блока 53, Состояние памятей 40 и 41 может быть прочитано процессором через шину 3. Запись в память 40 происходит в такте Т1 (выход элемента 49), а чтение — в такте ТЗ (вход 25 блока 19).

Запись в память 40 разрешается при появлении на входных каналах состояний:

"Свободно"; "Неисправность" (в неактивном состоянии канала); "Нет связи" (в неактивном состоянии канала); "Команда" (в неактивном состоянии канала), Речевая память 7 обеспечивает хранение речевой информации и данных на время коммутации информации. Запись в память

7 производится постоянно для всех входных каналов в такте Т1, чтение. — в такте ТЗ.

Адрес для чтения запоминается в регистре

1b, в который считывается информация из памяти соединений. В памяти 8 соединений хранится информация о соединениях, В циклах записи по последовательным адресам информация с шины 21 записывается в соответствующие ячейки речевой памяти 7 в следующей последовательности; для D-го канального интервала всех 16-ти портов, для 1-го канального интервала всех

16-ти портов,.„, для 31-го канального интервала всех 16-ти портов, т.е. для всех 512 каналов, В этих циклах информация из памяти соединений считывается в регистр 16.

Адрес памяти 8 соединений в режиме чтения — номер выходного канала, данные— номер входного канала.

В циклах чтения из памяти 7 адрес для чтения поступает из регистра 16 через мультиплексор 9, Данные, считываемые из памяти 7, поступают на шину 21 только при проключенном пути. Проключение пути осуществляется в памяти 55 выходных команд путем записи по соответствующему адресу (выходной канал) состояний: "Речь/данные" — для проключения прямого пути: "Подтверждение" — для проключения обратного пути (проключение произойдет после вывода в

1716622 выходной канал состоя ни я "Подтвер>кдение").

Старший разряд, определяющий состояние "Речь/данные", коммутирует на шину

21 один из двух источников информации. речевая память 7 или память 55 выходных команд.

Блок 20 передачи команд обеспечивает запоминание и передачу на шину 21 состояния выходного канала, Преобразователь

67 обеспечивает задание режима перезаписи информации в памяти 55, Регистр 68 запоминает состояние старших разрядов счить,ваемой из памяти 55 информации, Мультиплексор 68 передает на выход информацию для перезаписи, которая состоит из номера канала (вход 34 блока 20) и состояния вь1ходов блока 67, формирующую состояние для перезаписи, или информацию с входов 29 для "-аписи с шины 3. Перезапись осуществляется при чтении из памяти 55 состояния "Подтверждение", которое заменяется на состояние "Речь/данные", обеспечивающее проключение пути путем запрета регистра 56 и оазрешения буфера

14 сигналом 26 с выхода элемента 58, причем разрешение — при "1" в старшем разряqe регистра 68. При чтении из памяти 55 кода "Подтверждение" в старшем разряде регистра 65 — "0" и сигнал разрешения появляется на выходе элемента 59 (разрешение регистра 56), В этом случае буфер 14 запрещен.

Аналогично состояние "Команда" может изменяться на состояние, на которое коммутатор не реагирует, т,е. состояние, которое является фоном, на котором передаются команды. Например, это может быть состояние "Занято".

Процесс перезаписи происходит после того, как информация из памяти 55 перепишется в регистр 56, запись в который происходит в такте Т1 (вход 24 блока 20). В такте

ТЗ происходит перезапись, причем она зависит от состояния четырех старших разрядов считываемой информации, которые записываются в регистр 66, Один выход блока 67 определяет, необходимо ли осуществлять перезапись, остальные разряды определяют код состояния для перезаписи, Состояние старшего разряда регистра

66 определяет праключение пути, при котором импульс разрешения выхода появляется не на выходе элемента 57, а на выходе элемента 58, который открывает выходы byфера 14.

Во время перезаписи в такте Т3 на выходе элемента 62 формируется сигнал, который управляет мультиплексором 68. В остальных случаях в такте ТЗ на выходе элемента 63 появляется сигнал готовности, который во время перезаписи запрещен, так как цикл процессора с шины 3 не может совпадать с циклом перезаписи. Сигнал уп5 равления мультиплексором формируется на выходе элемента 61, сигнал разрешения записи — на выходе элемента 60.

Блок 10 сопряжения обеспечивает возможность работы с микроЭВМ и синхрони10 зацию с коммутатором, Буферы 69, 70, 71 обеспечивают развязку коммутатора от шины 3 (от управляющего процессора), дешифратор 72 вырабатывает сигнал выбора, который позволяет передавать данные че15 рез буфер 69 и сигнал готовности через буфер 71. Триггер 74 включается по фронту сигнала 23 при наличии сигнала выбора на выходе дешифратора 72, а выключается при включении триггера 75, который включается

20 по фронту сигнала 27, а выключается при окончании сигнала выбора, т.е. триггер 75 формирует сигнал готовности на шину 3.

Коммутатор в режиме приема и передачи информации работает следующим абра25 зом.

Данные поступаю последовательно нэ вход блоков 5 с входов 1 коммутатора. Они вводятся во входные регистры сдвига блаков5, из которыхсигналом 35записываются

30 н выходные буферные регистры блока 5. Такая процедура происходит синхронно и одновременно для всех входных портов.

Записанная в блоки 5 информация последовательно в тактах Т0, Т1 передается

35 на мультиплексированную шину 21 и в конце такта Т1 записывается в регистр 15. Дальнейшая обработка поступившей информации осуществляется в следующем подцикле, в котором она загружается либо

40 в память 40, либо в память 7.

При передаче данных они считываются или из памяти 55, или из речевой памяти 7, э в такте ТЗ поступают на шину 21 либо через регистр 56, либо через буфер 14 в

45 зависимости от состояния старшего разряда регистра 66, Далее данные с шины 21 записываются во входной регистр блока 6 обслуживаемого в данный момент порта, После загрузки всех блоков 6 осуществляет50 ся сигналом 35 перезагрузка в выходные регистры сдвига блоков 6, из которых информация в последовательном виде передается на выходы 2 коммутатора.

Установление соединения в коммутато55 ре обеспечивается командой управления.

После поступления команды канал переводится в состояние "Речь/данные", на которое коммутатор не реагирует. Посылка следующей команды для следующего коммутатора возможна только после получения

1716622

25

35

50

55 подтверждения. При невозможности установления соединения обрат н ый ка нал (номер обратного канала 32 — номер прямого канала) устанавливается в состояние "Занято". Коммутатор выполняет команду, если есть свободный путь; выбирает исходящее направление в соответствии с поступившей командой, причем выбор канала (если он не был указан в команде) осуществляется исходя из наименьшей задержки прохождения данных через коммутатор, Одновременно устанавливается обратный путь.

После установления прямого и обратного пути в памяти соединений проключается прямой путь и посылается "Подтверждение", после вывода которого в выходной кан ал автоматически осуществляется проключение обратного пути записью в память выходных команд состояния

"Речь/данные", Следующая команда управления проходит на следующий коммутатор через установленный путь..

При приеме команды активируется входной канал путем записи "1" в память 42, Все последующие команды, поступившие

Ilo активированному каналу, не записываются в память 40, Снятие активности входного .канала осуществляется с переходом входного канала в состояние "Свободно".

Разъединение пути или замена состояния "Занято" на состояние "Свободно" осуществляется по получении состояния

"Свободно" на входном канале, Коммутатор обеспечивает повышение надежности (отказоустойчивости), адаптивности и быстродействия коммутационного поля, обеспечивает построение систем коммутации с распределенным управлением, Формула изобретения

Коммутатор по авт.св. N 1389011, о тл и ч а ю шийся тем, что, с целью повышения быстродействия и надежности путем анализа состояния входных и выходных каналов, блок приема команд выполнен в виде последовательно соединенных первого регистра и первого преобразователя кодов, первый и второй выходы которого соединены с первыми входами соответственно первого и второго элементов И, вторые входы которых объединены и являются первым тактовым входом блока приема команд, вторым тактовым входом которого являются объединенные первые входы третьего элемента И, второго и третьего регистра, вторые входы третьего элемента И и второго регистра объединены и являются первым управляющим входом блока приема ко5

20 манд, вторым управляющим входом которого является второй вход третьего регистра, выход третьего элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента И и входом записи памяти активности входных каналов, выход первого элемента ИЛИ соединен с входом разрешения первого дешифратора, выходы которого подключены к входам записи памяти-указателя входных команд, выходы которого подключены к информационным входам третьего регистра, первый адресный вход блока приема команд подключен к первому и второму информационным входам первого мультиплексора и первому информационному входу второго мультиплексора, второй информационный вход которого. подключен к второму адресному входу блока приема команд, синхровход которого подключен к управляющим входам первого и второго мул ьтиплексоров, первому входу четвертого элемента И и входам загрузки первого и четвертого регистров, выходы первого мультиплексора подключены к адресным входам памяти активности входных каналов, первый информационный вход которого соединен с третьим выходом первого преобразователя кодов, четвертый выход которого соединен с.вторым входом четвертого элемента И, выход которого соединен с информационным входом памяти-указателя входных команд, адресные входы которого, адресные входы памяти входных команд и информационные входы первого дешифратора объединены и соединены с выходом второго мультиплексора, выходы памяти активности входных каналов соединены с входами четвертого регистра, первый выход которого соединен с вторым информационным входом памяти активности входных каналов и первым входом первого преобразователя кодов, второй вход которого соединен с вторым выходом четвертого регистра, информационный вход блока приема команд соединен с одноименными входами первого регистра и памяти входных, команд, выход которой соединен с информационным входом второго регистра, выходы которого объединены с выходами третьего регистра и являются выходом блока приема команд, выход второго элемента

И соединен с входом записи памяти входных команд, а блок передачи команд содержит последовательно соединенные третий мультиплексор, память выходных команд и пятый регистр, выход которого является информационным выходом блока передачи команд, первые информационные входы третьего и четвертого мультиплексоров объ1716622

Состояние

1111 единены и являются первым адресным входом блока передачи команд, вторым адресным входом которого является второй информационный вход третьего мультиплексора, первый тактовый вход блока пе. редачи команд соединен с входами загрузки пятого и шестого регистров, первые выходы которого соединены с первыми входами второго преобразователя кодов, второй вход которого соединен с вторым выходом шестого регистра, входом первого элемента

НЕ и первым входом пятого элемента И, второй вход которого соединен с первыми входами шестого, седьмого, восьмого, девятого и десятого элементов И и вторым тактовым входом блока передачи команд, первые выходы второго преобразователя кодов соединены с вторыми информационными входами четвертого мультиплексора, выходы которого подключены к информационным входам памяти выходных команд, второй выход второго преобразователя кодов соединен с вторым входом седьмого элемента И и входами вторых элементов НЕ и ИЛИ, выход которого соединен с вторым входом девятого элемента И, выход которого соединен с входом записи памяти выход5 ных команд, второй вход второго элемента

ИЛИ подключен к управляющему входу блока передачи команд, информационные входы которого подключены к третьим информационным входам четвертого муль10 типлексора, управляющий вход которого соединен с выходом седьмого элемента И, управляющий вход третьего мультиплексора соединен с выходом восьмого элемента

И, второй вход которого соединен с выхо15 дом второго элемента НЕ и вторым входом десятого элемента И, выход которого является вторым выходом блока передачи команд, третьим выходом которого является выход пятого элемента И, выход шестого

20 элемента И подключен к управляющему входу пятого регистра, информационный вход которого соединен также с информационным входом шестого регистра.

Нет связи

Неисправность

Свободно (разъединение ) Занято

Подтверждение

Команды управления (команды ановления соединения, команды технического обслуживания ) Сообщение

Квитанция сообщения

Начало

Конец

Речь (данные ) Сбой синхронизации

Нет связи

1716622

1716622 l 716622

30 31 О

Запись m нце

Р-1, ГО1 Регист 15

И пи

3апис т.ение Зались

Р-1, С01 ядр 23 блок И

23

4(8192 кlц } ление

Р, С>1

fAPHLl8

Р C-7

30fl

К C-1 пераиия рес

1716622