Устройство для ввода информации в калькулятор

Иллюстрации

Показать всеРеферат

Изобретение относится к устройствам ввода информации в клавишные вычислительные машины, в частности в калькулято21 ры. Целью изобретения является расширение области применения устройства за счет обеспечения возможности ввода в калькулятор нескольких программ. Устройство содержит первый 1 и второй 7 преобразователи кодов, первый 2 и второй 3 регистры, первый 4 и второй 6 блоки памяти , счетчик 5, блок 8 ключей, блок 9 запуска, первый 10, второй 11 и третий 12 элементы И, с первого по четвертый формирователи 13, 14, 15, 16, элемент ИЛИ 17 и триггер 18. Цель достигается за счет введения в устройство первого блока 4 памяти, первого преобразователя 1 кодов, первого 2 и второго 3 регистров, четвертого формирователя 16, второго 11 и третьего 12 элементов И. 1 з. п. ф-лы, 2 ил. сл 00 ю о

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 06 F 3/02

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

4@фВ5 чфщщВФРмйМф (21) 4707185/24 (22) 12.05.89 (46) 07.03.92, Бюл. N - 9 (71) Бишкекское производственное объединение по выпуску средств вычислительной техники (72) В. А. Андреев и В. Е, Лаптев (53) 681.327,11(088.8) (56) Патент CLUA М 4044398, кл, G 06 F 1/00, 1977.

Авторское свидетельство СССР

N 1117623, кл. G 06 F 3/02, 1984. (54) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ В КАЛЬКУЛЯТОР (57) Изобретение относится к устройствам ввода информации в клавишные вычислительные машины, в частности в калькулятоа9 > . Ы а л 1 7 1 8 2 1 О А 1 ры. Целью изобретения является расширение области применения устройства за счет обеспечения возможности ввода в калькулятор нескольких программ, Устройство содержит первый 1 и второй 7 преобразователи кодов, первый 2 и второй

3 регистры, первый 4 и второй 6 блоки памяти, счетчик 5, блок 8 ключей, блок 9 запуска, первый 10, второй 11 и третий 12 элементы

И, с первого по четвертый формирователи

13, 14, 15, 16, элемент ИЛИ 17 и триггер 18.

Цель достигается за счет введения в устройство первого блока 4 памяти, первого преобразователя 1 кодов, первого 2 и второго 3 регистров, четвертого формирователя 16, второго 11 и третьего 12 элементов И. 1 з. и. . ф-лы, 2 ил.

1718210

Изобретение относится к устройствам ввода информации в клавишные вычислительные машины, в частности в калькуляторы, Целью изобретения является расширение области применения устройства за счет обеспечения возможности ввода в калькулятор нескольких., программ.

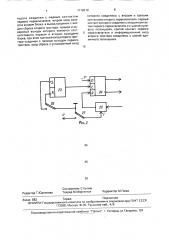

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 — схема блока запуска.

Устройство содержит первый преобразователь 1 кодов, первый 2 и второй 3 регистры, первый блок 4 памяти, счетчик 5, второй блок 6 памяти, второй преобразователь 7 кодов, блок 8 ключей, блок 9 запуска, первый 10, второй 11 и третий 12 элементы

И, первый 13, второй 14, третий 15 и четвертый 16 формирователи, элемент ИЛИ 17 и триггер 18, информационный вход 19 устройства, первый 20 и второй 21 тактовые входы устройства и выход 22 устройства, подключаемый параллельно клавишам калькулятора. Блок 9 запуска содержит первый 23 и второй 24 триггеры, элемент ИЛИ

25, первый 26 и второй 27 переключатели.

Устройство работает следующим образом.

После подачи питания на устройство оно приводится в исходное состояние с помощью подачи сигнала сброса переключателем 27. Сигнал сброса через элемент ИЛИ

25 блока 9 запуска подается íà R-вход триггера 24, При этом сигналом "Лог. 0" с прямого выхода триггера 24 закрывается элемент И 10 по второму входу, а сигналом

"Лог.1" с инверсного выхода триггера 24 открывается элемент И 12 по первому входу. Затем в регистры калькулятора вносятся исходные данные для решаемой задачи. На индикаторе калькулятора, например, MK-61 (на фигурах не показан) выбирается номер решаемой задачи в старших двух разрядах.

Сегментный код с калькулятора по входу 19 поступает на вход преобразователя 1 кодов и входы элемента ИЛИ 17, Сегментный код разрядов поступает синхронно с управляющими тактовыми сигналами на входах 20, 21. В преобразователе

1 кодов сегментный код преобразуется в двоична-десятичный и поступает на информационные входы регистров 2 и 3. В качестве преобразователя сегментного кода может быть использовано постоянное запоминающее устройство. По приходе сегментного кода старшего разряда его двоично-десятичное значение с выхода преобразователя 1 кодов вносится по управляющему сигналу с входа 20 в регистр 2, По приходе сегментного кода следующего

35 младшего разряда его двоично-десятичное значение вносится по управляющему сигналу с входа 21 в регистр 3.

С выходов регистров 2 и 3 двоично-десятичный код номера задачи подается на адресные входы блока 4 памяти. Сигнал выборки (обращение) к блоку управляющей памяти подключен к шине питания устройства и подается постоянно. В связи с этим для выборки ячейки из блока 4 памяти, аналогично и для блока 6 памяти, достаточно подать соответствующий адрес на его адресные входы. В блоке 4 памяти хранятся начальные адреса программ соответствующих задач. По значению двоично-десятичного номера задачи из блока 4 памяти выбирается начальный адрес cooTBGTGTBóþ щей программы, внесенной в блок 6 памяти, который по сигналу с формирователя 16 вносится в счетчик 5. По адресу, установленному в счетчике 5, на втором одноразрядном выходе блока 6 памяти выбирается код

"Лог. 0", который поступает на второй вход элемента И 11 и закрывает его, подготавливая к работе устройство. При этом запрещается подача сигнала "Сброс" через элемент

ИЛИ 25 на триггер 24, который вырабатывается на элементе И 11 от сигнала с выхода формирователя 15, Сегментный код номера задачи с входа

19 поступает также через элемент ИЛИ 17 на информационный вход триггера 18, По управляющему сигналу с входа 20 триггер

18 устанавливается в единичное состояние, при этом сигналом "Лог, 1" с его выхода открывается элемент И 10 по первому входу.

Устройство готово к выполнению соответствующей задачи, номер которой набран на индикаторе калькулятора.

Для запуска устройства подается сигнал пуска от переключателя 26, При этом переключается триггер 23. Передним фронтом сигнала с выхода триггера 23, поступающим на тактовый вход триггера 24, последний устанавливается в единичное состояние, При установке триггера 24 в единичное состояние сигналом- с его инверсного выхода закрывается элемент И

12, запрещая прохождение управляющего сигнала с входа 21 на управляющий вход счетчика 5, а сигналом с его прямого выходаоткрывается элемент И 10. Передним фронтом сигнала с выхода элемента И 10 запускается формирователь 13. Сигнал с выхода формирователя 13 поступает на счетный вход счетчика 5 и добавляет к его содержимому "1". По новому адресу, установленному в счетчике 5, из блока 6 памяти выбирается первая команда программы, 1718210

45

50 му входу

55 код которой поступает на преобразователь

7 кодов, На втором выходе блока 6 памяти выбирается также код "0", закрывая элемент И 11 по второму входу, По заднему фронту сигнала с выхода формирователя 13 запускается формирователь 15, сигнал с которого поступает на стробирующий вход преобразователя 7 кодов. При этом на выходе преобразователя 7 кодов вырабатывается сигнал на управление одного из ключей блока 8 ключей. Блок 8 ключей по входу 22 закорачивает одну из кнопок калькулятора.

Калькулятор начинает выполнение команды, во время которой сегментный код на индикатор калькулятора не подается, выдача управляющих сигналов на входы 20, 21 не запрещается. При этом через элемент ИЛИ

17 на информационный вход триггера 18 поступает сигнал "Лог. 0". По управляющему сигналу с входа 20 триггер 18 переключается и закрывает элемент И 10, При появлении результатов вычислений на индикаторе калькулятора на информационном входе триггера 18 появляется сигнал "Лог.

1". По управляющему сигналу с входа 20 триггер 18 переключается и открывает элемент И 10. При этом передним фронтом сигнала с выхода элемента И 10 запускается формирователь 13, происходит добавление

"1" к содержимому счетчика 5, выборка следующей команды с блока 6 памяти и процесс ввода команд в калькулятор повторяется, Ввод команд в калькулятор повторяется до тех пор, пока на втором выходе блока 6 памяти не будет выбран код "1", При выборке кода "1" на втором выходе блока 6 памяти элемент И 11 открывается по второПри этом при выработке сигнала формирователем 15 на выходе элемента И 11 вырабатывается сигнал, который через элемент ИЛИ 25 сбрасывает триггер 24 блока 9 запуска. Сигналом с прямого выхода триггера 24 закрывается элемент И 10 по второму входу и процесс выработки сигналов запуска прекращается.

Устройство по отношению к прототипу имеет более расширенные возможности, так как позволяет устанавливать начальные адреса вводимого в калькулятор массива, В результате появляется возможность внесения в память нескольких программ задач и их произвольной выборки, решения разного типа задач без смены в предлагаемом устройстве ПЗУ с прошитой программой, Формула изобретения

1. Устройство для ввода информации в калькулятор, содержащее второй преобразователь кодов, блок запуска, первый элемент ИЛИ, второй блок памяти, блок ключей, счетчик, первый элемент И, первый, второй и третий формирователи и триггер, прямой выход которого соединен с первым входом первого элемента И, второй вход которого соединен с первым выходом блока запуска, а выход — с входом первого формирователя, выход которого соединен с входом второго формирователя, выход которого соединен со стробирующим входом второго преобразователя кодов, при этом выход счетчика соединен с адресным входом второго блока памяти, первый выход которого соединен с информационным входом второго преобразователя кодов, выход которого соединен с входом блока ключей, выход которого является выходом устройства, вход второго формирователя является первым тактовым входом устройства, выход второго формирователя соединен с тактовым входом триггера, информационный вход которого соединен с выходом элемента

ИЛИ, вход которого является информационным входом устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет обеспечения возможности ввода в калькулятор нескольких программ, в него введены первый блок памяти, первый преобразователь кодов, первый и второй регистры, четвертый формирователь, второй и третий элементы И, причем второй вход третьего элемента И является вторым тактовым входом устройства, второй выход блока запуска соединен с первым входом третьего элемента И, выход которого соединен с входом четвертого формирователя, выход которого соединен с управляющими входами второго регистра и счетчика, информационный вход последнего соединен с выходом первого блока памяти, адресные входы группы младших и группы старших разрядов которого соединены соответственно с выходами второго и первого регистров, информационные входы которых соединены с выходом первого преобразователя кодов, вход которого является информацион ным входом устройства, управляющий вход первого регистра соединен с выходом второго формирователя, первый и второй входы второго элемента И соединены соответственно с выходом третьего формирователя и с вторым выходом второго блока памяти, выход второго элемента И соединен с входом блока запуска, выход первого формирователя соединен со счетным входом счетчика, 2. Устройство по и, 1, о т л и ч а ю щ е ес я тем, что блок запуска содержит первый и второй триггеры, первый и второй переключатели и элемент ИЛИ, первый вход ко1718210

40

Составитель С,Кулиш

Редактор Т.Юрчикова Техред М. Моргентал Корректор М.Пожо

Заказ 882 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул,Гагарина, 101 торого соединен с первым контактом первого переключателя, второй вход является входом блока, а выход соединен с входом сброса второго триггера, прямой и инверсный выходы которого являются соответственно первым и вторым выходами блока, при этом тактовый вход второго триггера соединен с прямым выходом первого триггера, вход сброса и установочный вход которого соединены с вторым и третьим контактами второго переключателя, первый контакт которого соединен с вторым контактом первого переключателя и с шиной нулевого потенциала, третий контакт первого

5 переключателя и информационный вход второго триггера соединены с шиной единичного потенциала.