Многоканальный сигнатурный анализатор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для тестового диагностирования многоканальных цифровых устройств. Цель изобретения - уменьшение времени локализации неисправностей в проверяемых каналах - достигается через разделение общей сигнатуры на составляющие, соответствующие каждому из проверяемых каналов. При этом анализатор за один цикл контроля дает возможность определить номера неисправных каналов. 1 з. п. ф-лы, 5 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (s1)s G 06 F 11/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ V

Ю

ЬЭ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4784919/24 (22) 22.01.90 (46) 07.03.92. Бюл. № 9 (71) Ленинградский электротехнический институт им. В. И. Ульянова (Ленина) (72) С. А. Иванов, Б, П. Подкопаев, В. Н.

Смирнов, Ф. В. Филиппов и Н. С. Щербаков (53) 681.326.7(088,8) (56) Авторское свидетельство СССР

¹ 1048475, кл, G 06 F 11/00, 1981..

Изобретение относится к вычислительной технике и может использоваться в системах тестового диагностирования.

Цель изобретения — уменьшение времени локализации неисправностей в проверяемых каналах.

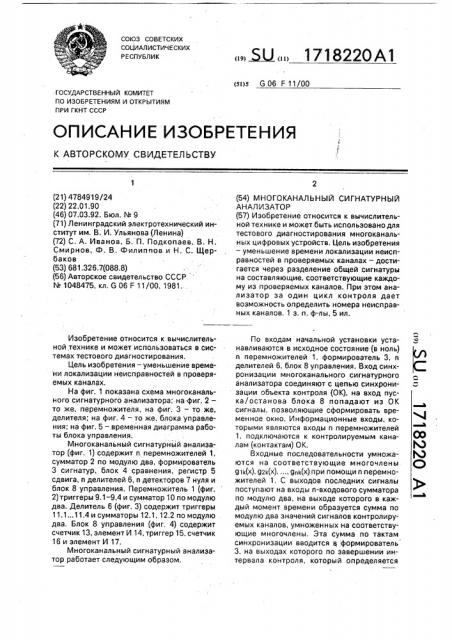

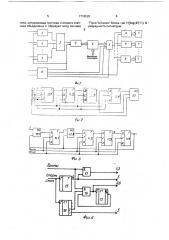

На фиг. 1 показана схема многоканального сигнатурного анализатора; на-фиг. 2— то же, перемножителя, на фиг; 3 — то же, делителя; на фиг. 4 — то же, блока управления; на фиг. 5 — временная диаграмма работы блока управления.

Многоканальный сигнатурный анализатор (фиг, 1) содержит и перемножителей 1, сумматор 2 по модулю два, формирователь

3 сигнатур, блок 4 сравнения, регистр 5 сдвига, и делителей 6, и детекторов 7 нуля и блок 8 управления. Перемножитель 1 (фиг.

2) триггеры 9.1 — 9,4 и сумматор 10 по модулю два. Делитель 6 (фиг. 3) содержит триггеры

11.1...11.4 и сумматоры 12.1, 12.2 по модулю два. Блок 8 управления (фиг, 4) содержит счетчик 13, элемент И 14, триггер 15, счетчик

16 и элемент И 17.

Многоканальный сигнатурный анализатор работает следующим образом. (54) МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ

АНАЛ ИЗАТОР (57) Изобретение относится к вычислительной технике и может быть использовано для тестового диагностирования многоканальных цифровых устройств, Цель изобретения — уменьшение времени локализации неисправностей в проверяемых каналах — достигается через разделение общей сигнатуры на составляющие, соответствующие каждому из проверяемых каналов. При этом анализатор за один цикл контроля дает воэможность определить номера неисправных каналов. 1 з. и. ф-лы, 5 ил.

По входам начальной установки устанавливаются в исходное состояние (в ноль) и перемножителей 1, формирователь 3, и делителей 6. блок 8 управления. Вход синхронизации многоканального сигнатурного анализатора соединяют с цепью синхронизации объекта контроля (ОК), на вход пуска/останова блока 8 попадают из ОК сигналы, позволяющие сформировать временное окно. Информационные входы, которыми являются входы п перемножителей

1, подключаются к контролируемым каналам (контактам) ОК.

Входные последовательности умножаются на соответствующие многочлены

g1k(x), g2k(x), gnk(x) при помощи п перемножителей 1, С выходов последних сигналы поступают на входы и-входового сумматора по модулю два, на выходе которого в каждый момент времени образуется сумма по модулю два значений сигналов контролируемых каналов, умноженных на соответствующие многочлены. Эта сумма по тактам синхронизации вводится ц формирователь

3, на выходах которого по завершении интервала контроля, который определяется

1718220

45

50 временным окном, будет сформирована сигнатура, характеризующая текущее техническое состояние ОК. Сравнение полученной сигнатуры с эталонной происходит в блоке сравнения 4 путем ее поразрядного суммирования по модулю два с эталонной сигнатурой.

Результат сравнения поступает в параллельном коде в регистр сдвига 5 и после преобразования в последовательный код с выхода регистра 5 подается одновременно на входы п делителей 6, в которых осуществляется деление поступившего сигнала на многочлены g>(x), Яг(х), ..., gn(x). Остатки от деления, сформированные в каждом из и делителей 6, подаются на блоки детекторов

7 нуля, где и осуществляется анализ результатов контроля узла, исправные каналы будут характеризоваться нулевыми остатками от деления на соответствующие многочлены, неисправные — ненулевыми остатками.

Я k(X)=92(X) 93(Х),, gn(X);

92(с(х)=91(х).ЯЗ(х), " Ял(х);

gnk(X)=g1(X).g2(X), ..., Яп-1(X), где Яз(х) — многочлен формирователя 3, Возможность обнаружения с помощью рассматриваемого многовходного сигнатурного анализатора канала с ошибкой обусловлена свойствами арифметических операций над конечными полями (в данном случае над подем 6(Рг), Блок 8 предназначен для выработки временного окна, т,е. интервала времени, в течение которого и роисходит сжатие тестовой последовательности в формирователе 3. Кроме того, данный блок синхронизирует и перемножителей 1 и формирователь 3, синхронизирует работу регистра 5 и и делителей 6, а также управляет процессом преобразования формата информации. и детекторов нуля 7 предназначены для анализа остатков от дления в и делителях 6 на равенство нулю. Каждый из детекторов выполнен как многовходовый элемент ИЛИ, причем количество входов соответствует числу разрядов в регистре сдвига соответствующего делителя, Каждый выход. регистра сдвига делителя подключен к одному из sxoдов элемента ИЛИ, поэтому на выходе последнего низкий уровень будет только в том случае, если во всех разрядах регистра записаны О, что свидетельствует о равенстве нулю всего остатка от деления, Блок сравнения 4 выполнен на N элементах ИСКЛЮЧАЮ ЩЕ Е ИЛ И (где N — разрядность сигнатуры).

Формула изобретения

1. Многоканальный сигнатурный анализатор, содержащий сумматор по модулю

35 два и формирователь сигнатур, информационный вход которого подключен к выходу сумматора по модулю два, о т л и ч а юшийся тем, что, с целью уменьшения времени локализации неисправностей в п ро ве ря емых каналах, он содержит группу из и перемножителей, блок сравнения, регистр сдвига, группу из и делителей, группу из и детекторов нуля, где и — число контролируемых каналов, блок управления, причем информационные входы п перемножителей группы являются первой группой информационных входов анализатора, выходы и перемножителей группы соединены с входами сумматора по модулю два, группа выходов формирователя сигнатур соединена с первой группой информационных входов блока сравнения, вторая группа информационных входов которого является второй группой информационных входов анализатора, группа выходов блока сравнения соединена с группой информационных входов регистра сдвига, выход которого соединен с информационными входами и делителей группы, группа информационных выходов каждого из которых соединена с группой входов соответствующего детектора нуля группы, вход сигнала "Пуск/останов" и синхровход блока управления являются одноименными входами анализатора, синхровходы формирователя сигнатур и п перемножителей группы объединены и подключены к первому выходу блока управления, вход параллельной загрузки регистра сдвига подключен к второму выходу блока управления, синхровходы п делителей группы и вход сдвига регистра сдвига объединены и подключены к третьему выходу блока управления, вход режима регистра сдвига подключен к четвертому выходу блока управления.

2. Анализатор по и. 1, о т л и ч а ю щ и йс я тем, что блок управления содержит триггер, два счетчика и два элемента И, выход первого элемента И является первым выходом блока, выход триггера соединен с первым входом первого элемента И и является вторым выходом блока, выход второго элемента И соединен со счетным входом первого счетчика и является третьим выходом блока, выход первого разряда второго счетчика является четвертым выходом блока, первый вход второго элемента И объединен с вторым входом первого элемента И и образует синхровход блока, второй вход второго элемента И подключен к выходу второго разряда второго счетчика, третий вход второго элемента И подключен к инверсному выходу г-го разряда первого счет1718220 чика, синхровходы триггера и второго счет- "Пуск/останов" блока, где г=Д!оцгМ (+1), N— чика объединены и образуют вход сигнала разрядность сигнатуры.

1718220

Такт. ониульСЫ

Отцова

Стол

ВыхоИ руэгг.f5

Еыхои 1

ЕТ®

Рыб зл- та

ff17

8a хоЫ

Сr fb юхоУ ф ЩЯ

И1В

Выход

СТ 9

40

50

Составитель И, Иванов

Редактор И.Ванюшкина Техред М,Моргентал Корректор Н.Король

Производственно-издатеаьскии комбинат "ГГатент", г. Ужгород, ул.Гагарина, 101

Заказ 882 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5