Устройство для проверки хроматографических колонок

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в 2 кроматографическом приборостроении для автоматического контроля качества (идентичности ) колонок. Целью изобретения является расширение функциональных возможностей за счет определения отклонения параметров колонки от идеальных значений. В известное устройство введены цифроаналоговый преобразователь и регистр , информационный вход которого подключен к шине, управляющий вход регистра соединен с соответствующим входом селектора , выход регистра соединен с входом цифроаналогового преобразователя, выход которого является информационным выходом устройства. 3 ил., 1 табл.

СОЮЗ СОВГТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1608638 (21) 4815101/24 (22) 05,03.90 (46) 07.03.92 Бюл. % 9 (71) Дзержинское опытно-конструкторское бюро автоматики и Научно-производственное объединение "Химавтоматика" (72) О.В.Столяров и В,Л.Авдоничев (53) 681.325 (088.8) (56) Авторское свидетельство СССР

М 1608638, кл. G 06 F 15/00, 17.04.89, (54) УСТРОЙСТВО ДЛЯ ПРОВЕРКИ XPQМАТОГРАФИЧЕСКИХ КОЛОНОК (57) Изобретение относится к вычислительной технике и может быть использовано в

Изобретение относится к вычислительной технике, может быть использовано в хроматографическом приборостроении для автоматического контроля качества (идентичности),колонок и являеТся усовершенствованием изобретения по авт.св. N.

1608638.

Целью изобретения является расширение функциональных возможностей путем определения отклонения параметров колонки от идеальных значений.

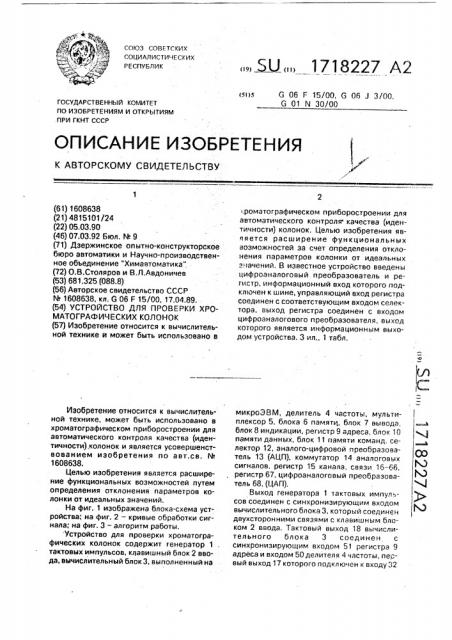

На фиг. 1 изображена блока-схема устройства; на фиг. 2 — кривые обработки сигнала; на фиг. 3 — алгоритм работы. Устройство для проверки хроматографических колонок содержит генератор 1 тактовых импульсов, клавишный блок 2 ввода, вычислительный блок 3, выполненный на

М „, 1718227 А2 (ч>з 6 06 F 15/00, G 06 J 3/00, G 01 N 30/00

::.роматографическом приборостроении для автоматического контроля качества (идентич ности) колонок. Цел ью изобретения я вляется расширение функциональных возможностей за счет определения отклонения параметров колонки от идеальных значений. В известное устройство введены цифроаналоговый преобразователь и регистр, информационный вход которого подключен к шине, управляющий вход регистра соединен с соответствующим входом селектора, выход регистра соединен с входом цифроаналогового преобразователя. выход которого является информационным выходом устройства. 3 ил., 1 табл. микроЭВМ, делитель 4 частоты, мультиплексор 5, блока 6 памяти, блок 7 вывода, блок 8 индикации, регистр 9 адреса, блок 10 памяти данных, блок 11 памяти команд, селектор 12, аналого-цифровой преобразователь 13 (АЦП), коммутатор 14 аналоговых сигналов, регистр 15 канала, связи 16--66, регистр 67, цифроаналоговый преобразователь 68, (ЦАП).

Выход генератора 1 тактовых импульсов соединен с синхронизирующим входом вычислительного блока 3, который соединен двухсторонними связями с клавишным блоком 2 ввода, Тактовый выход 18 вычислительного блока 3 соединен с синхрониэирующим входом 51 регистра 9 адреса и входом 50 делителя 4 частоты, первый выход 17 которого подключен к входу 32

1718227

15

25

35

55 опроса клавиатуры вычислительного блока

3, второй выход 24 делителя 4 частоты подключен к первому информационному входу

33 мультиплексора 5 и первому информационному входу 48 блока 7 вывода, третий выход 25 подключен к второму информационному входу 34 мультиплексора 5, четвертый выход 16 подключен.к третьему информационному входу 35 мультиплексора 5 и входу 64 разрешения выдачи блока 7 вывода; пятый выход 26 делителя частоты 4 соединен с тактовым входом 58 АЦП 13, первый выход 42 мультиплексора 5 соединен с адресным входом 44 блока 6 памяти, вход 45 записи считывания ко второго соединен с вторым выходом 43 мультиплексора 5, выход блока 6 памяти соединен с вторым информационным входом 49 блока 7 вывода, выход которого соединен с входом блока

Выход регистра 9 адреса соединен с адресными входами 36 мультиплексора 5. адресным входом 39 блока 10 памяти данных, адресным входом 40 блока 11 памяти команд и входом 56 селектора 12, информационный выход вычислительного блока 3 соединен шиной 23 с информационными входами 31 регистра 9 адреса, входом.57 регистра 15 канала, входом 46 блока 6 памяти, выходом блока 11 памяти команд, выходом блока 10 памяти данных, выходом 57

АЦП 13 и входом регистра 67. Выход 27 селектора 12 соединен с.входом 59 разрешения ввода АЦП 13, выход 28 селектора 12 соединен с входом 60 запуска АЦП 13, выход 29 селектора 12 — с входом 47 записи регистра 15 канала, выход 65 селектора 12 соединен с входом 66 регистра 67.

Первый управляющий выход 19 вычислительного блока 3 соединен с первым управляющим входом 37 мультиплексора 5.

Второй управляющий вход 38 мультиплексора 5. вход 61 записи блока 10 памяти данных и вход 55 разрешения ввода селекmpa 12 соединены с вторым управляющим выходом 22 вычислительного блока 3. Третий управляющий выход 20 последнего соединен с входом 53 выборки селектора 12, четвертый управляющий выход 21 подключен к входу 52 считывания блока 10 памяти данных и входу 54 разрешения ввода селектора 12, пятый управляющий выход 62 вычислительного блока 3 соединен с входом 63 разрвшения доступа блока 10 памяти данных, шестой управляющий выход 30 соединен с входом 41 записи блока 11 памяти команд, выход регистра 15 канала соединен с адресным входом коммутатора 14 аналоговых сигналов.

Устройство работает следующим образом.

При подаче питания генератор 1 тактовых импульсов начинает вырабатывать тактовую последовательность импульсов, которая поступает на вход блока 3. На выходе 18 блока 3 появляется тактовая последовательность импульсов, синхронная с внутренней частотой синхронизации вычислительного блока 3. В регистре 9 адреса по отрицательному перепаду сигнала на входе

51 запоминается адрес команды в блоке 11 памяти команд, которая выполняется в данном машинном цикле.

Управляющий сигнал с выхода 30 блока

3 поступает на вход 41 блока 11 памяти команд. Код команды по шине 23 адреса данных поступает в блок 3. Устройство работает по алгоритму(фиг. 3), который в виде последовательности команд хранится в бло-. ке 11 памяти команд. Управляющий сигнал с выхода 20 блока 3 поступает на вход 53 .выборки селектора 12, адрес внешнего устройства с выхода регистра адреса — на адресный вход 56 селектора 12.

Под действием управляющего сигнала с выхода 22 вычислительного блока 3, который поступает на вход 55 селектора 12, на выходе 29 формируется сигнал, который стробирует запись кода номера аналогового сигнала. Код номера аналогового сигнала поступает от блока 3 по шине 23 на вход 57 регистра 15. На основании кода, записанного в регистр 15, коммутатор подключает к входу АЦП преобразователя 13 соответствующий аналоговый. сигнал.

Управление коммутатором 14 с помощью регистра 15 позволяет устанавливать частоту опроса каждого входного аналогового сигнала, исходя из частотных свойств самого сигнала, а оптимальная частота опроса каждого входного аналогового канала позволяет экономить память блока 10.

B регистре 9 адреса фйксируется адрес следующего внешнего устройства, повторяется цикл обращения к селектору 12, в результате которого на выходе 28 селектора 12 формируется сигнал, который поступает на вход 60 запуска АЦП 13. Тактовые импульсы с выхода 26 делителя 4 частоты поступают на тактовый вход 58 АЦП 13.

При вводе кода из АЦП 13 в блок 3 на выходе 21 блока 3 формируется сигнал, поступающий на вход 54 селектора 12. В результате на выходе 27 селектора 12 формируется сигнал, поступающий на вход

59 разрешения ввода данных АЦП, а затем по шине 23 в блок 3. Результаты расчетов, их промежуточные значения; исходные параметры хранятся в блоке 10 памяти данных

1718227 и могут быть отображены в блоке 8 индика- программируются частоты таймерных преции. рываний.

При обращении блока 3 к блоку 10 па- Вычислительный блок 3 в темпе реальмяти данных на выходе 62 блока 3 формиру- ного времени производит синхронный расется сигнал обращения, который поступает 5 чет значений первой, второй и третьей на вход 63 управления доступом к блоку 10 производных по формуле Савицкого памяти данных. Под действием управляЮ.-. щих сигналов с выходов 21 и 22 блока. 3, Г!) (! — 1) — 1) которые поступают .на соответствующие У" (2 У! 2 + YI 1 + входы 52 и 61 адреса, а с выхода регистра 9 10. — на адресный вход 39 блока 10, происходит + у,(++! „1) + 2 YI(! обмен данными между блоком 3 и блоком 16 памяти данных по шине 23. актовая последовательность с выхоф а . где верхний индекс О-1, 2, 3) указывает по18 блока 3 поступает на вход 50 делителя-4 15 Р частоты, а тактовая последовательность В точках перегиба, где вторая нроизводвыхода 17 делителя частоты — на вход 32; наЯ обРащаетсЯ в нУль, РегистРиРУетсЯ вРеблоказ.периодследованияимпульсовна " кс РемУмы пеРвой пРоизводной входе 32 представляет период опроса кла-. си нала, вРемЯ выхода РегистРиРУетсЯ в мовиатуры блока 2. Наличие в устройстве кла- -20 мент обРаЩениЯ в нУль тРетьей пРоизвОДвиатуры. позволяет оперативно менять . ной фиг.2. исходные данные, используемые в работе, . Далее на базе этой информации рассчизапрашивать вычислительный блок 3 о ре- тываетсЯ оценка амплитУды сигнала, ползультатах обработки входных сигналов с УшиРины и коэффициента асимметРии по отображением результатов в блоке 8 инди-. 25 кации. 1

На выходе 16 делителя 4 частоты форАЧ=(max(Y ) -m!!1(Y ) ) мируется периодический сигнал, который поступает на вход 35 мультиплексора 5 и

tb — т1 12 — tb . предназначен для управления считыванием 30

1г — 11 из блока 6 памяти. Сигнал с выхода 16делителя 4 частоты поступает на вход 64 блока 7,:

AH=t2-t1; на выходе 22 блока 3 формируется сигнал;: управляющий записью данных в блок 6 па«- К 12 tb . (3) мяти, который поступает на вход 38 мульти- 35

tb t1 плексора 5. С выхода 43 мультиплексора 5 сигнал правления записью и считыванием где AM — оценка амплитуды сигнала; поступает на вход 45 блока 5 памяти.

Данные, предназначенные для записи в: "Ac — оценка коэффициента асимметблок 6 памяти, поступают на вход 46 по.40 Рии

1 1 шине 23. Q выхода 25 делителя 4 частоты на и ах(т ), и1! п(У ) — максимальное и мивход 34 мультиплексора 5 поступают млад- нимальное значения производных сигнала шие разряды адреса блока 6 памяти, с выхо-. соо ве ствен о; да 24 делителя 4 частоты на вход 33 . tb,11,t2 — вРемЯвыхоДа1вРемЯРегистРамультиплексор вход48блока7 вывода 45 ции еах(У ), вРемЯ РегистРации а!п(У )

1 1 — старшие разряды адреса. блока 6. . соответственно.

На вход 36 мультиплесора 5 поступают . Эффективность колонки может быть адресные разряды с выхода регистра 9 адре- . Рассчитана по фоРмУле са. Адрес с выхода 42 мультиплексора 5 поступает на адресный вход 44 блока 6 памяти. 50 . " "6 (tb 2AH) 4(tbI AH)

Управление мультиплексором осуществляется сигналом с выхода 19 блока 3, который где п — число теоретических тарелок; поступает на вход 37 мультиплексора 5. Дан- . tb — РасстоЯние от точки ввОДа пРобы ДО ные с выхода блока 6 памяти поступают на максимУма пика хРоматогРафической зоны. вход 49 блока 7. Сигналы с выхода блока 7 55 ЗастепеньотклонениЯ отсимметричнопоступают на блок 8 индикации. сти хроматографического пика можно взять

При ycTaHoeKe e исходное состояние . КозффиЦиент КАс.

{фиг. 3) осуществляется инициализация не- Хроматографический процесс стремятОбходимых областей для запОминания дан „ся проводить В условиЯх, соответствУющих ных, счетчиков и регистров состояния, линейной области изотермы сорбции, кО1718227 торой отвечают симметричные полосы компонентов(КАс=1). Определенные трудности, возникающие при ручном измерении Кдс (дрейф, наложение зон), не гарантируют высокую точность, поэтому не найдены данные по погрешности для сравнения точности измерения КАс с предлагаемым устройством.

В таблице приводятся погрешности из десяти измерений полуширины (AH) и Кдс для кривых Гаусса с различными соотношениями амплитуд (входной сигнал для измерения получен на имитаторе хроматографических сигналов с практически идеальной воспроизводимостью).

Блоки алгоритма устройства (фиг. 3): блок 1 формирует код с АЦП и счетчик времени, блок 2 сравнивает счетчик числа снятых данных сзаданным,,блок 3 — сравнения счетчика времени с заданным временем работы, блок 4 регистрирует результаты работы на ИЖК, блоки 5, 7, 9 и 12 формируют буферные массивы для расчетов соответственно данных первой, второй и третьей производных, блоки 6, 8 и 11 осуществляют расчет по формуле Савицкого соответственно первой, второй и третьей производных, блок 10 переписывает данные из буфера в регистр ЦАП, блок 13 анализирует регистр состояния системы, поиск начала, максимума или конца пика, блоки 14 и 22 — блоки регистрации начала пика и установки состо-. яния поиска максимума пика, блок 15 — блок регистрации максимума пика, блок 16 производит контроль полуширины, блок 17— установка поиска конца пика, блок 18- блок регистрации конца пика, блок 19 производит контроль полуширины, блок 20 производит расчет амплитуды с записью в ОЗУ необходимой информации для дальнейшего расчета,.блок 21 — блок установки поиска начала пика, блок 23 осуществляет регистрацию результатов, блок 14 производит расчет полуши рины и коэффициента асимметрии пика с регистрацией. результатов на ИЖК.

Программа работает с частотой таймерных прерываний, генератор осуществляет сьем данных с АЦП 13, формирует счетчик времени, суммирует снятые в сумматоре и увеличивает счетчик числа снятых данных.

Далее блок 2 сравнивает этот счетчик с заданным значением и от знака сравнения переходит либо к блоку 1, либо к блоку 3, который в зависимости от сравнения с заданным временем работы счетчика времени переходит либо к блоку 4, осуществляющему регистрацию результатов, либо переходит на формирование массива суммируемых данных.

10. буфер результата и необходимой информа25 ции для расчета по соотношениям (2) и (3).

Далее по сформированному массиву блок 6 осуществляет расчет по формуЛе Савицкого, блок 7 формирует массив производных, блок 8 рассчитывает вторую производную, с последующим формированием в блоке 9 массива двух производных.

Блок 1 осуществляет вывод данного в регистр ЦАП. Блок 11 рассчитывает аналогично третью производную, а блок 12— соответствующий массив.

Анализ состояния в блоке 13 передает управление ветке поиска начала (блок 14) с последующим запоминанием необходимых для блоков 4 и 23 значений и установкой (блок 22) признака поиска максимума с возвратам к блоку 1 или по ветке из блоков

15 — 17, регистрирующих соответственно время максимума пика, проверкой условий сброса, состояния регистра состояния в нуль, установкой (блок 17) поиска конца (блок 18), просверки условий сброса регистра состояния в начало (блока 19), расчет амплитуды сигнала по формуле (1) с занесением в

После установки регистра состояния в поиск начала пика (21) — переход к блоку 1.

Далее работа циклически повторяется до времени окончания работы блока 3 и переходит к блоку 4 — регистрации на ИЖК результатов. Блок 3 осуществляет расчет по формулам (2) и (3) из буфера результатов значений полуширины и коэффициента асимметрии уже не в темпе реального времени.

Для визуального контроля корректности вычислений входного сигнала обработанный сигнал может быть зарегистрирован на внешнем самописце. Это становится возможным с введением регистра 67 и ЦАП 68.

При этом управляющий сигнал с выхода 20 вычислительного блока поступает на вход

53 выборки селектора С 12. Адрес ЦАП с выхода регистра адреса поступает на адресный вход 56 селектора внешних устройств, Под действием управляющего сигнала с выхода 22 вычислительного блока 3, который поступает на вход 55 селектора 12, на выходе 65 формируется сигнал, который поступает на вход 66 регистра 67 и стробирует запись выводимого кода. Записанный код с выхода регистра 67 поступает на цифровые входы ЦАП 68, где преобразуется в выходное напряжение.

ЦАП позволяет в темпе реального времени, используя при необходимости согласующий делитель, производить регистрацию обработанного аналогового сигнала на внешнем самописце типа КСП-4 или другом аналогичном регистраторе, а также может быть

1718227

10 использован для управления в темпе реального времени внешним объектом.

Формула изобретения

Устройство для проверки хроматогра- фических колонок по авт.св. t4 1608638, о тл и ч аю щ ее с я тем, что, с целью расширения функциональных возможностей путем определения отклонения параметров 10 колонки от.идеальных значений, в него дополнительно введены цифроаналоговый преобразователь и регистр, информационный вход которого подключен через шину, к информационному выходу вычислительного блока, управляющий вход регистра соединен с соответствующим входом селектора, выход регистра — с входом цифроанало гового преобразователя, выход которого являет- ся информационным выходом устройства.

1718227 а.

Фиг3

Составитель B.Àâäîíè÷eâ

Техред М.Моргентал Корректор С. Ш евкун

Редактор И.Шулла

Заказ 883 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101