Цифровой коррелятор сигналов различной доплеровской частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной и вычислительной технике и может быть использовано для измерения функции взаимной корреляции между двумя случайными процессами, задержанными один относительно другого. Цель изобретения повышение быстродействия и расширение диапазона обзора по частоте Доплера. Коррелятор содержит аналого-цифровые преобразователи 12, блок аналого-цифровых преобразователей 8, делитель 24-27 частоты , генератор 34 тактовых импульсов, элементы И 13-17, четыре блоха элементов И 10-12, блок перемножителей 22, блок накопителей 29, блок 3 задержки, триггеры 35- 36, блоки элементов ИЛИ 20-21, блок делителей 28 частоты, элементы 32. 33 за держки, регистры 4,5. блок 30 определение максимального значения, дешифратор 31, узел блоков 19 памяти, блок 23 синхронизации . 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si)s G 06 F 15/336

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ КЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4836178/24 (22) 07.06,90 (46} 07.03.92.Бюл. ¹ 9 (72) Н.К.Бондарь, В.А.Маркитанов, И.И.Обод и И.Н.Попатенко (53} 681.3 (088.8) (55} Авторское свидетельство СССР № 1571612, кл, G 06 F 15/336, 1988. (54) ЦИФРОВОЙ КОРРЕЛЯТОР СИГНАЛОВ

РАЗЛИЧНОЙ ДОПЛЕPOBCKÎA ЧАСТОТЫ (57) Изобретение относится к измерительной и вычислительной технике и может быть использовано для измерения функции взаимной корреляции между двумя случайны-" ми процессами, задержанными один относительно другого. Цель изобретения—

„, Ы,, 1718231 А1 повышение быстродействия и расширение диапазона обзора по частоте Даплера. Коррелятор содержит аналого-цифровые преобразователи 12, блок аналого-цифровых преобразователей 8, делитель 24-27 частоты, генератор 34 тактовых импульсов, элементы И 13 — 17, четыре блока элементов И

10 — 12, блок перемножителей 22, блок накопителей 29, блок 3 задержки, триггеры 35—

36, блоки элементов ИЛИ 20-21, блок делителей 28 частоты, -элементы 32, 33 задержки, регистры 4, 5, блок 30 опоеделения максимального значения, дешифратор 3 t, .узел блоков 19 памяти, блок 23 синхронизации, 4 ил.

1718231

50

Изобретение относится к измерительной и вычислительной технике и может быть использовано для измерения функции взаимной корреляции между двумя случайными процессами, задержанными один относительно другого, Целью изобретения является увеличе-. ние быстродействия и расширение диапазона обзора по частоте Доплера.

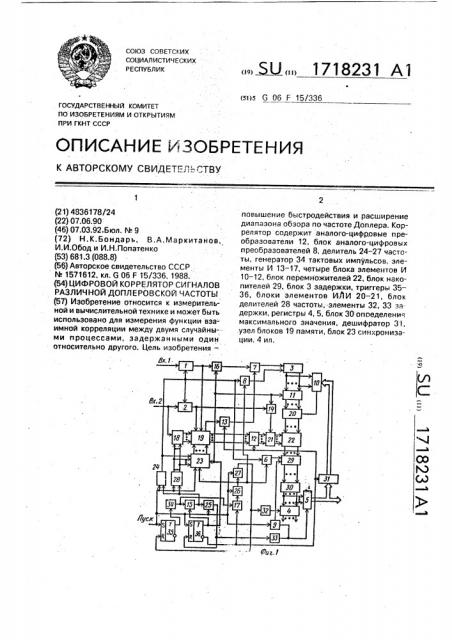

На фиг. 1 приведена структурная схема коррелятора; на фиг. 2 — структурная схема блока синхронизаторов; на фиг. 3 — структурная схема синхронизатора; на фиг, 4— временные диаграммы работы коррелято.ра.

Коррелятор (фиг. 1) содержит аналогоцифровые преобразователи (АЦП) 1 и 2, блок 3 задержки, регистры 4 и 5, элементы

ИЛИ 6-9, блоки 10-12 элементов И, элементы 13-17, блок АЦП 18, узел блоков 19 памяти, блоки элементов ИЛИ 20 и 21, блок перемножителей 22, блок 23 синхронизации, делители 24-27 частоты, блок делителей 28 частоты, блок накопителей 29, блок

30 определения максимального значения, дешифратор 31, элементы 32 и 33 задержки, генератор 34 тактовых импульсов, триггеры

35 и 36.

Блок 23 синхронизации (фиг. 2) содержит M синхронизаторов 37. Синхронизаторы 37 (фиг, 3) содержат элементы И 38 и 39, элементы ИЛИ 40-41, счетчик 42, делитель

43 частоты и триггер 44.

Коррелятор работает следующим образом.

В исходном состоянии триггеры 35 и 36 находятся в нулевом состоянии. При поступлении импульса запуска на вход коррелятора производится обнуление делителей

24 — 27, блока делителей 28, установка в начальное состояние блока синхронизаторов

23, а также установка триггера 35 в единичное состояние (фиг. 46) и триггера 36 в единичное состояние (фиг. 4в). Этот же импульс проходит через элемент ИЛИ 9 и производит обнуление блока накопителей 29.

Установка триггера 35 в единичное состояние разрешает работу генератора тактовых импульсов, который формирует на своем выходе импульсы тактовой частоты, установка триггера 36 в единичное состояние — работу элементов И 15, 16 и 14 и блока элементов И 11. Высокое напряжение с прямого выхода триггера 36 поступает на третий вход блока 23, который в этом состоянии формирует импульсы управления записью информации в узел блоков 19 памяти. Импульсы тактовой частоты с выхода генератора тактовых импульсов проходят через открытый элемент И 15 и поступают на входы делителей 24 и 25 и блока делителей 28.

На выходе делителя 24 получаются.импульсы квантования с периодом следования, выбранным в соответствии с правилом

Котельникова. На выходе блока делителей

28 получаются импульсы квантования, размноженные за счет того, что коэффициенты деления делителей разные.

Импульсы квантования с выхода делителя 24 поступают на синхровходы АЦП 1 и

2, в которых аналоговые напряжения, поступающие на вход коррелятора, преобразуют- . ся в цифровой код, Цифровые отсчеты с выхода АЦП 1 проходят через открытый элемент И 16, элемент ИЛИ 7 и поступают на блок 3 задержки, число отводов которого равно К, где К вЂ” число вычисляемых ординат взаимной корреляционной функции.

Одновременно с этим цифровые отсчеты с выходов АЦП 1 и 2 по импульсам квантования с выхода делителя 24, .а также цифровые отсчеты с выхода блока АЦП 18 по импульсам квантования блока делителей 28 записываются в узел блоков 19 памяти по импульсам блока 23 синхронизации. Цифровые отсчеты с выходов блока 3 задержки проходят через открытый блок элементов И

11, блок элементов ИЛИ 20 и поступают на входы блока 22, Цифровые отсчеты с выходов второго АЦП 2 проходят через открытый элемент И 14, блок элементов ИЛИ 21 на другие входы блока 22. В умножителях блока перемножителей 22 происходит перемножение входных отсчетов, Результаты перемножения поступают. в блок накопителей 29, где производится накопление результатов перемножения.

При появлении импульса на выходе делителя 25 (фиг. 4г), который определяет время накопления, триггер 36 устанавливается в нулевое состояние (фиг. 4в). Импульс с выхода делителя 25 задерживается в элементе 33 задержки на время срабатывания блока 30. Блок 30 анализирует выходные коды блока накопителей 29 и определяет код накопителя с максимальным значением.

Этот код выделяется на выходе блока 30 и поступает на входы регистров.

Импульс с выхода элемента 33 задержки поступаег на синхровход регистра 5 записывает код с выхода блока 30 в регистр 5.

Этот код поступает на выход коррелятора и несет информацию о времени задержки принимаемых сигналов. Код с выхода регистра 5 дешифруется дешифратором 31, на выходе которого появляется высокий потенциал на той шине, которая определяет номер канала блока 3 задержки, номер

5 .-1.7.18231 которого несет информацию о времени за:» держки. Дешифратор 31 работает толко, при поступлении на синхровход разрецаю:: щего потенциала. В остальных случаях-;ма всех выходах дешифратора 31 нулевьге :..5 уровни.

Таким образом, в блоке элементов И 1О открывается тот элемент, который опреде-: ляет номер канала выбранной задержки,, Цифровые отсчеты этого канала задержки, 10 регистра 3 через открытый элемент И блбка . элементов И 10 поступают на все первые входы умножителей 22 через блок элемен-." тов ИЛИ 20.

В связи с тем; что триггер 36 находитея,15 в нулевом состоянии, открываются третийблок элементов И 12 и элементы И 13 и 17:, В первом цикле работы коррелятора происходит размножение принимаемых сигналов по сетке частот дискретизации и эти пол- 20 ученные цифровые отсчеты записываются. в .. узел блоков.19 памяти. Во втором цикле, так . как триггер 36 находится в нулевом состоя-: нии, на вход блока синхронизаторов 23 по- .. ступает низкий потенциал. Это определяет:- 25 работу узла блоков памяти в режиме считы.= вания информации. Импульс с выхода элемента 33 задержки проходит, кроме всего,: через элемент ИЛИ 9 и обнуляет блоки накопителей 29. Цифровые отсчеты с первого 30 выхода узла блоков 19 памяти проходят через открытый элемент И 13,. элемент ИЛИ 7 и поступают на вход блока 3 задержки, цифровые отсчеты с выбранного в первом цикле . отвода которого проходят через блок элемен- 35 тов И 10, блок элементов ИЛИ 20 и поступают на входы блока перемножителей 22. Цифро- . вые отсчеты с группы выходов узла 19 проходят через открытый блок элементов И 12, блок элементов ИЛИ 21 и поступают на входы бло- 40 ка перемножителей 22.

Во втором цикле синхронизации считывания, сдвига и накопления работа осуще-. ствляется по импульсам делителя 26, на вход которого поступают импульсы с гене-.45 ратора 34 тактовых импульсов через открытый во втором цикле элемент И 17. В умножителях блока перемножителей 22 происходит перемножение поступающих цифровых отсчетов и результат перемноже- 50. ния поступает на блок накопителей 29. В блоке накопителей 29 происходит накопление результата и вычисление взаимной корреляционной функции с размножением по частоте Доплера в выбранной на первом 55 цикле временной точке. При появлении импульсов на выходе делителя 27 (фиг. 4е), а он определяет время работы во втором цикле и его коэффициент деления равен коэффициенту деления делителя 25, триггер 35 устанавливается в нулевое состояние {фиг, 46) и импульс, задержавшись в элементе 32 задержки на время срабатывания блока 30, поступает на синхровход регистра 4, обеспечивая этим запись.кода номера ординаты

ВКФ. с максимальным значением, код которой вычисляется в.блоке 30. Этот код, хара ктеризующий смещение по частоте Доплера, с выхода регистра 4 выделяется на выход коррелятора.

Таким образом,. в результате двух циклов вычисления взаимной корреляционной функции осуществляется вычисление и времени эадержки,.и частоты Доплера. В дальнейшем работа цифрового, коррелятора аналогична.

Блок 23 синхронизации содержит M синхронизаторов, где M — число блоков памяти в узле 19, Таким образом, каждый синхронизатор синхронизирует работу своего блока памяти. При поступлении импульса на вход обнуления триггер 44 устанавливается в единичное состояние и обнуляются делитель 43 и счетчик 42. Установление триггера

44 в единичное состояние разрешает работу элемента И 38, в результате чего импульсы квантования проходят через этот. элемент и элемент ИЛИ 40 и поступают на счетный вход счетчика 42, с выхода которого снимается код, подаваемый на адресный вход блока памяти в узле 19. Так как в режиме записи на входе управления записью — высокое напряжение, то элемент И 39.открыт, в результате импульсы квантования. с выхода элемента И 38 проходят через элемент И 39 и выделяются на синхровходе записи, поступают на синхровход записи блока памяти и по этим импульсам осуществляется запись информации в блок памяти. При появлении импульса на выходе делителя 43, а коэффициент деления этого делителя выбирается равным объему выборки, триггер 44 устанавливается в нулевое состояние. Одновременно с этим импульс с выхода делителя 43 проходит через элемент ИЛИ 41 и обнуляет счетчик 42.

При переключении режима работы коррелятора во второй цикл на входе исчезает высокое напряжение. Отрицательный перепад состояния вызывает то, что элемент И 39 закрывается, В этом случае импульсы, поступающие на другой вход, проходят через элемент ИЛИ 40 и поступают на счетный вход счетчика 42. В результате код счетчика 42, т,е, код адреса блока памяти, изменяется, а импульс записи, так как элемент И 39 закрыт, не формируется. Следовательно, в этом цикле осуществляется считывание информации с блока памяти. В дальнейшем работа синхронизатора аналогична.

1718231

20

Формула изобретения

Цифровой коррелятор сигналов различной доплеровской частоты, содержащий два аналого-цифровых преобразователя, два регистра, блок задержки, два элемента

ИЛИ, три блока элементов И, три элемента

И, блок аналого-цифровых преобразователей, два блока элементов ИЛИ, блок пере-. множителей, два делителя частоты, блок делителей частоты, блок накопителей, блок определения максимального значения, дешифратор, два элемента задержки, генератор тактовых импульсов, два триггера, причем информационный вход первого аналого-цифрового преобразователя является первым информационным входом коррелятора, информационный вход второго аналого-цифрового преобразователя соединен с информационным входом блока аналогоцифровых преобразователей и является вторым информационным входом коррелятора, синхровход первого аналого-цифрового преобразователя соединен с выходом первого делителя частоты, с первым входом первого элемента ИЛИ и с синхровходом второго аналого-цифрового преобразователя, выход которого соединен с первым входом первого элемента И, синхровходы группы блока аналого-цифровых преобразователей соединены с соответствующими выходами группы блока делителей частоты, вход установки в "0" которого соединен с. входом установки в "0" первого делителя частоты, с входами установки в "1" первого и второго триггеров, с входом обнуления второго делителя частоты, с первым входом второго элемента ИЛИ и является входом запуска коррелятора, информационный вход блока делителей частоты соединен с информационным входами первого и второго делителей частоты и с выходом второго элемента И, первый вход которого соединен с прямым выходом второго триггера, вторым входом первого элемента И и с управляющим входом первого блока элементов И, второй вход второго элемента И соединен с выходом генератора тактовых импульсов, вход запуска которого соединен с прямым выходом первого триггера, выход первого элемента задержки соединен с синхровходом первого регистра, выход которого является выходом значения разности доплеровских частот сигналов коррелятора, информационный вход первого регистра соединен с выходом блока определения максимального значения и с информационным входом второго регистра, синхровход которого соединен с вторым входом второго элемента ИЛИ и с выходом второго элемента задержки, выход второго регистра соединен с входом

55 дешифратора и является выходом значения времени задержки между сигналами коррелятора, синхровход дешифратора соединен с инверсным выходам второго триггера, с первым входом третьего элемента И, с управляющим входом второго блока элементов И, выход дешифратора соединен с управляющим входом третьего блока элементов И, информационные входы группы которого соединены с соответствующими выходами группы блока задержки и с соответствующими информационными входами группы первого блока элементов И, выходы группы которого соединены с соответствующими входами группы первого блока элементов ИЛИ, вход которого соединен с выходом третьего блока элементов И, а выходы группы блока элементов И вЂ” с соответствующими входами первой группы блока перемножителей, выходы группы которого соед. нены с соответствующими входами группы блока накопителей, входы второй группы блока перемножителей соединены с соответствующими выходами группы второго блока элементов ИЛИ, вход которого соединен с выходом первого элемента И, входы. группы второго блока элементов И соединены с соответствующими выходами группы второго блока элементов И, выход второго делителя частоты — с входом установки в "0" второго триггера и с входом первого элемента задержки, входы группы блока опоеделения максимального значения соединены с соответствующими выходами группы блока накопителей, вход обнуления которого соединен с выходом второго элемента ИЛИ, синхровход блока накопителей соединен .с выходом третьего элемента ИЛИ, отличающийся тем, что, с целью увеличения быстродействия и расширения диапазона обзора по частоте

Доплера, в него дополнительно введены узел блоков памяти, два элемента ИЛИ, два элемента И, две делителя частоты и блок синхронизации, вход установки в начальное состояние которого подключен к входу запуска коррелятора, выход первого делителя частоты — с тактовым входом блока синхронизации, группа тактовых входов которого соединена с группой выходов блока делителей частоты, вход задания режима работы блока синхронизации — с прямым выходом второго триггера и с первым входом четвертого элемента И, второй вход которого соединен с первым информационным входом узла блоков памяти и с выходом первого аналого-цифрового преобразователя, выход четвертого элемента И соединен с первым входом четвертого элемента ИЛИ, второй вход и выход которого соединены соответ17.182.31

10 ственно с выходом ретьего элемента И и.с информационным входом блока задержки, синхровход которого соединен с выходом: первого элемента ИЛИ, второй вход которо-. го соединен с первым входом третьего эле- 5 мента ИЛИ, с синхровходом блока синхронизаций, с выходом третьего делителя частоты и с входом четвертого делителя частоты, выход которого соединен с входом первого элемента задержки и с входом 10 установки "0" первого триггера, вход обнуления четвертого делителя часто-: ты соединен с входом обнуления третьего .: делителя частоты, информационный вход: которого соединен с выходом пятого эле- 15 мента И, первый вход которого соединен с инверсным выходом второго триггера, второй вход пятого элемента И вЂ” с выходом генератора тактовых импульсов, группа выходов блока синхронизации -с группой адресных входов узла блоков памяти, выход которого соединен с вторым входом третьего элемента И, группа. выходов узла блоков памяти — с группой входов второго блока элементов И, второй информационный вход и группа информационных входов узла памяти соединены соответственно с выходом второго аналою-:цифрового преобразователя и с группой выходов блока аналогоцифровых преобразователей.

1718231

Составитель В,Орлов

Техред M.Mîðãåíòàë

Редактор И. Шулла

Корректор В.Гирняк

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 883 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5