Цифровой синтезатор частотно-модулированных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - расширение частотного диапазона и увеличение длительности импульсов формируемых частотно-модулированных сигналов. Цифровой синтезатор частотно-модулированных сигналов содержит формирователь 1 управляющих сигналов , задающий генератор 2, умножитель 3 частоты, делитель 4 частоты с переменным коэффициентом деления, двоичный счетчик 5, первый коммутатор 6, второй коммутатор 7, блок 8 постоянной памяти, первый блок 9 управляемых инверторов (Б УП). второй Б УП 10, инвертор 11, первый буферный регистр 12, второй буферный регистр 13, первый цифроаналоговый преобразователь (ЦАП) 14, второй ЦАГ1 15. блок 16 полосовых фильтров, третий коммутатор 17, четвертый коммутатор 18, при этом формирователь 1 содержит генератор 19 импульсов, счетчик 20, формирователь 21 импульсов, блок 22 памяти и регистр 23 памяти. Обеспечивается формирование последовательности различных сигналов с программным изме нением их видов и параметров. Формирование каждого из сигналов осуществляется в несколько этапов. 1 з.п. ф-лы, 3 ил, /

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 Н 03 В 23/00

ГОСУДАРСТВЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ли

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4723903/09 (22) 24.07.89 (46) 15.03.92. Бюл. М 10 (72) Н.В. Горшков, С.А. Иванов и Ю,Мв РомаН0В (53) 621.373.42 (088.8) (56) Кочемасов В.Н, и др. Формирование сигналов с линейной частотной модуляцией. — M. Радио и связь, 1983, с. 55.

Авторское свидетельство СССР

ЬЬ 1552345, кл. Н 03 В 23/00, 16.05.88. (54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ (57) Изобретение относится к радиотехнике.

Цель изобретения — расширение частотного диапазона .и увеличение длительности импульсов формируемых частотно-модулированных сигналов. Цифровой синтезатор частотно-модулированных сигналов содержит формирователь 1 управляющих сигна5LJ 1720144 A l лов, задающий генератор 2, умножитель 3 частоты, делитель 4 частоты с переменным коэффициентом деления, двоичный счетчик

5, первый коммутатор 6, второй коммутатор

7, блок 8 постоянной памяти, первый блок 9 управляемых инверторов (Б УП), второй Б

УП 10, инвертор 11, первый буферный регистр 12, второй буферный регистр 13,. первый цифроаналоговый преобразователь (ЦАП) 14, второй ЦАП 15, блок 16 полосовых фильтров, третий коммутатор 17, четвертый коммутатор 18, при этом формирователь 1 содержит генератор 19 импульсов. счетчик

20, формирователь 21 импульсов, блок 22 памяти и регистр 23 памяти, Обеспечивается формирование последовательности различных сигналов с программным измео нением их видов и параметров. Формирование каждого ив сигналов осущвствллвтсл в вгтрк несколько этапов. 1 э.п. ф-лы, 3 ил, 1720144

10

50

Изобретение относится к радиотехнике и может быть использовано в радиопередающих устройствах.

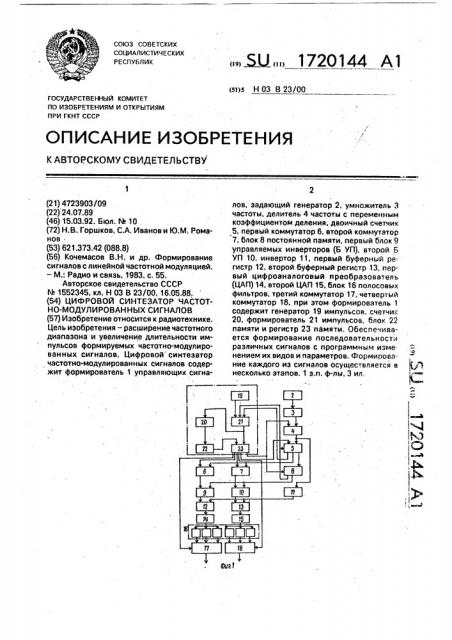

Целью изобретения является расширение частотного диапазона и увеличение длительности ипульсов формируемых частотно-модулированных сигналов. .На фиг.1 представлена структурная электрическая схема цифрового синтезатора частотно-модулированных сигналов; на фиг.2 — спектры дискретных линейно-частотно-модулированных сигналов и закон изменения выходного сигнала на первом выходе цифрового синтезатора частотно-модулированных сигналов; на фиг,3 — спектры дискретных линейно-частотно-модулированных сигналов и закон изменения выходного сигнала на втором выходе цифрового синтезатора частотно-модулированных сигналов.

Цифровой синтезатор частотно-модулированных сигналов содержит формирователь 1 управляющих сигналов, задающий генератор 2, умножитель 3 частоты, делитель 4 частоты с переменным коэффициентом деления, двоичный счетчик 5, первый коммутатор 6, второй коммутатор 7, блок 8 постоянной памяти (БПП), первый блок 9 управляемых инверторов (БУИ), второй

БУИ 10, инвертор 11, первый буферный регистр 12, второй буферный регистр 13, первый цифроаналоговый преобразователь (ЦАП) 14, второй ЦАП 15, блок 16 полосовых фильтров (БПФ), третий коммутатор 17, четвертый коммутатор 18. При этом формирователь 1 содержит генератор 19 импульсов, счетчик 20, формирователь 21 импульсов, блок 22 памяти и регистр 23 памяти.

Цифровой синтезатор частотно-модулированных сигналов работает следующим образом.

Цифровой синтезатор частотно-модулированных сигналов обеспечивает формирование последовательности различных сигналов с программным изменением их видов и параметров. Формирование каждого из сигналов осуществляется в несколько этапов. Формирователь 1 обеспечивает заданную последовательность работы.

Рассмотрим режим работы, при котором одновременно формируются два линейно-частотно-модулированных сигнала (ЛЧМ) с одинаковыми значениями центральной частоты, девиации и длительности, но различными знаками скорости частотной модуляции. -Формирование данных сигналов осуществляется в пять этапов.

В исходном состоянии двоичный счетчик 5 удерживается в нулевом состоянии сигналом.с третьего выхода формирователя

1. Сигнал с третьего выхода формирователя

1 представляет собой двухразрядный параллельный двоичный код, формируемый уровнями напряжений логических единиц третьего выхода регистра 23 памяти, Поступая с третьего выхода формирователя 1 на управляющий вход двоичного счетчика 5, двухразрядный параллельный .двоичный код, состоящий из двух единиц, переводит двоичный счетчик 5 в режим параллельного приема информации по информационным входам. Поскольку на информационные входы двоичного счетчика 5 постоянно поданы уровни напряжений логического нуля (на фиг.1 не показано), то двоичный счетчик 5 удерживается в нулевом состоянии. При этом на вход двоичного счетчика 5 постоянно поступает последовательность тактовых импульсов с выхода делителя 4. Формирование ЛЧМ сигналов начинается в момент поступления импульса положительной полярности с выхода генератора 19 импульсов на первый вход формирователя 21 импульсов. Под действием этого импульса на выходе формирователя 21 импульсов формируется короткий синхроимпульс, который поступает на вход синхронизации регистра 23 памяти и на счетный вход счетчика

20. Для простоты описания будем считать. что счетчик 20 находится, например, в нулевом состоянии. Под действием короткого синхроимпульса с выхода формирователя

21 импульсов в регистр 23 памяти осуществляется запись информации, хранящейся по нулевому адресу блока 22 памяти. Одновременно этот синхроимпульс увеличивает на единицу содержимое счетчика 20, и на вход блока 22 памяти поступает новый двоичный код с выхода счетчика 20, что приводит к появлению на выходе блока 22 памяти информации, хранящейся по первому адресу блока 22 памяти. Таким образом, на выходах регистра 23 памяти и формирователя 1 формируется набор управляющих сигналов и начинается первый этап формирования

ЛЧМ сигналов. При этом на входе регистра

23 памяти сформирован набор управляющих сигналов для второго этапа работы устройства.

На первом этапе с первого выхода формирователя 1 на управляющий вход первого коммутатора 6 поступает напряжение уровня логического нуля и на выходе первого коммутатора 6 формируется постоянный уровень напряжения логического нуля независимо от уровня сигнала на входе первого коммутатора 6. С второго выхода формирователя 1 на управляющий вход второго коммутатора 7 поступает напряжение уровня логического нуля, которое запрещает прохождение сигналов с входа на выход второ1720144 го коммутатора 7. На выходе второго коммутатора 7 удерживается уровень напряжения логического нуля независимо от изменения сигнала на его входе (аналогично первому коммутатору 6). С третьего выхода формирователя 1 параллельный двухразрядный двоичный код (младший разряд имеет уровень логического нуля, старший — логической единицы) поступает на управляющий вход двоичного счетчика 5 и переводит его в режим суммирования числа импульсов, поступающих на вход двоичного счетчика 5 с выхода делителя 4, С четвертого выхода формирователя 1 уровень напряжения логического нуля поступает на управляющий вход делителя 4 и задает коэффициент деления, равный двум, обеспечивающий предельно допустимую для устройства максимальную величину тактовой частоты, которая ограничивается быстродействием двоичного счетчика 5 и БПП 8.

Кроме того, уровень напряжения логического нуля с четвертого выхода формирователя

1 поступает на второй вход БПП 8 и определяет обращение на первом этапе к младшей половине БПП 8, поскольку вторым входом

БПП 8 является вход старшего разряда адреса. С пятого выхода формирователя 1 па.раллельный двоичный трехразрядный позиционный код (младший разряд имеет уровень логической единицы, остальные разряды — уровень логического нуля) поступает на управляющий вход третьего коммутатора 17 и подключает первый выход БПФ

16 на выход третьего коммутатора 17. С шестого выхода формирователя 1 параллельный двоичный трехразрядный позиционный код (старший разряд имеет уровень логической единицы, остальные разряды — уровень логического нуля) поступает на управляющий вход четвертого коммутатора 18 и подключает шестой выход БПФ 16 на выход четвертого коммутатора 18. Высокостабильная тактовая частота с выхода задающего генератора 2 поступает на вход умножителя

3, который умножает величину тактовой частоты до необходимого значения fT. С выхода умножителя 3 тактовая частота fv поступает на вход делителя 4, который делит тактовую частоту в два раза. Полученная

В РЕЗУЛЬтатЕ ДЕЛЕНИЯ таКтОВаЯ ЧаСтата Гт1 =

fT/2 поступает на входы двоичного счетчика

5 и инвертора 11. Кроме того, уровень напряжения логического нуля с четвертого выхода формирователя 1 поступает на второй вход БПП 8 и определяет обращение на первом этапе к младшей половине БПП 8 постоянной памяти, поскольку вторым входом

БПП 8 является вход старшего разряда адреса. Длительность г1 первого этапа определяется разрядностью и двоичного счетчика 5 и величиной тактовой частоты f, с выхода делителя 4 т1- 2 / т1 — N/fò1 — NT>, где N — емкость двоичного счетчика 5;

Т1 — величина периода тактовой частоты

10 f,1, Под действием тактовой частоты содержимое двоичного счетчика 5 на первом этапе изменяется от 0 до N-1. Выходы всех разрядов двоичного счетчика 5 образуют

15 первый выход двоичного счетчика 5, который подключен к первому входу БПП 8. Первый вход ДПП 8 образован всеми разрядами адреса, кроме старшего. Выход самого младшего разряда двоичного счетчика 5 об20 разует его второй выход. Третьим выходом двоичного счетчика 5 является выход импульса переноса. Уровень напряжения логического нуля с третьего выхода двоичного счетчика 5 через первый вход формирова25 теля 1 поступает на второй вход формирователя 21 импульсов, и не изменяет его состояния. Меандровое колебание частотой fry /2 с второго выхода двоичного счетчика 5 поступает.на входы первого б и

30 второго 7 коммутаторов, Линейно нарастающая последовательность кодов от 0 до N-1 с первого выхода двоичного счетчика 5 используется для адресации БПП 8, в котором с нулевого по N-1-й адрес записаны двоич35 ные коды амплитудных отсчетов ЛЧМ сигнала Х(гТ1), частота которого за время тт изменяется от значения начальной частоты

fH дО 1т1/4 (фИГ.2а). ДВОИЧНЫЕ КадЫ аМПЛИтудных отсчетов вычислеНы заранее с шагом дискретизации Т1, равным периоду тактовой частоты fT1. На второй вход БПП 8, образованный входом старшего разряда адреса, поступает уровень напряжения логического нуля с четвертого выхода форми45 рователя 1, Первый выход БПП 8 образован всеми выходными разрядами выходного кода БПП 8, кроме двух старших разрядов, Два старших разряда выходного кода БПП 8 образуют его второй выход, Коды амплитуд50 ных отсчетов ЛЧМ сигнала не используют два старших выходных разряда БПП 8, которые выполняют служебные .функции, т,е. разрядность по выходу БПП 8 определяется количеством разрядов, необходимых для

55 представления кодов амплитудных отсчетов

ЛЧМ сигнала с заданной точностью, и двумя дополнительными старшими разрядами, выполняющими служебные функции. Коды амплитудных отсчетов ЛЧМ сигнала X(rT>) с

1720144

20

30

55 первого выхода БПП 8 поступают на вторые входы первого и второго БУИ 9 и 10. Поскольку на их первые входы поступают уровни напряжений логического нуля с выходов первого и второго коммутаторов 6 и 7 соответственно, то коды амплитудных отсчетов

ЛЧМ сигнала X(rT> ) с первого выхода БПП

8 без изменения проходят через первый и второй БУИ 9 и 10 и поступают на входы первого и второго буферных регистров 12 и

13 соответственно. Последовательность тактовых импульсов с выхода делителя 4 проходит через инвертор 11 и поступает на входы синхронизации первого и второго буферных регистров 12 и 13, Под действием последовательности тактовых импульсов двоичные коды амплитудных отсчетов ЛЧМ сигнала Х(гТ,) записываются в первый и второй буферные регистры 12 и 13 и появляются на их выходах. С выходов первого и второго буферных регистров 12 и 13 амплитудные коды отсчетов ЛЧМ сигнала поступают на входы первого и второго ЦАП 14 и 15, в которых происходит преобразование двоичных кодов в аналоговые величины. На выходах первого и второго ЦАП 14 и 15 формируются одинаковые дискретные ЛЧМ сигналы, которые поступают на первый и второй входы БПФ 16. Каждый вход БПФ 16 нагружен на три полосовых фильтра, амплитудно-частотные харатеристики которых показаны на фиг.2а,б. В спектре дискретного

ЛЧМ сигнала на выходах первого и второго

ЦАП 14 и 15 присутствуют спектральные составляющие, частоты которых изменяются от f> до f»/4 и от f> до 3f»/4. Тогда на первом и четвертом выходах БПФ 16 выделяется основная составляющая спектра дискретного ЛЧМ сигнала, частота которой изменяется от fH до f»/4 (фиг.2 а). На третьем и шестом выходах БПФ 16 полосовых фильтров выделяется спектральная составляющая дискретного ЛЧМ сигнала, частота которой изменяется от f> = f» — f> до 3f»/4 (фиг.3а). Управляющий сигнал с пятого выхода формирователя 1 подключает первый выход третьего коммутатора 17, который является первым выходом устройства. На первом выходе устройства формируется

ЛЧМ сигнал, частота которого изменяется от fg до f»/4, Управляющий сигнал с шесгого выхода формирователя 1 подключает шестой выход БПФ 16 на выход четвертого коммутатора 18, который является вторым выходом устройства. На втором выходе устройства формируется ЛЧМ сигнал, частота которого изменяется от f> до 3f»/4 (фиг.3a).

На первом этапе двоичный двухразрядный параллельный нулевой код второго выхода БПП 8 через второй вход формирователя 1 поступает на третий вход формирователя 21 импульсов и не изменяет его состояния, Кроме того, двоичный двухразрядный параллельный нулевой код с второго выхода БПП 8 поступает на вход предварительной установки двоичного счетчика 5 и не оказывает влияния на его работу. Управляющий вход и вход предварительной установки двоичного счетчика 5 подключены к одной и той же точке внутренней структуры двоичного счетчика 5, а именно к входу управления режимами работы двоичного счетчика 5. Поскольку такое подключение образует логи ку M О Н ТАЖ Н ОЕ

ИЛИ, то нулевой код на входе предварительной установки двоичного счетчика 5 не оказывает влияния на его работу. Режим работы двоичного счетчика 5 определяется кодом на управляющем входе двоичного счетчика 5.

Второй этап формирования выходных .ЛЧМ сигналов начинается в момент переполнения двоичного счетчика 5, когда его содержимое достигает значения N-1..На третьем выходе двоичного счетчика 5 формируется импульс переполнения положительной полярности, который через первый вход формирователя 1 поступает на второй вход формирователя 21 импульсов.

Под действием данного импульса на его выходе появляется короткий синхроимпульс, с помощью которого в регистр 23 памяти заносится содержимое блока 22 памяти по первому адресу, а к содержимому счетчика 20 добавляется единица, и оно становится pBBHblM двум. Изменение содержимого счетчика 20 приводит к тому, что на входы регистра 23 памяти поступает информация, хранящаяся в блоке 22 памяти по второму адресу и представляющая собой набор управляющих сигналов для третьего этапа формирования выходных ЛЧМ сигналов. Таким образом, на выходах регистра 23 памяти и на выходах формирователя

1 формируется набор управляющих сигналов и осуществляется второй этап формирования выходных ЛЧМ сигналов, Процесс перехода к второму этапу происходит за один такт работы устройства, т.е. по времени меньше периода тактовой частоты. С первого и второго выходов формирователя 1 на управляющие входы первого и второго коммутаторов 6 и 7 поступают напряжения уровней логических единиц, в результате чего на выходах первого и второго коммутаторов.б и 7 формируется информация, инверсная выходной. С третьего выхода формирователя i параллельный двухраэрядный двоичный код(младший разряд имеет уровень логической единицы, старший—

1720144

10 логического нуля) поступает на управляю- инвертирование каждого второго двоичного щий вход двоичногo счетчика 5 и переводит кода амплитудных отсчетов ЛЧМ сигнала его в режим вычитания. С четвертого выхода Х(гТ)). Сформированные последовательноформирователя 1 уровень напряжения логи- сти кодов с выхода первого и второго БУИ 9 ческого нуля продолжает поступать на уп- 5 и 10 фиксируются в первом и втором буферравляющий вход делителя 4, обеспечивая ных регистрах 12 и 13 соответственно, котокоэффициентделения, равныйдвум,атакже рые тактируются проинвентированной на второй вход БПП 8, обеспечивая считы- последовательностью импульсов частоты 1т вание информации из младшей половины, поступающей с выхода инвертора 11 на их блока БПП 8. С пятого выхода формировате- 10 входы синхронизации. С выходов первого и ля 1 параллельный двоичный трехразряд- второго буферных регистров 12 и 13 двоичный позиционный код (младший разряд ныекодыамплитудныхотсчетовЛЧМсигнаимеетуровеньлогическойедини,осталь- ла поступают на входы первого и второго ные разряды — уровень логического нуля) ЦАП 14 и 15 соответственно. На выходах поступает на управляющий вход третьего 15 первого и второго ЦАП14и15формируются коммутатора 17 и подключает первый выход одинаковые дискретные ЛЧМ сигналы. ПоБПФ 16 на выход третьего коммутатора 17. скольку считывание кодов из БПП 8 провоС шестого выхода формирователя 1 парал- дится в обратном порядке, то частота лельный двоичный трехразрядный позици- основной спектральной составляющей форонный код (старший разряд имеет уровень 20 мируемых ЛЧМ сигналов X(IT)) должна мелогической единицы, остальные разряды — няться от fT)/4 до fH. Однако в первом и уровень логического нуля) поступает íà уп- втором БУИ 9 и 10 осуществляется инвертиравляющий вход четвертого коммутатора рование каждого второго двоичного кода

18 и подключает шестой выход БПФ 16 на амплитудных отсчетов формируемых ЛЧМ выход четвертого коммутатора 18. Такта- 25 сигналов Х(гТ)), что приводит к инверсии вая частота f)) = fT/2 с выхода делителя 4 спектров формируемых ЛЧМ сигналов поступает на входы двоичного счетчика 5 и инвертора 11. 8 инверторе 11 происхо- т (12)г g) Х (!2 М(0,5 q, — FJ ) дит инвертирование последовательности тактовых импульсов частоты fT). Поскольку 30 То есть закон изменения частоты ЛЧМ двоичный счетчик 5 находится в режиме вы- сигнала Y(rT)) будет зеркальным отображечитания, то под действием тактовых импуль- нием закона изменения частоть| ЛЧМ сигнасов его содержимое изменяется от N-2 до О. ла Х(гТ)) относительно частоты fT)/4, и

При этом уровень напряжения логического частота основной спектральной составляюнуля с третьего выхода двоичного счетчика 35 щей формируемых ЛЧМ сигналов изменяет5 через первый вход формирователя 1 по-, ся от fT)/4 до f8) (фиг,2б). Кроме того, в ступает на второй вход формирователя 21 спектре дискретных ЛЧМ сигналов íà выхоимпульсов и не оказывает влияния на дах первого и второго ЦАП 14 и 15 присутего работу. Уменьшающееся от N-2 до 0 ствует спектральная составляющая, частота содержимое двоичного счетчика 5 поступа- 40 которой изменяется от 3 f>)/4 до fBç(фиг.Зб). ет с его выхода на вход БПП 8 и использу- Указанная спектральная составляющая выется для адресации. В соответствии с деляется натретьем и шестом выходах БПФ изменяющимися адресами из БПП 8 в об- 16. Управляющий сигнал с пятого выхода ратном порядке (по отношению к первому формирователя 1 подключает первый выход этапу) считываются двоичные коды ампли- 45 БПФ 1.6 на выход третьего коммутатора 17. тудных отсчетов ЛЧМ.сигнала Х(гТ)), Меан- Таким образом, во время второго этапа на дровое колебание частотой 1т /2 с второго первом выходе устройства формируется выхода двоичного счетчика 5 поступает на Л4М сигнал, частота которого изменяется входы первого и второго коммутаторов 6 и от fT)/4 до 41 Управляющий сигнал с шес7. Поскольку на управляющие входы перво- 50 того выхода формирователя 1 подключает го и второго коммутаторов 6 и 7 поступают шестой выход БПФ 16 на выход четвертого разрешающие потенциалы с первого и вто- коммутатора 18. Таким образом. во. время рого выходов формирователя 1, то меандро- второго этапа на втором выходе устройства вые колебания частотой 1т)/2 проходят формируется ЛЧМ сигнал, частота которого через первый и второй коммутаторы 6 и 7, 55 изменяется от 3f))/4 до 4з. Длительность инвертируются в них и поступают на входы второго этапа г2 на один период тактовой первого и второго БУИ 9 и 10соответствен- частоты Т) = 1/fT) меньше длительности но. первого этапа, поскольку на втором этапе

Под действием импульсов меандрового . опрашивается тот же объем БПП 8, эа искколебания частоты fr)/2 в них происходит лючением самого старшего адреса N-1.

1720144

Таким образом, на первом и втором этапах за Bp8MR z1 + z2 = z1 + z1 — T1 = 2 z1 — Т на первом выходе устройства формируется

ЛЧМ сигнал, частота которого изменяется от f< до 41, а на втором выходе — ЛЧМ сигнал, частота которого изменяется от 4 до

43.

Непрерывность фазы формируемых

ЛЧМ сигналов в момент перехода от первого этапа к второму обеспечивается инвертированием в первом и втором коммутаторах

6 и 7 меандровой последовательности тактОВЫХ ИМПУЛЬСОВ Чаотатсй 1т1/2, ПОСтУПаЮщих с второго выхода двоичного счетчика 5.

В этом случае будет проинвентирован каждый второй двоичный код амплитудных отсчетов формируемых ЛЧМ сигналов, начиная с кода, который записан по адресу

N-2, и будет обеспечена непрерывность фазы формируемых ЛЧМ сигналов. На фиг.За показаны величины кодов амплитудных отсчетов, считанные по соответствующим адресам из БПП 8. При этом по достижении адреса N-1 показано обратное изменение адресов обращения к БПП 8 и инвертирование каждого второго кода амплитудных отсчетов, начиная с записанного по адресу

N-2. На фиг,Зб показано соответствующее изменение напряжения на выходе второго

ЦАП 15. Можно наблюдать непрерывность фазы формируемого сигнала. На втором этапе двоичный двухразрядный параллельный нулевой код с второго выхода БПП 8 через второй вход формирователя 1 поступает на третий вход формирователя 21 импульсов и не изменяет его состояния, Кроме того, двоичный двухразрядный параллельный код с второго выхода БПП 8 поступает на вход предварительной установки двоичного счетчика 5 и не оказывает влияния на его

pc360ò, Третий этап формирования выходных

ЛЧМ сигналов начинается в момент переполнения двоичного счетчика 5, когда его содержимое в режиме вычитания достигает нулевого значения. На третьем выходе двоичного счетчика 5 формируется импульс переполнения положительной полярности, который через первый вход формирователя 1 сигналов поступает на второй вход формирователя 21 импульсов. Под действием данного импульса на его выходе формируется короткий синхроимпульс, который поступает на вход синхронизации регистра 23 памяти и на счетный вход счетчика 20. Вследствие этого в регистр 23 памяти заносится содержимое блока 22 памяти по второму адресу, а к содержимому счетчика 20 добавляется единица, и оно

20 становится равным трем. Изменение содержимого счетчика 20 приводит к тому, что на вход регистра 23 паяти поступает ийформация, хранящаяся в блоке 22 памяти по третьему адресу. На выходах регистра 23 памяти и на выходах формирователя 1 сформирован двоичный код, представляющий собой набор управляющих сигналов для третьего этапа формирования ЛЧМ сигналов. Процесс перехода к третьему этапу работы устройства также не превышает во времени одного периода тактовой частоты 41. С первого выхода формирователя 1 на управляющий вход первого коммутатора 6 поступает напряжение уровня логической единицы, которое разрешает прохождение и инвентирование информации с входа на выход первого коммутатора 6. С второго выхода формирователя 1 на управляющий вход второго коммутатора 7 поступает напряжение уровня логического нуля, которое запрещает прохождение информации с входа на выход второго коммутатора 7.

С третьего выхода формирователя 1 параллельный двухразрядный двоичный код

25 (младший разряд имеет уровень логического нуля, старший — логической единицы) поступает на управляющий вход двоичного счетчика 5 и переводит его в режим суммирования. С четвертого выхода формирователя 1

30 уровень напряжения логической единицы поступает на управляющий вход делителя .

4, обеспечивая коэффициент деления, равный трем, Таким образом, на выходе делителя

4 начинает формироваться последовательность

35 тактовых импульсов частотой f< = f3.>

40 и шестого выходов формирователя 1 одинаковые параллельные двоичные трехразрядные позиционные коды(средний разрядимеетуровень логической единицы, остальные разряды — уровень логического нуля) поступают на уп45 равляющие входы третьего и четвертого коммутаторов 17 и 18 и подключают второй и пятый выходы БПФ 16 к выходам третьего и . четвертого коммутаторов 17 и 18 соответственно. Тактовая частота fa с выхода делите50 ля 4 поступает на входы двоичного счетчика 5 и инвертора 11. В инверторе 11 осуществляется инвертирование последовательности тактовых импульсов частоты fa. Поскольку двоичный счетчик 5 находится в режиме сум55 миррвания, то его содержимое начинает, увеличиваться и используется для адресации БПП 8.с адреса Nu обеспечивается уровнем напряжения логической единицы, поступающим с четвертого выхода формирователя 1 на второй вход БПП 8, В

1720144

БПП 8 с адреса N to адрес N+M записаны двоичные коды амплитудных отсчетов ЛЧМ сигнала P(rTz), вычисленные с шагом дискретизации Т, равным периоду тактовой частоты fa. Тогда длительность третьего 5 этапа составит тз= (М+1) Т, где {М+1)— количество кодов амплитудных отсчетов

ЛЧМ сигнала P(rTz), М < N. 3a время кз частота ЛЧМ сигнала P(rTz) изменяется от f„z до 1а. Уровень напряжения логического ну- 10 ля с третьего выхода двоичного счетчика 5 и двухразрядный двоичный нулевой код с второго выхода БПП 8 поступают через первый и второй входы формирователя 1 на второй и третий входы формирователя 21 импуль- 15 сов соответственно, не изменяя его состояния. Коды амплитудных отсчетов ЛЧМ сигнала с выхода БПП 8 поступают на второй вход второго БУИ 10, на первый вход которого поступает уровень напряжения ло- 20 гического нуля с выхода второго коммутатора 7. Коды амплитудных отсчетов ЛЧМ сигнала с выхода БПП 8 без изменения проходят через второй БУИ 10 и фиксируются во втором буферном регистре 13. Запись 25 указанных кодов во второй буферный регистр 13 осуществляется проинвентированНой последовательностью тактовых импульсов частотой fa, поступающей с выхода инвертора 11 на вход синхронизации 30 второго буферного регистра 13, С выхода второго буферного регистра 13 последовательность кодов амплитудных отсчетов поступает на вход второго ЦАП 15, в котором преобразуется в дискретный ЛЧМ сигнал. 35

Спектр дискретного ЛЧМ сигнала на выходе второго ЦАП 15 содержит спектральные составляющие, частоты которых изменяются от f 2 до fez и от 4з до 41 (фиг,Зв). Дискретный ЛЧМ сигнал с выхода второго ЦАП 15 40 поступает на второй вход БПФ 16. На его четвертом выходе выделяется спектральная составляющая, частота которой изменяется от f z до fez. На пятом выходе выделяется спектральня составляющая, частота кото- 45 рой изменяется от 4з до f». Управляющий сигнал с шестого выхода формирователя 1 поступает на управляющий вход четвертого коммутатора 18 и подключает пятый выход

БПФ 16 к выходу четвертого коммутатора 50

18. Таким образом, в течение длительности третьего этапа а на втором выходе.устройства формируется ЛЧМ сигнал, частота

КОТОРОГО ИЗМЕНЯЕТСЯ От fe3 ДО fe1 (фИГ.ЗВ).

Кроме того, коды амплитудных отсчетов 55

ЛЧМ сигнала с выхода БПП 8 поступают на . второй вход первого БУИ 9. на первый вход которого поступает проинвертированная в первом коммутаторе 6 меандровая последовательность, импульсов частотой fez/2 с торого выхода двоичного счетчика 5. Под де:..,ствием указанной последовательности импульсов в первом БУИ 9 осуществлч:тся инвентирование каждого второго k,çäà амплитудных отсчетов ЛЧМ сигнала

Преобразованная таким образом последовательность кодов поступает на вход первого буфернбго регистра 12, запись в который осуществляется проинвертированной последовательностью тактовых импульсов частотой fa, которая поступает с выхода инвертора 11, С выхода первого буферного регистра 12 преобразованная последовательность кодов амплитудных отсчетов поступает на вход первого ЦАП 14. Дискретный ЛЧМ сигнал с его выхода поступает на первый вход БПФ 16. Инвертирование каждого второго кода амплитудных отсчетов

ЛЧМ сигнала р(гТ2) приводит к эффекту инверсии спектров и формированию ЛЧМ сигнала, спектр которого описывается выражением

То есть закон изменения частоты сигнала В(гТ2) будет зеркальным отображением закона изменения частоты сигнала р(гТ ) 0 гносительно частоты fa/4, Таким образом, спектр дискретного ЛЧМ сигнала на выходе первого ЦАП 14 содержит спектральные составляющие, частоты которых изменяются от fez до fez и от f et до 4з (фиг.2в). На первом выходе БПФ 16 выделяется спектральная составляющая, частота которой изменяется от fez äî fHz, а на втором выходе — спектральная составляющая, частота которой изменяется от fel до 43. Управляющий сигнал с пятого выхода формирователя 1 поступает на управляющий вход третьего коммутатора

17 и подключает второй выход БПФ 16 к его выходу. В течение длительности третьего этапа хз на первом выходе устройства формируется ЛЧМ. сигнал, частота которого изменяется от fe1 до fe3 (фиг.2в). Таким сбразом, в течение длительности првых трех этапов7>+tz+ss на первом выходеустройства формируется ЛЧМ сигнал, частота которого изменяется от fe до 4з, а на втором выходе устройства — ЛЧМ сигнал, частота которого изменяется от 4 до fe1. Отсутствие разрыва по частоте при переходе к третьему этапу формирования ЛЧМ сигналов и возможность использования на третьем этапе эффекта инверсии спектров обеспечивается выбором соответствующих величин тактовых частот fT1 и fez. Поскольку1т1 = fT/2, 15

1720144

5

45

55 а f 2 = f /3, то можно записать fT = 21т1, т = 3f r, Приравняв правые части выражений, получим 2f > 31т2, э отсюда 1т1/2 - 3 /4.

Таким образом, с использованием эффекта инверсии спектров на третьем этапе формируются ЛЧМ сигналы с центральной частотой ЗФт2/4. В то же время центральная частота формируемых ЛЧМ сигналов равна

f»/2, что обеспечивает переход из подспектра в подспектр без разрыва по частоте.

Конкретная девиация частоты формируемых на третьем этапе ЛЧМ сигналов определяется требованиями к условиям фильтрации парциальных ЛЧМ импульсов на втором и четвертом этапах. Непрерывность фазы формируемых ЛЧМ сигналов при переходе к третьему этапу обеспечивается расчетом и записью в старшую половину БПП 8 двоичных кодов амплитудных отсчетов ЛЧМ сигнала Р (гТр) с начальной и конечной фазами, соответствующими конечным фазам ЛЧМ сигналов, формируемых на втором этапе., Четвертый этап формирования выходных ЛЧМ сигналов начинается в момент формирования в двоичном счетчике 5 кода

N+M+1. В БПП 8 по адресу М+М+1-записан код, два старших разряда которого равны единицам. Таким образом, в момент формирования в двоичном счетчике 5 кода Й+М+1 на выходе БПП 8 формируется двоичный код, два старших разряда которого равны единицам. Двоичный двухразрядный код с второго выхода БПП 8 поступает на вход предварительной установки двоичного счетчика 5 и переводит его в режим параллельного приема информации по информационным входам. Поскольку на информационные входы двоичного счетчика 5 постоянно поданы уровни напряжений логического нуля (на фиг.13 не показано), то двоичный счетчик 5 переходит в нулевое состояние. Кроме того, двоичный код, состоящий иэ двух единиц, с второго выхода БПП

8 через второй вход формирователя 1 поступает на третий вход формирователя 21 импульсов. Под действием данного кода на его выходе формируется короткий: синхроимпульс, который поступает на вход синхронизации регистра 23 памяти и на счетный вход счетчика 20. Вследствие этого в регистр 23 памяти заносится содержимое блока 22 памяти по третьему адресу, и к содержимому счетчика 20 добавляется единица, и оно становится равным четырем.

Изменение содержимого счетчика 20 приводит к тому, что на вход регистра 23 памяти поступает информация, хранящаяся в блоке

22 памяти по четвертому адресу, На выходах регистра 23 памяти и на выходах формирователя 1 сформирован двоичный код, представляющий собой набор управляющих сигналов для четвертого этапа формирования ЛЧМ сигналов. Процесс перехода к четвертому этапу работы устройства также не превышает по времени одного периода тактовой частоты f>i. С первого и второго выходов формирователя 1 на управляющие входы первого и второго коммутаторов 6 и 7 поступают напряжения уровней-логических единиц, которые разрешают прохождение и инвертирование информации с входа на выход первого и второго коммутаторов 6 и 7.

С третьего выхода формирователя 1 параллельный двухраэрядный двоичный код (младший разряд имеет уровень логического нуля, старший — уровень логической единицы) поступает на управляющий вход двоичного счетчика 5 и удерживает его в режиме суммирования. С четвертого выхода формирователя 1 уровень напряжения логи.ческого нуля поступает на управляющий вход делителя 4. обеспечивая коэффициент деления равным двум. Таким образом; на выходе делителя 4 начинает формироваться последовательность тактовых импульсов с частотой f>i = f>/2. Кроме того, напряжение логического нуля с четвертого выхода формирователя 1 поступает на второй вход БПП

8, обеспечивая выборку кодов амплитудных отсчетов X(rT>) из младшей половины БПП 8.

C пятого выхода формирователя 1 параллельный двоичный трехразрядный позиционный код (старший разряд имеет уровень логической единицы. остальные разряды— уровень логического нуля) поступает на управляющий вход третьего коммутатора 17 и подключает третий выход БПП 16 к выходу третьего коммутатора 17. С шестого выхода формирователя 1 параллельный двоичный трехразрядный позиционный код (младший разряд имеет уровень логической единицы, остальные разряды — уровень логического нуля) поступает на управляющий вход четвертого коммутатора 18 и подключает четвертый выход БПФ 16 к выходу четвертого коммутатора 18. Тактовая частота f 1 = fr/2 с выхода делителя 4 поступает на вход двоичного счетчике 5 и инвертора 11. Поскольку двоичный счетчик 5 находится в режиме суммирования, то под действием тактовых импульсов частотой fr>, поступающих с выхода делителя 4, содержимое двоичного счетчика 5 изменяется на четвертом этапе от 0 до N-1. При этом на выходе БПП 8 формируется та же последовательность кодов амплитудных отсчетов ЛЧМ сигнала

X(rTi), что и на первом этапе. Коды амплитудных отсчетов ЛЧМ сигнала с nepaoro вы17

1720144 хода БПП 8 поступают на вторые входы первого и второго БУИ 9 и 10, Меандровое колебание частотой f»/2 с второго выхода двоичного счетчика 5 поступает на входы первого и второго коммутаторов 6 и 7. Поскольку на управляющие входы первого 6 и второго 7 коммутаторов поступают разрешающие потенциалы с первого и второго выходов формирователя 1, то меандровые колебания частотой f» проходят через первый и второй коммутаторы 6 и 7, инвертируются и поступают на входы первого и второго БУИ 9 и 10 соответственно, где просходит инвертирование каждого второго двоичного кода амплитудных отсчетов

ЛЧМ сигнала Х(гТ1). Сформированные последовательности кодов Y(rT1) с выхода первого и второго БУИ 9 и 10 фиксируются в первом и втором буферных регистрах 12 и