Мажоритарный элемент

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении управляющих систем. Цель изобретения - упрощение мажоритарного элемента. Элемент содержит инвертор 2, логический элемент 5, входы 10-12, выход 13. Введение в состав мажоритарного элемента инвертора, выполненного на КМОП транзисторах 3 и 4, причем сопротивление открытых транзисторов 3 и 4 в. 2(К-1) раз превышает сопротивление открытого транзистора логического элемента 5, где К - отношение напряжения питания к напряжению порога, и позволяет при разных значениях сигналов на 10 и 11 входах мажоритарного элемента установить его выход 13 по значению на входе 12. 1 ил.

СО103 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 03 К 19/23

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

11 (21) 4758100/21 (22) 10.11.89 (46) 15.03.92. Бюл. % 10 (71} Ленинградский электротехнический институт им. В.И.Ульянова (Ленина) (72) В.И.Варшавский, А,Ю,Кондратьев, В.А.Романовский, Б.С.Цирлин (53) 621.374 (088.8} (56) Авторское свидетельство СССР

Ф 993479, кл. Н 03 К 19/23, 1983. (54) МАЖОРИТАРНЫЙ ЭЛЕМЕНТ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении управляющих

„„5U „„1720154 А1 систем, Цель изобретения — упрощение мажоритарного элемента. Элемент содержит инвертор 2, логический элемент 5, входы

10-12, выход 13. Введение в состав ма>коритарного элемента инвертора, выполненного на КМОП транзисторах 3 и 4, причем сопротивление открытых транзйсторов 3 и 4 s

2(К-1) раз превышает сопротивление открытого транзистора логического элемента 5, где К вЂ” отношение напряжения питания к напряжению порога, и позволяет при разных значениях сигналов на 10 и 11 входах мажоритарного элемента установить его выход 13 по значению на входе 12. 1 ил.

1720154

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении управляющих систем.

Известен мажоритарный элемент, содержащий элемент И-ИЛИ-НЕ, причем первый вход мажоритарного элемента соединен с первыми входами первой и второй групп И элемента И-ИЛИ-НЕ, второй вход — с вторыми входами второй и третьей групп И элемента И-ИЛИ-НЕ; третий вход— с вторым и первым входами первой и третьей групп И элемента И-ИЛИ-НЕ соответственно, а выход мажоритарного элемента соединен с выходом элемента

И-ИЛИ-Н Е.

Недостатком известного мажоритарного элемента является избыточность оборудования, так как при его реализации на

КМОП транзисторах требуется 10 транзисторов.

Наиболее близким к предлагаемому является мажоритарный элемент, состоящий из первого логического элемента, выполненного на двух МОП транзисторах и-типа и двух МОП транзисторах р-типа, и второго логического элемента, выполненного на трех МОП транзисторах и-типа и трех МОП транзисторах р-типа, причем в каждом логическом элементе сток и исток первого MOfl транзистора р-типа соединены с шиной питания и истоком второго МОП транзистора р-типа, исток и сток первого МОП транзистора и-типа соединены соответственно с общей шиной и истоком второго МОП транзистора п-типа, сток которого соединен с истоком первого транзистора р-типа, во втором логическом элементе сток и исток третьего МОП транзистора р-типа соединены с истоком первого транзистора р-типа и стоком третьего транзистора п-типа, исток которого соединен со стоком первого транзистора и-типа того >ке элемента, первый вход мажоритарного элемента соединен с затворами первых транзисторов fl- и р-типов обоих логических элементов, второй вход — с затворами вторых транзисторов пи р-типа первого логического элемента и затворами третьих транзисторов и- и р-типов второго, третий вход — с затворами вторых транзисторов и- и р-типов второго логического элемента, выход мажоритарного элемента соединен со стоками первых транзисторов и-типа обоих логических элементов, а также со стоком третьего транзистора. л типа второго логического элемента.

Недостатком данного мажоритарного элемента является избыточность оборудования, поскольку его реализация требует 10

М ОП транзисторов.

45 шиной питания и стоком транзистора 7 р-ти50

55 нен с выходом логического элемента 5 и выходом 13 мажоритарного элемента 1, 5

Цель изобретения — упрощение мажоритарного элемента, Указанная цель достигается тем, что в мажоритарном элементе, состоя щем из инвертора и логического элемента, выполненного на двух МОП транзисторах и-типа и двух МОП транзисторах р-типа, в логическом элементе исток и сток второго транзистора р-типа соединены соответственно с шиной питания и истоком первого транзистора р-типа, исток и сток второго транзистора и-типа соединены соответственно с общей шиной и истоком первого транзистора п-типа, сток которого соединен со стоком первого транзистора р-типа и выходом логического элемента, первый вход мажоритарного элемента соединен с затворами первых транзисторов и- и р-типов логического элемента, второй вход — с затворами вторых транзисторов и- и р-типов логического элемента, а третий вход — с входом инвертора, выход мажоритарного элемента соединен с выходом инвертора и логического элемента, причем сопротивление открытого транзистора инвертора превышает сопротивление открытого транзистора логического элемента более чем в 2(k-1) раз, где k — отношение напряжения питания к напряжению порога, Введение в состав мажоритарного элемента инвертора, выполненного на МОП транзисторах с повышенным сопротивлением, позволяет при разных значениях на первом и втором входах мажоритарного элемента установить его выход по значению на третьем входе, в результате чего достигается упрощение элемента.

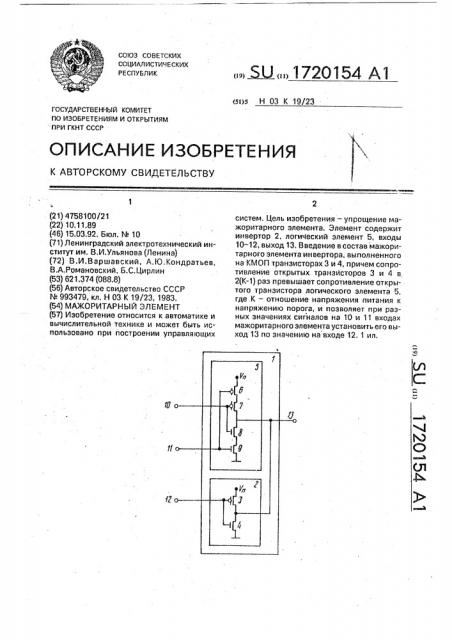

На чертеже приведена схема предлагаемого мажоритарного элемента.

Мажоритарный элемент 1 содержит инвертор 2, выполненный на МОП транзисторе р-типа 3 и и-типа 4, и логический элемент

5, выполненный на МОП транзисторах 6 и 7 р-типа и 8 и 9 и-типа. Сток и исток транзистора 6 р-типа соединены соответственно с па, исток и сток транзистора 9 и-типа соединены соответственно с общей шиной и истоком транзистора 8 п-типа, сток которого соединен с истоком транзистора 7 р-типа и выходом логического элемента 5. Вход 10 мажоритарного элемента 1 соединен с затворами транзисторов 7 и 8, вход 11 — с затворами транзисторов 6 и 9, вход 12 — с входом инвертора 2, выход которого соедиМажоритарный элемент работает следующим образом.

1720154

Составитель Н.Деубровская

Редактор Ю.Середа Техред M.Ìîðãåíòàë Корректор Q.Кундрик

Заказ 777 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Если на входах 10 и 11 логические значения 00 (11), то транзисторы 6 и 7 открыты (закрыты), а транзисторы 8 и 9 закрыты (открыты). Тогда при выбранном соЬтношении между сопротивлением R открытого транзистора инвертора 2 и сопротивлением г от- 5 крытого транзистора логического элемента

5(R >2(k-1)г, где k =Чи(Чу, Vn напряжение питания; VT — пороговое напряжение) на выходе 19 будет значение логической единицы (нуля) вне зависимости от значения на входе 10

12..Если значения на входах 10 и 11 противоположны, то закрыт один из транзисторов

6 и 7 и закрыт один из транзисторов 8 и 9, тем самым значение на выходе 13 определяется значением на входе 12 и будет равно 15 единице, если на входе 12 — логический нуль, и нулю, если на входе 12 — единица.

Так например, при напряжении питания 5В и пороге 1В отношение сопротивлений транзисторов 8 и 9 и 3 или 6, 7 и 4 20 составит соответственно 1:8; Если на входах 10 и 11 имеются зна«ения "1" (открыты транзисторы 8 и 9), а на входе 12 — "0" (открыт транзистор 3), то образуется делитель напряжения из двух транзисторов 8 и 25

9 и транзистора 3, при этом, исходя из указанного соотношения сопротивлений этих транзисторов. напряжение на выходе 13 составит 1В, т.е. напряжение логического нуля, В противоположном случае(на входах 10 30 и 11 сигналы "0", а на входе 12 — "1") напряжение будет соответствовать 4В, т,е. напряжение логической единицы. Заметим, что, увеличивая отношение сопротивлений указанных транзисторов {например 1:10), мы 35 еще больше приблизим напряжения на выходе 13 к идеальным значениям логического нуля и единицы соответственно. Заметим, кроме того, что, когда на входах 10 и 11 .значения сигналов различны, значение на выходе 13 определяется значением выхода инвертора 2, т.е. противоположно значению на входе 12 и при этом равно идеальному значению логического нуля или единицы соответственно.

Реализация предлагаемого мажоритарного элемента требует 6 МОП транзисторов против 10 МОП транзисторов в прототипе, т.е. достигнуто упрощение оборудования на

40/, Формула изобретения

Мажоритарный элемент, состоящ. из инвертора и логического элемента, г полненного на двух парах КМОП транзис оров и- и р-типов, в логическом элементе истоки вторых транзисторов р- и и-типов соединены соответственно с шиной питания и общей шиной, их стоки — с истоками первых транзисторов р- и п-типов, стоки которых соединены с выходами логического элемента, выходом инвертора и выходом мажоритарного элемента, первый вход которого соединен с затворами первых транзисторов р- и и-типов логического элемента, второй вход — с затворами вторых транзисторов ри и-типов логического элемента, а третий вход — с входом инвертора, о т л и ч а ю щ ий сятем,,что, с целью упрощения, сопротивление открытого транзистора р- и п-типа инвертора B 2(k-1) раз больше сопротивления открытого транзистора р- и и-типа логического элемента, где k — отношение напряжения питания к напряжению порога, а истоки транзисторов р- и и-типа инвертора подключены соответственно к шине питания и общей шине.