Устройство для приема четвертично-кодированных последовательностей

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и может найти применение в системах передачи информации, синхронизации и радиолокации . Целью изобретения является увеличение числа принимаемых последовательностей . Устройство содержит коммутатор , блоки задержки, демодулятор, многоотводную линию задержки, вычислитель , решающий блок, преобразователи импульсной последовательности и знакозадающий блок. На выходе решающего блока в процессе приема четвертичной последовательности формируется напряжение , пропорциональное автокорреляционной функции этой последовательности при условии, что по первым установочным входам знакозадающие блоки включены по номеру соответствующего D-кода, а по вторым установочным входам линия задержки и элементы задержки включены по номеру соответствующей функции Радемахера. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (!! ) (.)5 Н 04 1.27/26

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4798941/09 (22) 08.01.90 (46) 23.03.92. Бюл. М 11 (72) П.В.Гришин (53) 621.394.62(088.8) (56) WILSON R. RICHTER J. Generation and

perbormance of guadraphase Welti Codes bor

Radar and Sunohronization of Coherent and

Dlfberentially Coherent P.S.Ê. IEEE trans on

Communications, corn. 27, М9, 1979, Fig,4. (54) УСТРОЙСТВО ДЛЯ ПРИЕМА ЧЕТВЕРИЧНО-КОДИРОВАННЫХ ПОСЛЕДОВАТЕЛ Ь Н ОСТЕЙ (57) Изобретение относится к радиотехнике и может найти применение в системах передачи информации, синхронизации и радиолокации. Целью изобретения является

Изобретение относится к радиотехнике и может найти применение в системах передачи информации, синхронизации и радиолокации.

Целью изобретения является увеличение числа принимаемых последовательностей.

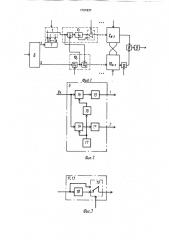

На фиг.1 изображена структурно-электрическая схема устройства; на фиг.2 — структурно-электрическая схема демодулятора; на фиг.3 — структурно-электрическая схема знакозадающего блока; на фиг.4 — эпюры напряжений, поясняющие работу устройства.

Устройство содержит коммутатор 1, блоки 2 задержки, каждый из которых содержит вычитатель 3, элемент 4 задержки и переключатель 5, демодулятор 6, многоотувеличение числа принимаемых последовательностей. Устройство содержит коммутатор, блоки задержки, демодулятор, многоотводную линию задержки, вычислитель, решающий блок, преобразователи импульсной последовательности и знакозадающий блок. На выходе решающего блока в процессе приема четвертичной последовательности формируется напряжение, пропорциональное автокорреляционной функции этой последовательности при условии, что по первым установочным входам знакозадающие блоки включены по номеру соответствующего D-кода, а по вторым установочным входам линия задержки и элементы задержки включены по номеру соответствующей функции Радемахера. 4 ил. водную линию 7 задержки, вычислитель 8, решающий блок 9 и преобразователи 10 импульсной последовательности, каждый из которых содержит знакозадающий блок 11 и сумматор 12, и знакозадающий блок 13, причем демодулятор 6 содержит два перемножителя 14, два фильтра 15, фазовращатель 16 на к/2 и генератор 17 опорных колебаний, а знакозадающие блоки 11 и 13 содержат инвертор 18 и переключатель 19.

Устройство работает следующим образом.

До приема четверично-кодированной (четверичной) последовательности по первым установочным входам устройства знакозадающие блоки 11 и 13 включаются в режим инвертирования или неинвертирования, поступающего на их вход напряжения, 1721837 согласно номеру D-кода, соответствующего принимаемой четверичной последовательности. По вторым установочным входам также до приема четверичной последовательности производится коммутация выходов многоотводной линии 7 задержки и элементов 4 задержки в соответствии с номером! функции Радемахера, соответствующего четверичной последовательности, по следующему правилу: а) номер коммутируемого коммутатора

1 входа определяется выражением

i- k — )+1; б) номера блоков 2 задержки, в которых переключатели 5 подключают к своему выходу дополнительный отвод соответствующих элементов 4 задержки, определяются с 1-го по (k - 1)-й.

Многоотводная линия 7 задержки выполнена так, что задержка в ее 1-м отводе равна (2 ) т(где i = 1,..., k — номер отвода, -длительность одного элемента принимаемой четверичной последовательности, которая содержит 2 элементов). В блоках 2 задержки элементы 4 задержки выполнены на (2 ) Т(где 1 = 1,..., k — 1 — номер блока задержки), задержка в дополнительном отводе соответствующего элемента задержки (2" ) t.

Вычислители 3 и 8 обеспечивают вычитание напряжения, поступающего на их второй вход из напряжения, поступающего на первый вход, При поступлении на вход демодулятора

6 четверичной последовательности (Е-кода) с алфавитом а, Р д, у на двух выходах демодулятора образуются троичные последовательности с алфавитом - 1,0 — 1 по следующему правилу;

0выы = 1; 0вых2 = О; если Е = а:

Овых1 = -1; UBblx2 = 0; если Е = Р;

0вых1 = 0; 0Вых2 = 1; ЕСЛИ Е! = д;

Овых1 = О; Овых2 = -1; если Ei = y, При этом последовательности активных элементов (1 и -1) на первом и втором выходах демодулятора 6 представляют собой дополнительные последовательности О-кода, образующего принимаемую четверичную последовательность. Частота чередования активных элементов одной и другой дополнительных последовательностей определяется номером j функции Радемахера.

Например, при j=k активные элементы одной дополнительной последовательности чередуются с активными элементами другой последовательности через один, а при

j=1 сначала следуют все активные элементы первой последовательности, а затем — все активные элементы второй последовательности (фиг.2а,б,в при k = 3).

Многоотводная линия 7 задержки и коммутатор 1 обеспечивают в соответствии с

5 номером j функции Радемахера совмещение по времени активных (-1 и 1) и пассивных (О) элементов дополнительных последовательностей, поступающих с обоих выходов демодулятора 6 (фиг.2в„г). Обе, по10 следовательности имеют по 2 активных элементов, Дополнительные последовательности в силу механизма их образования характерны тем, что половина их активных элементов

15 одинакова, а другая половина — противоположная по знаку. B преобразователе 101 импульсной последовательности энакозадающий блок 111 обеспечивает в соответствии с номером 0-кода синфазное сложение

20 в вычитателе 31 первых 2 2 активных элементов дополнительных последовательностей и взаимную компенсацию вторых 2 2 активных элементов этих дополнительных последовательностей. При этом в суммато25 ре 12> преобразователя 101 импульсной последовательности наоборот в фазе складываются вторые 2 активных элементов этих последовательностей, а первые 2" их активных элементов — взаимно компен30 сируются. В результате на выходах вычитателя 31 и сумматора 121 образуются новые дополнительные последовательности, но они содержат по 2 активных элемента в два раза больших по напряжению, чем эле35 менты исходных последовательностей (фиг.2д,е). Для этого примера выбран такой

D-код, для которого по первым установочным входам все знакозадающие блоки 11 и

13 включены в режим неинвертирования по

40 знаку напряжения, поступающего на их входы

Блок 21 задержки обеспечивает при помощи элементов 4> задержки и переключателя 5> вновь совмещение активных

45 элементов новых дополнительных последовательностей, которые после вычитания в вычитателе 32 и сложения в сумматоре 122 образуют новые дополнительные последовательности, содержащие по 2 активных

50 элемента уже в 4 раза больше по напряжению, чем элементы принимаемой четверичной последовательности (фиг.2ж,з) и так далее. На выходах последних блока 2 задержки и преобразователя 10 импульс55 ной последовательности дополнительные последовательности сжимаются до длительности одного активного элемента, а по напряжению становятся больше в 2 раз элементов принимаемой четверичной последовательности. Знакозадающий блок 13

1721837

15 л 3

2 г

55 обеспечивает в вычитателе 8 сложение в фазе двух импульсов напряжением 2 " каждый. На входе решающего блока 9 на протяжении времени в (2" )х после начала поступления на вход устройства четверичной последовательности напряжение будет отсутствовать, но по истечении этого времени появится импульс длительностью в t u напряжением в 2 раз больше амплитуды элемента четвертичной последовательности (фиг.2и).

Таким образом, на входе решающего блока 9 в процессе приема четверичной последовательности формируется напряжение, пропорциональное автокорреляционной функции этой последовательности при условии, что по первым установочным входам знакозадающие блоки включены по номеру соответствующего D -кода, а по вторым установочным входам линия задержки и элементы задержки включены по номеру соответствующей функции Радемахера.

Решающий блок 9 в простейшем случае является пороговым элементом. Коммутатор 1 в простейшем случае является переключателем, Демодулятор 6 может быть выполнен в виде когерентного демодулятора фазоманипулированных посылок. Если начальные фазы посылок принимаемых четверичных последовательностей будут равны то такой демодулятор обеспечивает разделение двух ортогональных последовательностей(а,P ) и(д, у).

Таким образом, устройство позволяет принимать в k раз больше различных четверично-кодированных последовательностей.

При установке по вторым установочным входам положений переключателей 5 и коммутатора 1 в позиции согласно функции Радемахера j = k устройство позволяет принимать все Е-коды. Следовательно, увеличение множества принимаемых устройством последовательностей позволяет расширить область его применения, например, его можно применять в системах передачи информации, где требуется высокая структурная скрытность используемых сигналов.

Формула изобретения

Устройство для приема четверично-кодированных последовательностей, содержащее последовательно соединенные волоки задержки, вычитатель и решающий блок и последовательно соединенные демодулятор, преобразователи импульсной последовательности и знакозадающий блок, выход которого подключен к второму входу вычитателя, первый и второй входы каждого блока задержки соединены с вторыми соответственно входом и выходом соответствующего преобразователя импульсной последовательности, причем каждый блок задержки выполнен в виде последовательно соединенных вычитателя и элемента задержки, при этом первый и второй входы вычитателя являются соответственно первым и вторым входами блока задержки, каждый преобразователь импульсной последовательности выполнен в виде последовательно соединенных знакозадающего блока и сумматора, второй вход и выход которого являются соответственно вторым входом и первым выходом преобразователя импульсной последовательности, первым и третьим входами и вторым выходом которого являются соответственно первый, второй входы и выход знакозадающего блока, вход демодулятора является информационным входом устройства, первыми установочными входами и выходом которого являются соответственно третьи входы преобразователей импульсных последовательностей и выход решающего блока, о т л и ч а ю щ е ес я тем, что, с целью увеличения числа принимаемых последовательностей, введены многоотводная линия задержки и коммутатор, причем второй выход демодулятора подключен к входу многоотводной линии задержки, выходы которой подключены к сигнальным входам коммутатора, выход которого подключен к первому входу первого блока задержки, а в каждый блок задержки введен переключатель, сигнальные входы которого соединены с выходами элемента задержки, управляющий вход и выход переключателя является соответственно третьим входом и первым выходом блока задержки, а управляющий вход коммутатора и третьи входы блока задержки являются вторыми установочными входами устройства.

1721837

° °

° °

° °

1721837

П1й б ими га д

Щй)

5г

12

Составитель О. Андрушко

Редактор В. Бугренкова Техред М.Моргентал Корректор M. Кучерявая

Заказ 965 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101