Устройство тактовой синхронизации и выделения пачки импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано для число-импульсного кодирования информации. Цель изобретения - расширение функциональных возможностей путем дополнительного формирования регулируемых пачек импульсов в заданном интервале асинхронного сигнала с одновременным формированием импульса регулируемой длительности -достигается введением JK-триггера 9 с задержкой срабатывания, третьего и четвертого элементов И-НЕ 10, 11, элемента И 12, шины 3 выбора режима, третьей и четвертой выходных шин Т5 и 16. Устройство также содержит шину 1 синхронизации, входную шину 2, шину 3 управления, инвертор 4, два D-триггера 5, 6, первый, второй элементы И-НЕ 7, 8. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (ss)s Н 03 К 5/13, 3/64

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 884106 (21) 4800000/21 (22) 11.01.90 (46) 30.03.92. Бюл. ¹ 12 (71) Всесоюзный научно-исследовательский институт оптико-физических измерений (72) Н.Д,Поршнева, В.И.Горшков и Е.К.Поршнев (53) 621.374(088.8) (56) 1. Авторское свидетельство СССР

¹884106,,кл. Н 03 К 5/13, P 03 К 3/64, 1980. (54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ И ВЫДЕЛЕНИЯ ПАЧКИ ИМПУЛЬСОВ (57) Изобретение относится к импульсной технике и может быть использовано для чисИзобретение относится к импульсной технике, в частности к формирователям, производящим временную привязку асинхронного сигнала в тактовой частоте и, кроме того. формирующим регулируемые серии импульсов в интервале длительности асинхронного сигнала, и может быть использовано для число-импульсного кодирования информации.

Известен формирователь серии импульсов, содержащий два триггера (1). Недостатком этого устройства является то, что у него нет выхода, на котором формируется первый синхронизированный импульс каждой пропускаемой серии импульсов.

Известно устройство тактовой синхронизации, содержащее два триггера и элемент совпадения, один вход которого

„„5U„„1723658 А2 ло-импульсного кодирования информации.

Цель изобретения — расширение функциональных возможностей путем дополнительного формирования регулируемых пачек импульсов в заданном интервале асинхронного сигнала с одновременным формированием импульса регулируемой длительности — достигается введением JK-триггера 9 с задержкой срабатывания, третьего и четвертого элементов И-НЕ 10, 11, элемента И

12, шины 3 выбора режима, третьей и четвертой выходных шин 15 и 16. Устройство также содержит шину 1 синхронизации, входную шину 2, шину 3 управления, инвер,ор 4, два D-триггера 5, 6, первый. второй элементы И-НЕ 7, 8. 2 ил. соединен с шиной синхронизации и с С-входом первого триггера, два других входа подключены к прямым выходам первого и второго триггеров, а выход соединен с выходом шиной и С-входом второго триггера, S-вход которого подключен к прямому выходу первого D-триггера, D-вход которого соединен с R-входом и с выходной шиной, а инверсный выход подключен к D-входу второго триггера

Недостатком известного устройства тактовой синхронизации является то, что оно не может формировать на выходе пачки им пул ьсов.

Наиболее близким к предлагаемому по технической сущности и схемному решению является. устройство тактовой синхронизации и выделения пачки импульсов, содержа1723658 щее входную шину, два триггера, два эле- шины, причем D âõoä первого триггера соемента И-НЕ и инвертор, вход которого сое- динен со входной шиной и с первым входом динен с шинои синхр и синхронизации и первыми третьего элемента И-НЕ через элемент входами первого и второгоэлементов И-НЕ, второй вход которого соединен с выходом выходы которых соедин соединены с первой и вто- 5 четвертого элемента И-НЕ, первый вход корой выходными шинами, соответственно, торого соединен с шиной выбора режима, выход инвертора подключен к счетному вхо- второй вход — с прямым выходом JK-триггеду первого D-триггера, прямой и инверсный ра с задержкой срабатывания, J-вход котосоответственно соедине- рого соединен с прямым выходом первого ны с установочным и информационным вхо- 10 триггера и с третьей выходной шиной, дами второго D-триггера, счетный вход вход — с инверсным выходом первого тригкоторого соединен с выходом второго эле- гера и с вторым входом третьего элемента мента И-НЕ, второй вход которого соединен И-НЕ, выход которого соединен с четвертой с вторым входом первого элемента И-НЕ, выходной шиной, третий вход — с шиной второй вход которого соединен с вторым 15 тактовых импульсов. входом первого элемента И-НЕ и прямым При этом J К-триггер с задержкой срабавыходом первого D-триггера, третий вход тываниясодержитВ$-триггер, первуюивтосоединен с прямым выходом 0-триггера, а рую регулируемые интегрируемые ЯС-цепи, информационный вход первого D-триггера каждая из которых состоит из последовасоединен с входной шиной, 20 тельно соединенных регулируемого резиНедостатком известного устройства стора и конденсатора, второй обкладкой тактовой синхронизации и выделения пачки соединенного с общей шиной, первый и втоимпульсов является невозможность регули- рой элементы И-НЕ, первые входы которых ровать число импульсов в и сов в пачке и формиро- являются входами J и К соответственно, а вать группы импульсов в интервале 25 выходы через первую и вторуюинтегрируюдлительности асинхр и асинхронного сигнала, что щие цепи соответственно соединены с устазначительно сужает его функциональные новочным и обнуляющим входами возможности. RS-триггера, прямой и инверсный выходы

Целью предлагаемого изобретения яв- которого соединены со вторыми входами ляется расширение функцион ф нкциональных воз- 30 второго и первого элементов И-НЕ соответможностей устройств стройства путем ственно, прямой вход RS-триггера является дополнительногоформирования регулируе- прямым выходом JK-триггера с задержкой мых пачек импульсов в заданном интервале срабатывания. асинхронного сигнала с одновременным Поскольку в данном устройстве по сравформированием импульса регулируемой 35 нению с известным техническим решением длительности. (в частности, с прототипом) имеются новые

Поставленная цель достигается тем, что признаки, то предложение удовлетворяет

II II в устройство тактовой синхронизации и вы- критерию новизна, деления пачки импульсов по авт.св. М Введенные JK-триггер с задержкой сра884106, содержащее шину синхронизации, 40 батывания, элемент совпадения и элементы входную шину, два D-триггера, два элемен- И-НЕ известны из цифровой техники и прита И-НЕиинвертор, входкоторогосоединен менены по своему назначению. Однако их с шиной синхронизации и первыми входами связь между собой и с остальными элеменпервого и второго элементов И-НЕ, выходы тами устройства позволяет значительно которых соединены с первой и второй вы- 45 расширить функциональные возможности ходными шинами соответственно, выход устройства. инвертора подключен к счетному входу пер- Устройство тактовой синхронизации и вого О-триггера, прямой и инверсный выхо- выделения пачки импульсов, принятое за ды которого соответственно соединены с прототип, позволяет формировать синхрониустановочным и информационным входами 50 зируемый импульс и пачку импульсов, соотвторого D-триггера, счетный вход которого ветствующую длительности асинхронного соединен с выходом второго элемента И- сигнала,апредлагаемоеустройствопозволяНЕ, второй вход которого соединен с вто- етформироватьсинхронизируемый импульс, рым входом первого элемента И-НЕ и регулируемую пачку импульсов в заданном прямым выходом первого D-триггера, тре- 55 интервале длительности асинхронного сигтий вход соединен с прямым выходом вто- нала, формировать регулируемые пачки имрого О-триггера, введены JK-триггер с пульсов в интервале длительности задержкой срабатывания, третий и четвер- асинхронного сигнала с одновременным тый элементы И-НЕ, элемент И, шина выбо- формированием синхронизируемого имра режима, третья и четвертая .выходные пульса, соответствующего началу каждой

1723658 пачки импульсов, а на третьей выходной шине устройство позволяет получить импульсы регулируемой длительности при формировании импульсов по переднему фронту асинхронного сигнала, а на четвертой выходной шине получить пачку импульсов, отстоящую от переднего фронта асинхронного сигнала на и+ 1 импульсов.

На момент подачи материалов заявки авторам не известна заявляемая схема устройства тактовой синхронизации и выделения пачки импульсов, обеспечивающая достижение поставленной цели, Поэтому предложение можно считать удовлетворяющим критерию "Существенные отличия".

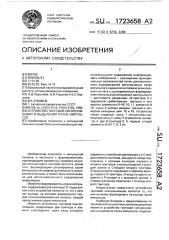

Схема устройства тактовой синхронизации и выделения пачки импульсов представлена на фиг. 1; на фиг. 2 дана диаграмма работы устройства.

Устройство тактовой синхронизации и выделения пачки импульсов содержит шину синхронизации 1, входную шину 2, шину 3 выбора режима, инвертор 4, два 0-триггера

5, 6, элементы И-HF 7, 8 JK-триггер 9, элементы И-НЕ 10, 11, элемент совпадения 12, выходные шины 13 — 16.

J К-триггер 9 с задержкой срабатывания содержит первый 17 и второй 18 элементы

И-НЕ, первую 19 и вторую 20 интегрирующие RC-цепи, каждая из которых состоит из последовательно соединенных регулируемого резистора и конденсатора, второй обкладкой соединенного с общей шиной, и

RS-триггер 21.

Входная шина 2 соединена с первыми входами элемента совпадения 12 и элемента И-НЕ 10, второй вход которого соединен с шиной синхронизации 1, входом инвертора 4 и первыми входами эле."ентов И-НЕ 7 и 8, входы которых соединены с первой 13 и второй 14 выходными шинами соответственно, выход инвертора 4 подключен к счетному входу D-триггера 5, прямой и инверсный выходы которого соответственно соединены с установочным и информационным входами D-триггера 6, счетный вход которого соединен с выходом элемента И-НЕ 8, второй вход которого соединен с вторым входом элемента И-НЕ 7, прямым выходом 0-триггера 5 и третьей, выходной шиной 15, третий вход соединен с прямым выходом D-триггера 6, установочный и информационный входы которого соединены через первые входы элементов И-НЕ 17, 18 (J и К входы JK-триггера 9), регулируемые сопротивления первой 19 и второй 20 интегрирующих RC-цепей с установочным и обнуляющим входами RS-триггера 21 соответственно, прямой и инверсный выходы которого соответственно соединены. с

15

40

45 тактовым, триггер 5 в нулевом состояние.

Низкий уровень прямого выхода перекрывает элементы И-HF 7, 8 и устанавливает триггер 6 по установочному входу в единичное состояние, на выходных шинах 13, 14

55

35 вторыми входами элементов И-НЕ 18, 19.

Первый вход элемента И-HE 11 соединен с шиной управления 3, второй вход соединен с прямым выходом RS-триггера 21, который является прямым выходом JK-триггера, а выход с вторым входом элемента совпадения 12, выход которого соединен с информационным входом D-триггера 5, четвертая выходная шина 16 соединена с выходом элемента И-НЕ 10, третий вход которого соединен с инверсным выходом D-триггера 5

Устройство работает в двух режимах.

1-й р е ж и м . Формирование пачки импульсов в интервале длительности асинхронного сигнала и формирование синхронизируемого импульса, соответствующего началу пачки.

На шину управления 3 подается низкий уровень, который перекрывает элемент ИНЕ 11, тем самым исключает влияние задержек, формируемых на JK-триггере 9 с задержкой срабатывания, т,е. на элементах

17, 18, интегрирующих цепях 19, 20 и RSтриггере 21. При этом устройство работает аналогично устройству, взятому за прототип.

2-й р е ж и м. Формирование регулируемых пачек импульсов в интервале длительности асинхронного сигнала, формирование синхронизируемых импульсов, соответствующих началу каждой пачки импульсов. Формирование импульса по переднему фронту асинхронного сигнала.

На шину управления 3 подается высокий уровень, разрешающий прохождение через элемент И-НЕ 11 задержанных импульсов, формируемых на JK-триггере 9 с задержкой срабатывания, т,е. элементах 17, 18, RC-цепях 19, 20 и RS-триггере 21, которые поступают на схему совпадения 12.

В исходном состоянии на входной шине

2 низкий уровень, по шине синхронизации

1 поступают тактовые импульсы (фиг. 2, а), на выходе инвертора 4 импульсы инверсные (фиг, 2, е, ж) — высокие уровни, триггер 21— в единичное состояние, на третьей выходной шине 15 — низкий уровень, а на четвертой 16 — единичный (фиг. 2, и), Триггер 5 находится в ждущем режиме, Входной асинхронный импульс (фиг. 2, б) устанавливает на D-входе триггера 5 высокий уровень при переходе уровня с низкого на высокий на выходе инвертора 4, следовательно, на Свходе триггера 5 устанавливается единичное состояние (фиг. 2, г). Высокий уровень

1723658 прямого выхода триггера 5 разрешает прохождение импульсов тактовой частоты с шины 1 через элемент И-НЕ 7 на выходную шину 13 (фиг. 2, е), через элемент И-НЕ 8 на выходную шину 14 проходит один импульс (фиг. 2, ж). По окончании выходного импульса на выходной шине 14 создается перепад с низкого уровня на высокий, по которому триггер 6 (на его D-входе низкий уровень инверсного выхода триггера 5) устанавливается в нулевое состояние (фиг. 2, з) и низкий уровень прямого выхода перекрывает элемент И-НЕ 8, Также высокий уровень прямого выхода триггера 5 устанавливает низкий уровень (фиг. 2, и) на выходе элемента И-НЕ

17, так как на втором его входе присутствует высокий уровень (фиг. 2, о), поступающий с инверсного выхода триггера 21. При установке низкого уровня на выходе элемента И-НЕ 17 конденсатор интегрирующей цепи 19 разряжается (фиг. 2, л) до уровня срабатывания по входу RS-триггера 21, при этом íà его прямом выходе (фиг, 2, н) устанавливается высокий уровень, который на выходе элемента И-НЕ 17 устанавливает высокий, а на D-входе триггера 5 (фиг. 2, д) через элемент И-НЕ 11 и элемент совпадения 12 устанавливает низкий уровень, и триггер 5 возвращается в нулевое состояние при наличии на С-входе переяада с низкого на высокий, поступающего с выхода инвертора 4. Низкий уровень единичного выхода триггера 5 устанавливает по S-входу триггер 6 в единичное состояние и элементы И-НЕ 7 и 8 в исходное состояние, а высокий уровень с инверсного выхода устанавливает низкий уровень на выходе элемента И-НЕ 18 (фиг. 2, к) и разрешает прохождение импульсов тактовой частоты с шины 1 через элемент И-НЕ 10 (фиг, 2, и) на выходную шину 16. При установке низкого уровня на выходе элемента И-НЕ 16 конденсатор интегрирующей цепи 20 разряжается (фиг. 2, м) до уровня срабатывания по входу R триггера 21, при этом на его прямом выходе устанавливается низкий уровень, переводящий выход четвертого элемента И-НЕ 18 в высокий уровень, а на

D-выходе(фиг, 2, д) триггера 5через элемент

И-НЕ 11 и элемент совпадения 12 устанавливает высокий уровень, и процесс повторяется до установления на входной шине 2 низкого уровня, По окончании входного асинхронного сигнала устройство возвращается в исходное состояние. Изменением сопротивления регулируемого резистора интегрирующей цепи 19 изменяется задержка т срабатывания триггера 21 по входу S, которой соответствует длительность высокого уровня на прямом выходе триггера 5, а следовательно и длительность пачки импульсов на выходной шине 13. Изменением соп ротивления регулируемого резистора интегрирующей цепи 20 изменяется задер5 жка zz срабатывания триггера 21 по входу

R, которой соответствует длительность низкого уровня на прямом выходе триггера 5, а соответственно, и интервал между пачками импульсов на выходной шине 13 или дли10 тельность пачки импульсов (фиг. 2, и) на выходной шине 16, начальный импульс которой отстоит от фронта асинхронного сигнала, поступающего с входной шины 2, на длительность, интервала высокого уровня

15 на прямом выходе триггера 5 (фиг, 2, г). При формировании на выходной шине 13 одной пачки импульсов на выходной шине 15 формируется импульс по переднему фронту асинхронного сигнала, на выходной шине

20 16 формируется пачка импульсов, отстоящая от переднего фронта асинхронного сигнала а интервал, соответствующий длительности пачки импульсов на шине 13.

Макет заявляемого устройства был со25 бран и испытан в лабораторных условиях. В устройстве были использованы микросхемы

155-й серии. Переменные резисторы интегрирующих цепей 470 Ом. В первой интегрир ующей цепи 19 был использован

30 конденсатор 0,47 мкФ и второй конденсатор 20 1 мкФ. При этом время задержки т, вносимое интегрирующей цеп ью 19, регулируется от 10 до 300 мкс, а время задержки т, вносимое интегрирующей цепью 20, — от

35 10 до 450 мкс.

1-й р е ж и м. На. шину управления 3 подается низкий уровень, тогда устройство работает аналогично устройству, взятому за прототип.

40 2-й р е ж и м . На шину управления 3 подается высокий уровень. На шину синхронизации 1 подавались импульсы с частотой повторения 1 мГц, а на входную шину 2— асинхронные сигналы длительностью 0,5 мс

45 и частотой повторения 1 кГц, На выходных шинах формировались следующие сигналы, При установке т = 20 мкс, n = 30 мкс на выходной шине 19 в интервале асинхронного сигнала 0,5 мс формировалось десять па50 чек импульсов по 20 импульсов в пачке с интервалом между пачками 30 мкс. На выходной шине 14 в интервале асинхронного сигнала формировалась пачка из 10 импульсов, соответствующих началу каждой пачки на выходной шине 13. Длительность импульса соответствовала длительности синхроимпульса, а период повторения был равен 50 мкс. На выходной шине 15 в интервале асинхронного сигнала формировалась

1723658

10 пачка из 10 импульсов. Длительность импульса 20 мкс и период повторения 50 мкс.

На выходной шине 16 в интервале асинхронного сигнала формировалось 10 пачек импульсов по 30 импульсов в пачке и периодом повторения 50 мкс. При этом первая пачка отстояла от переднего фронта асинхронного сигнала на 20 мкс или 20 синхроимпул ьсов.

Приустановке х =200мкс, юг=300.мкс на выходной шине 13 в интервале асинхронного сигнала 0,5 мс формировалась одна пачка импульсов из 200 импульсов, на выходной шине 14 формировался один импульс от переднего фронта асинхронного сигнала началу пачки на выходной шине.13.

На шине 15 формировался один импульс от переднего фронта асинхронного сигнала длительностью 200 мкс. На выходной шине

16 формировалась пачка импульсов из 300 импульсов, отстоящая от переднего фронта асинхронного сигнала на 200 мкс или 200 тактовых синхроимпульсов.

Формула изобретения

1. Устройство тактовой синхронизации и выделения пачки импульсов по авт.св. М

884106, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей путем дополнительного формирования регулируемых пачек импульсов в заданном интервале асинхронного сигнала с одновременным формированием импульса регулируемой длительности, в него введены

JK-триггер с задержкой срабатывания, третий и четвертый элементы И-НЕ, элемент И, шина выбора режима, третья и четвертая выходные шины, причем 0-вход первого триггера соединен со входной шиной и с

5 первым входом третьего элемента И-HE через элемент И, второй вход которого соединен с выходом четвертого элемента И-НЕ, первый вход которого соединен с шиной выбора режима, второй вход — с прямым

10 выходом JK-триггера с задержкой срабатывания, J-вход которого соединен с прямым выходом первого триггера и с третьей выходной шиной, К-вход — с инверсным выходом первого триггера и со вторым входом

15 третьего элемента И-НЕ, выход которого соединен с четвертой выходной шиной, третий вход — с шиной тактовых импульсов.

2, Устройство пои. 1, отл и чаю щеес я тем, что J К-триггер с задержкой срабаты20 вания содержит RS-триггер, первую и вторую регулируемые интегрирующие

RC-цепи, каждая из которых состоит из последовательно соединенных регулируемого резистора и конденсатора, второй обклад25 кой соединенного с общей шиной, первый и второй элементы И-НЕ, первые входы которых являются входами J и К соответственно, а выходы через первую и вторую интегрирующие RC-цепи соответственно соедине30 ны с установочным и обнуляющим входами

RS-триггера, прямой и инверсный выходы которого соединены со вторыми входами второго и первого элементов И-НЕ соответственно, прямой выход RS-триггера являет35 ся прямым выходом JK-триггера с задержкой срабатывания.

1723658

@цг. 2

45

Редактор Т.Орловская

Заказ 1069 Тираж, Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 г д

L1

8

Ж

Л

Составитель Н.Поршнева

Техред М.Моргентал Корректор Л.Бокшан