Логический элемент на переключении тока

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике, в частности к логическим элементам на переключении тока, и может быть использовано в сверхскоростных интегральных схемах для построения комбинационной части логических схем. Цель изобретения - расширение функциональных возможностей логического элемента на переключении тока путем реализации функции трех переменных. Логический элемент на переключении тока содержит пять транзисторов , резистор, два источника тока, две шины опорного напряжения, три входа, выход , девять дополнительных транзисторов и два дополнительных источника тока. Введение девяти дополнительных транзисторов, двух дополнительных источников тока и третьего входа позволяет расширить функциональные возможности логического элемента за счет реализации функции трех переменных Y ХчХаХз + X-i&Xs при обеспечении максимального быстродействия и сохранении стабильности уровня логического нуля на выходе без использования диодного фиксатора потенциала. 1. ил. СО С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (sa>s Н 03 К 19/086

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4785648/21 (22) 24.01.90 (46) 30.03.92. Бюл. ¹ 12 (71) Ленинградское объединение электронного приборостроения "Светлана" (72) А.П. Голубев и С.Л.Афиногенов (53) 621.374(088.8) (56) Алексеенко А.Г., Шагурин И.И. Микросхемотехника M.: Радио и связь, 1982, с.

115 †1.

Микросхемы и интегральные. Кристалл

К1520ХМ2. Исходные данные по проектированию заказных матричных БИС на базовом матричном кристалле И60. 734. 106, 1984, с.

43-44, 54.

Руководящий документ. Микросхемы интегральные матричные на основе базового матричного кристалла (. -200. Правила проектирования РД бМ 194-88, 1988, с. 100. (54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА ПЕРЕКЛЮЧЕНИИ ТОКА (57) Изобретение относится к импульсной технике, в частности к логическим элеменИзобретение относится к импульсной технике, в частности к логическим элементам на переключении тока, и может быть использовано в сверхскоростных интегральных схемах для построения комбинационной части логических схем.

В ряде случаев при построении ЭСЛ элемента, выполненного на двух уровнях переключения тока, требуется реализовать функцию F(X1, Хг, Хз) = Х1Х2Хз + Х1Х2Хз причем задержка переключения от любой,, Ы,, 1723668 А1 там на переключении тока, и может быть использовано в сверхскоростных интегральных схемах для построения комбинационной части логических схем. Цель изобретения — расширение функциональных возможностей логического элемента на переключении тока путем реализации функции трех переменных. Логический элемент на переключении тока содержит пять транзисторов, резистор, два источника тока, две шины опорного напряжения, три входа, выход, девять дополнительных транзисторов и два дополнительных источника тока. Введение девяти дополнительных транзисторов, двух дополнительных источников тока и третьего входа позволяет расширить функциональные возможности логического элемента за счет реализации функции трех переменных Y = Х1Х2Хз+ Х1Х2Хз при обеспечении максимального быстродействия и сохранении стабильности уровня логического нуля на выходе без использования диодного фиксатора потенциала, 1 ил. переменной при этом должна быть минимальна.

Известен метод построения функций трех переменных на одном переключаемом токе при трех ярусах его переключения(1), однако задержка сигнала, подаваемого на нижний ярус, оказывается значительно больше задержки прохождения сигнала, подаваемого на верхний ярус.

Кроме того, значительное число БМК

ЭСЛ-типа ориентировано на два уровня пе1723668 реключения тока, что также заставляет ограничиваться двумя уровнями.

Известны элементы (2), выполненные на двух и более токовых ключах с двумя уровнями переключения тока, причем максимальная задержка таких элементов примерно равна задержке одного токового ключа.

Однако в элементе, построенном данным образом, через резистор, формирующий логический перепад, может одновременно протекать О, 1, 2 и более токов токовых ключей. Для стабилизации уровня логического нуля в элемент введен параллельно резистору ограничительный диод, что, однако, не позволяет сохранять достаточно стабильный уровень логического нуля в схеме и приводит к увеличению задержки.

Наиболее близким по технической сущности к предложенному является элемент(3), реализующий функцию F(X1, Хг) =

Х1Х2 на двух уровнях переключения тока, т.е. функцию, являющуюся частным случаем требуемой при Хз = О, Недостатком этого элемента является невозможность реализации функции Е(Х1, Х, Хз) = Х1Х2Хз + Х1Х2Хз от трех переменных, каждая из которых отлична от const, Целью изобретения является расширение функциональных возможностей логического элемента на переключении тока путем реализации функции трех переменных.

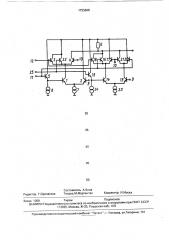

Поставленная цель достигается тем, что в логический элемент на переключении тока, содержащий пять транзисторов, резистор, два источника тока, две шины опорного напряжения, два входа и выход, причем первый и второй транзисторы выполнены с объединенными эмиттерами, которые подключены к первому источнику тока, коллектор первого транзистора соединен с эмиттерами третьего и четвертого транзисторов, база первого транзистора соединена с эмиттером пятого транзистора и со вторым источником тока, база второго— с первой шиной опорного напряжения, база четвертого транзистора подключена ко второй шине опорного напряжения, база пятого транзистора соединена с первым входом, база. третьего транзистора соединена со вторым входом, коллектор четвертого транзистора подключен к первому выводу резистора, коллектор третьего транзистора подключен к коллектору пятого транзистора и второму выводу резистора, согласно изобретению, введены девять дополнительных транзисторов, два дополнительных источника тока, третий вход, причем эмиттеры первого и второго дополнительных транзисторов соединены с первым дополн,.гельн ым источником тока, коллектор первого дополнительного транзистора соединен с эмиттерами третьего, четвертого и пятого

5 дополнительных транзисторов, база первого дополнительного транзистора соединена с эмиттером шестого дополнительного транзистора и вторым дополнительным источником тока, база второго дополнитель10 ного транзистора — с первой шиной опорного напряжения, база третьего дополнительного транзистора — с базой седьмого дополнительного транзистора и с первым входом логического элемента, а коллектор—

15 с коллекторами пятого, восьмого дополнительных транзисторов и коллектором четвертого транзистора, база четвертого и восьмого дополнительных транзисторов соединены со второй шиной опорного напря20 жения, а коллектор четвертого дополнительного транзистора — с коллекторами,шестого, седьмого и девятого дополнительных транзисторов, с коллекторами второго и третьего транзисторов, эмиттеры

25 восьмого и седьмого дополнительных транзисторов соединены с коллектором второго дополнительного транзистора, а эмиттер девятого дополнительного транзистора — с коллектором первого транзистора, база пя30 того дополнительного транзистора соединена со вторым входом элемента, а базы шестого и девятого дополнительных транзисторов — с третьим входом элемента.

Предложенный логический элемент на

35 переключении тока обладает новизной и существенными отличиями. Введение дополнительных элементов, указанных в формуле изобретения, позволяет реализовать функцию Р(Х1, Х2, Хз) = Х1Х2Хз + X>XzXa, причем

40 через резистор протекает одновременно не более одного тока первого источника тока или первого дополнительного источника, и поэтому не требуется подключения ограничительного диода, а задержка практически

45 равна задержке элемента, реализующего функцию F(X1, Xz) = Х Х2.

Ни одного известного элемента, позволяющего реализовать аналогичную функцию аналогичным образом, нами не

50 обнаружено.

На чертеже представлена электрическая схема логического элемента на переключении тока, реализующего функцию

55 F(X1, Xz, Хз) = Х Х2Хз + Х Х2Хз.

Логический элемент на переключении тока содержит пять транзисторов 1 — 5, резистор

6, два источника тока 7, 8, два шины 9. 10 опорного напряжения, два входа 11, 12 и

1723668

30

40

50

Составитель А,Янов

Техред M.Ìîðãåíòàë

Корректор И.Муска

Редактор T.Îðëîâñêàÿ

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101

Заказ 1069 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5