Устройство для измерения симметричных составляющих напряжений трехфазной сети

Иллюстрации

Показать всеРеферат

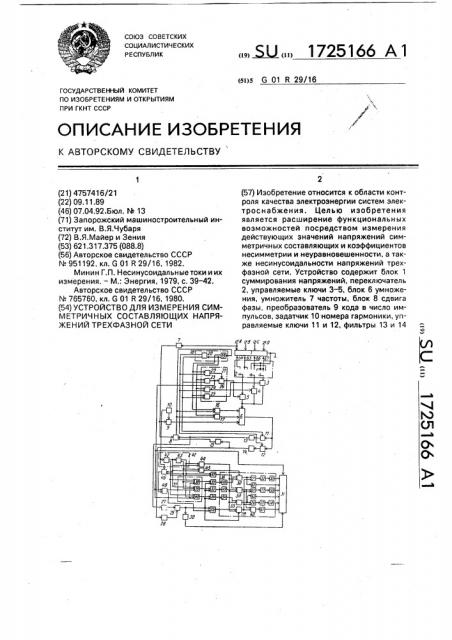

Изобретение относится к области контроля качества электроэнергии систем электроснабжения . Целью изобретения является расширение функциональных возможностей посредством измерения действующих значений напряжений симметричных составляющих и коэффициентов несимметрии и неуравновешенности, а также несинусоидальности напряжений трехфазной сети. Устройство содержит блок 1 суммирования напряжений, переключатель 2, управляемые ключи 3-5, блок 6 умножения , умножитель 7 частоты, блок 8 сдвига фазы, преобразователь 9 кода в число импульсов , задатчик 10 номера гармоники, управляемые ключи 11 и 12, фильтры 13 и 14

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4757416/21 (22) 09,11.89 (46) 07.04.92,Бюл. М 13 (71) Запорожский машиностроительный институт им. В.Я.Чубаря (72) В.Я.Майер и Зения (53) 621,317.375 (088.8) (56) Авторское свидетельство СССР

N 951192, кл. G 01 R 29/16, 1982.

Минин Г.П. Несинусоидальные токи и их измерения. — M.: Энергия, 1979, с. 39-42.

Авторское свидетельство СССР

N 765760, кл. G 01 R 29/16, 1980. (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СИММЕТРИЧНЫХ СОСТАВЛЯЮЩИХ НАПРЯЖЕНИЙ ТРЕХФАЗНОЙ СЕТИ ЯЛ 1725166 А1 (57) Изобретение относится к области контроля качества электроэнергии систем электроснабжения. Целью изобретения является расширение функциональных возможностей посредством измерения действующих значений напряжений симметричных составляющих и коэффициентов несимметрии и неуравновешенности, а также несинусоидальности напряжений трехфазной сети. Устройство содержит блок t суммирования напряжений, переключатель

2, управляемые ключи 3-5, блок 6 умножения, умножитель 7 частоты, блок 8 сдвига фазы, преобразователь 9 кода в число импульсов, задатчик 10 номера гармоники, управляемые ключи 11 и 12, фильтры 13 и 14

1725166

35 низких частот, делитель 15 напряжения, элементы И 16 и 17, счетчик 18, состоящий из двух последовательно соединенных триггеров 19 и 20, дешифратор 21, выполненный в виде блока из элементов И 22 — 25 и элемента ИЛИ 26, и блок 31 индикации. В устройство введены квадраторы 27 и 28, сумматор

29, блок 30 извлечения квадратного корня, управляемые ключи 32.— 35, вычислительный блок 36, дешифратор 37, состоящий из элементов И 38 — 40, счетчик 41, выполненный в виде блока из двух последовательно соединенных триггеров 42 и 43, элементы И 44 — 47 и триггер 48, Предпочтительным является

Изобретение относится к области контроля качества электроэнергии систем электроснабжения.

Известно устройство для измерения симметричных составляющих напряжений трехфазной сети, содержащее масштабный преобразователь, коммутатор фаз, преобразователь аналог-код, блок памяти, счетчики, постоянные запоминающие устройства, умножители, блоки реализации функции косинуса и синуса, блоки сумматоров-накопителей, квадратор, блок управления, блок регистрации, блок деления, блок реализации функции арктангенса, определитель знака и сумматор.

К недостаткам этого устройства следует отнести недостаточные возможности из-за использования фазных соотношений векторов гармоник для измерения симметричных составляющих напряжений. Эти фазные соотношения векторов гармоник соответствуют только лишь рассмотренным ЭДС еА, еБ, ес, представляющим собой три фазные ЭДС трехфазного неявнополюсного синхронного генератора, которые изображены прямоугольными

Т 27 волнами, смещенными на углы

Каждая ЭДС (eA, ев, ec) повторяет по форме остальные со двигом на одну треть периода (— ) и может быть разложена на

Т

3 грамоники. Однако часто встречающиеся в практической энергетике периодические кривые имеют произвольную форму. Кроме того, известное устройство не позволяет измерять действующие значения выполнение вычислительного блока из блоков 62 и 63 извлечения квадратного корня и четырех цепочек, первая и вторая из которых состоят из последовательно соединенных накапливающего сумматора 49, блока

50 запоминания, блока 51 деления, блока 52 извлечения квадратного корня и масштабирующего блока 53, третья — из накапливающего сумматора 54, ключа 55, блока 56 деления, блока 57 извлечения квадратного корня и масштабирующего блока 58, а четвертая — из блока 59 запоминания, сумматор

60 и блока 61 извлечения квадратного корня. 1 з.п.ф-лы, 1 ил. напряжений симметричных составля ющих и тем самым коэффициенты несимметрии и неуравновешенности, а также несинусоидальности трехфазных напряжений, Наиболее близким техническим решением к изобретению является устройство для измерения симметричных составляющих напряжений трехфазной сети, содержащее блок суммирования напряжений, переключатель, ключи, блок умножения, умножитель частоты, блок сдвига, преобразователь кода, задатчик номера гармоники, фильтры низких частот, блок индикации, делитель напряжения, счетчик, дешифратор и элементы И.

Однако данное устройство позволяет измерять только гармонические составляющие, а не действующие значения напряжений симметричных составляющих, что не дает возможности оценить как степень несимметрии и неуравновешенности, так и уровни несинусоидальности напряжений трехфазной сети.

Цель изобретения — расширение функциональных возможностей посредством измерения действующих значений напряжений симметричных составляющих и коэффициентов несимметрии и неуравновешенности, а также несинусоидальности напряжений трехфазной сети.

Поставленная цель достигается тем, что в устройство для измерения симметричных составляющих напряжений трехфазной сети, содержащее блок суммирования напряжений, переключатель, блок умножения, блок индикации, 17251 бб

30

55 блок сдвига фазы, умножитель частоты, преобразователь кода в число импульсов, задатчик номера гармоники, дешифратор на восемь входов, выполненный в виде четырех элементов И, первый и второй из которых подключены к элементы ИЛИ, делитель напряжения, два фильтра низких частот, счетчик, состоящий из двух последовательно соединенных триггеров, два элемента И и пять управляемых ключей, причем входные шины через блок суммирования напряжений и переключатель подключены к входам первого, второго и третьего ключей, управляющие входы которых подключены к выходам дешифратора, а выходы ключей объединены и подключены к входу блока умножения, к двум установочным входам которого подключены выходы двух элементов И, к уп равля ющему входу — выход и реобразователя кода в число импульсов; управляющим входом соединенного с задатчиком номера гармоники, одна из входных шин через умножитель частоты подключена к входу преобразователя кода в число импульсов и к первому входу блока сдвига фазы, второй вход которого через первый фильтр низкой частоты и четвертый управляемый ключ, а третий вход через делитель напряжения, второй фильтр низкой частоты и пятый управляемый ключ подключены к выходу блока умножения, выход блока сдвига фазы подключен к первым входам двух элементов И и к входу первого триггера счетчика, выходы первого триггера счетчика подключены к первым входам элементов И дешифратора и к вторым входам двух элементов И, выходы второго триггера — к вторым входам элементов И дешифратора и к управляющим входам четвертого и пятого ключей, в него дополнительно введены первый и второй квадраторы, сумматор, блок извлечения квадратного корня, второй счетчик, состоящий из двух последовательно соединенных триггеров, с третьего по шестой элементы И, триггер, дешифратор, выполненный в виде трех элементов И, с шестого по девятый управляемые ключи и вычислительный блок, причем входы квадраторов соединены с выходами фильтров низких частот, а выходы подключены к входам сумматора, выходом подключенного через блок извлечения квадратного корня к блоку индикации и через шестой, седьмой, восьмой и девятый ключи к входам вычислительного блока, выходы которого подключены к блоку индикации, управляющим входом объединенному с первым входом триггера, третьими входами первого и третьего элементов И второго дешифратора и подключенному к выходу второго элемента И первого дешифратора, выход четвертого элемента И которого подключен к управляющему входу первого ключа, а выход элемента ИЛ И= к управляющему входу третьего ключа, первый выход первого триггера второго счетчика подключен к первым входам второго элемента И второго дешифратора, третьего, четвертого и пятого элементов И, а второй выход — к первым входам первого и третьего элементов И второго дешифратора и шестого элемента И, первый выход второго триггера второго счетчика подключен к вторым входам третьего элемента И второго дешифратора, третьего и шестого элементов И, а второй выход — к вторым входам первого и второго элементов И второго дешифратора, четвертого и пятого элементов И, третий вход которого объединен с входом первого триггера второго счетчика и подключен к второму выходу задатчика номера гармоники, а выход пятого элемента И соединен с вторым входом триггера, первым выходом подключенного к третьему входу второго.элемента И второго дешифратора, а вторым выходом — к управляющим входам девятого ключа и вычислительного блока, выходы первого, второго и третьего элементов И второго дешифратора подключены соответственно к управляющим входам шестого, седьмого и восьмого ключей, выходы третьего, четвертого и шестого элементов И подключены к другим управляющим входам вычислительного блока.

При этом вычислительный блок содержит два блока извлечения квадратного корня и четыре цепочки, первая и вторая из которых состоят из последовательно соединенных накапливающего сумматора, блока запоминания, блока деления, блока извлечения квадратного корня и масштабирующего блока, третья — из накапливающего сумматора, ключа, блока деления, блока извлечения квадратного корня и масштабирующего блока, а четвертая — из блока запоминания, сумматора и блока извлечения квадратного корня, причем входы накапливающих сумматоров трех цепочек и блока запоминания четвертой цепочки подключены к входам вычислительного блока, к одному из управляющих входов которого объединены и подключены вторые входы блоков запоминания трех цепочек и ключа третьей цепочки, а к другим — третьи входы блоков запоминания, вторые входы блоков деления трех цепочек объединены и подключены к вы1725166 ходу блока запоминания четвертой цепочки, второй вход сумматора которой соединен с первым входом блока деления второй цепочки, а входы первого и второго блоков извлечения квадратного корня соединены с первыми входами блоков деления первой и третьей цепочек соответственно, при этом выходы блока извлечения квадратного корня четвертой цепочки, масштабирующих блоков трех цепочек и двух блоков извлечения квадратного корня являются выходами вычислительного блока.

На чертеже представлена блок-схема устройства для измерения симметричных составляющих напряжений трехфазной сети.

Входные шины А, В, С, через блок 1 суммирования напряжений, переключатель 2, ключи 3 — 5 соединены с блоком 6 умножения. Одна иэ входных шин через умножитель 7 частоты подключена к первому входу блока 8 сдвига фазы импульсов. Выход умножителя частоты через преобразователь 9 кода в число импульсов, к управляющим входам которого присоединен задатчик 10 номера гармоники, подключен к управляющему входу блока умножения. Выход блока умножения через ключи 11 и 12 соединен с фильтрами 13 и

14 низких частот. Выход фильтра 13 присоединен к второму входу блока сдвига фазы, а выход фильтра 14 через делитель 15 напряжения к третьему входу блока сдвига фазы, выход которого подключен к первым входам элементов И 16 и 17, и к счетчику

18, который состоит из триггеров 19 и 20.

Вторые входы элементов И 16 и 17 соединены с четными входами дешифратора 21, состоящего из элементов И 22 — 25 и элемента ИЛИ 26. Выходы триггера 19 счетчика подключены к первым входам элементов И 22 — 25, вторыми входами соединенных с выходами триггера 20 счетчика и подключенных к управляющим входам ключей 11 и 12. Выходы элементов И 22 и

23 через элемент ИЛИ 26 дешифратора подключены к управляющему входу ключа

5, а выходы элементов И 24 и 25 — к управляющим входам соответственно ключей 4 и 3. Выходы фильтров 13 и 14 соединены с входами квадраторов 27 и 28, выходы которых подключены к входам сумматора 29, выходом присоединенного через блок 30 извлечения квадратного корня к блоку 31 индикации, и через ключи 32 — 35 к вычислительному блоку 36, выходы которого подключены к блоку 31 индикации, Управляющие входы ключей 32 — 35черездешифратор 37, состоящий из элементов И

38-40, соединены с выходами счетчика 41, выполненного в виде двух последовательно соединенных триггеров 42 и 43. Прямой выход триггера 42 счетчика подключен к первым входам элемента И 39 дешифратора и элементов И 44-46, а инверсный выход—

5 к первым входам элементов 39 и 40 дешифратора и элемента И 47. Прямой выход триггера 43 счетчика подключен к вторым входам элемента И 40 дешифратора и элементов И 44 и 47, а инверсный выход — к

10 вторым входам элементов И 38 и 39 дешифратора и элементов И 45 и 46, третий вход которого объединен с входом триггера 42 счетчика и подключен к второму выходу задатчика 10 номера гармоники. Выход эле15 мента И 46 соединен с вторым входом триггера 48, первый вход которого объединен с третьими входами элементов И 38 и 40 дешифратора, управляющим входом блока индикации, и подключен к выходу элемента

2р И 23 дешифратора 21. Прямой выход триггера 48 подключен к третьему входу элемента

И 39 дешифратора 37, а инверсный выход— к управляющим входам ключа 35 и вычислительного блока. Выходы элементов И 44, 45 и 47 подключены к другим управляющим входам вычислительного блока.

Вычислительный блок содержит четыре цепочки, первая и вторая из которых состоят из последовательно соединенных накап30 ливающего сумматора 49, блока 50 запоминания, блока 51 деления, блока 52 извлечения квадратного корня и масштабирующего блока 53, третья — накапливающего сумматора 54, ключа 55, блока 56

35 деления, блока 57 извлечения квадратного корня и масштабирующего блока 58, а четвертая — блока 59 запоминания, сумматора

60 и блока 61 извлечения квадратного корня. При этом первые входы блоков 51 деле40 ния и 56 первой и третьей цепочки соотвественно соединены с входами блоков

62 и 63 извлечения квадратного корня, выходы которых подключены к блоку индикации. Входы накапливающих сумматоров 49

45 и 54 трех цепочек и блока 59 запоминания четвертой цепочки подключены к выходам кл ючей 32-35 соответст вен но, Уп ра вл я ющие входы блоков 50 и 59 запоминания трех цепочек и ключа 55 третьей цепочки объединены i, подключены к выходу элемента И 44.

Другие управляющие входы блоков 50 и 59 запоминания трех цепочек соответственно подключены к выходам элементов И 45 и 47 и к инверсному выходу триггера 48, Вторые входы блоков 51 и 56 деления трех цепочек объединены и подключены к выходу блока 59 запоминания четвертой цепочки, Выход блока 50 запоминания второй цепочки подключен к второму входу сумматора 60 четвертой цепочки. Выходы мас1725166

1

U >-- — (Од+ Ов+ Uc) .

20 ГЗ

Оз- (Uc Ua) V3

U4- (Ua Uc) 25

Ъ

1 (2) штабирующих блоков 53 и 58 трех цепочек и блока 61 извлечения квадратного корня четвертой цепочки подключены к блоку 31 индикации.

Один цикл работы устройства соответ- 5 ствует четырем периодам напряжения сети.

Блок 1 суммирования напряжений содержит измерительные трансформаторы, первичные обмотки которых подключены к 10 выходным шинам, а вторичные обмотки соединены таким образом, чтобы на выходах

64 — 67 блока 1 напряжения были соответственно равные

1 1 1

Ог= — (UA — Ов- — Ос

3 2 2 где UA. Ов, Uc — фазные напряжения трехфазной сети.

Левое по схеме положение переключа- 30 теля 2 соответствует режиму измерения напряжения нулевой последовательности Up, при этом напряжение U< подается на вход ключа 5, а входы ключей 4 и 3 подключаются к общей шине, 35

Среднее по схеме положение переключателя 2 соответствует режиму измерения напряжения прямой последовательности U+, при этом на вход ключа

5 подается напряжение Ог, на вход ключа 40

4 — напряжение Оз, на вход ключа 3— напряжение U4.

Правое по схеме положение переключателя 2 соответствует режиму измерения . напряжения обратной последовательно- 45 сти U-, при этом на вход ключа 5 подается напряжение Ог, на вход ключа 4 — напряжение U4, на вход ключа 3 — напряжение

Оз.

Номер гармоники исследуемой симмет- 50 ричной составляющей напряжения устанавливаются на задатчике 10, Выходы триггеров 19 и 20 подключены через дешифратор 21 к управляющим входам ключей 3 — 5, а выходы триггера 20 еще и к ключам 11 и 12, В дешифраторе

21 элемент И 22 открывается на первом периоде цикла работы устройства, элемент И 23 — на четвертом, элемент И 24— на втором, элемент И 25 — на третьем, Выходы элементов И 22 и 23 объединены через элемент ИЛИ 26, поэтому ключ 5 открыт на первом и четвертом периодах цикла работы устройства, ключ 4- на втором, ключ

3 — на третьем, ключ 11 — на третьем и четвертом, ключ 12 — на первом и втором, На первом периоде цикла работы устройства определяется синусная ортогональная составляющая у-й гармоники напряжения на входе ключа 5, на втором периоде — косинусная составляющая на входе ключа 4, на третьем периоде — синусная составляющая на входе ключа 3, на четвертом периоде — косинусная составляющая на входе ключа 5. Соответственно на фил ьтре 14 выделяется напряжение,. и ропорциональное сумме синусной составляющей на входе ключа 5 и консинусной составляющей на входе ключа 4, а на фильтре 13 — сумма синусной составляющей на входе ключа 3 и косинусной составляющей на входе ключа 5.

Комплексные значения симметричных составляющих напряжений у-й гармоники трехфазной сети равны

1 И И

+ (U ag+j0 ву)КОсу+)Ос )), I и 1 (6

U+It= U+J+ jU+ = — (U AP JUAN)+

+ (- — + j XUa + )Ов )+

2 2

1 .иа (- —,-) —, XUcg+ JUGS)l, 1 .v3

+ (- — -) — )(О в +) Ов )+

2 2

1, v3 (2 j 2 )(Ос(j 09)1

I I (. где 0<, О+у, U-y, Од,г, Ову, Ucg — синусные, Оо, 0+y, U - у, 0"ду . Ов, Ucg— косинусные ортогональные составляющие у -й гармоники соответственно напряжений нулевой, прямой, обратной последовательности и фазных напряжений трехфазной сети.

Разделяя выражение (2) на действител ьные и мнимые части после преобразований, получаем f725166 (7) U+= (8) гЗ

+ (0c<-0e<), (3) vs

+ (Ue Uc ), З (Ов О у) (9) K u —— 100

1 1 " 1

Г 3 (UA< 2 ц 2

V3

+ — (Ос -О в ) 30 (10) K LIO = 100

Кнс=100 (5) (6) 0о

U (= — (UAp Ue + UcdI), 1 1 1

0+II= — (UAg — — Ов — Uc )+

1 " 1 1

Г 3 (uA 2 2 О) 1 1 1

U-у — — (0Ag — 0 в — UcII)++

Сравнивая выражение в скобках в формулах (3) с формулами (1), видно, что

I II

0оу =01 Uo(=0!g (II Р II I

0+)= U2) + 03(, 0+(= 02У + 04У (4)

I 4 It ц

0-у = 02/ + 04 ), 0-У= 02У+ 03(, ), 1 П где 0у, 02, Uag, 04т — косинусные ортогональные составляющие у-й гармоники напряжений на выходе блока 1.

Действующее значение у-й гармоники напряжений симметричных составляющих определяется следующим образом:

Следовательно, действующие значения напряжений нулевой, прямой и обратной последовательности соответственно имеют вид где Й вЂ” количество учитываемых гармоник, UotI, U+g, U-g — действующие значения у-й гармоники;

Uo, U+, U- — действующие значения напряжений нулевой, прямой и обратной последовательности соответственно.

Определив действующие значения по выражениям (6), (7) и (8) напряжений симметричных составляющих, можно найти коэффициент нессимметрии, который определяется по формуле

20 коэффициент неуравновешенности, определяющийся по формуле коэффициент несинусоидальности трехфаз35 ного напряжения, который равен где U+> — действующее значение основной частоты напряжения прямой последовательности, 45 Таким образом на фильтрах 14 и 13 являются синусная UIt и косинусная UII ортогональные составляющие у -й гармоники напряжений нулевой, прямой и обратной последовательности, которые подаются на квадраторы 28 и 27 соответственно, где формируются квадраты О„и U, Эти квадраты суммируются на сумматоре 29 и на его выходе образуется значение (U <+ 0y)/2 (формула (5)). С выхода сумматора 29 полусумма

55 квадратов поступает на блок 30, где производится извлечение из нее квадратного корня в соответствии с формулой (5). Выходная величина Ug блока извлечения квадратного корня является действующим значением у13

1725166 и гармоники симметричных составляющих и она поступает на блок 31 индикации, Выходы триггеров 42 и 43 счетчика 41, прямой выход триггера 48 и выход элемента

И 23 дешифратора 21 подключены через дешифратор 37 к управляющим входам ключей 32 — 34, а инверсный выход триггера 48к ключу 35. В дешифраторе 37 элемент И 38 открывается в режиме измерения напряжения нулевой последовательности, элемент

И 39 — напряжения прямой последовательности, элемент И 40 — напряжения обратной последовательности.

Для определения действующего значения напряжения нулевой последовательности импульсы, выделяемые счетчиком 18 на каждом четвертом периоде цикла работы устройства, который соответствует окончанию вычисления каждой текущей гармоники, с выхода элемента И 23 подаются через элемент И 38 на управляющий вход ключа

32, При этом последний замыкается и с выхода сумматора 29 через него квадраты действующих значений гармоник напряжения нулевой последовательности поступают на накапливающий сумматор 49 первой цепочки, Таким образом, в накапливающем сумматоре после завершения цикла работы задатчик 10 номера гармоники, который соответствует N-м гармоникам, формируетг ся значение U<> . При этом с другого

r=1 выхода, зэдэтчик номера гармоники выдает сигнал об окончании анализа данной реализации напряжения на элемент И 46 и нэ счетный вход счетчика 41, Этот импульс изменяет состояние триггера 42 и на его выходе появляется единичный сигнал, который через элемент И 45 подается на разрешающий запись вход блока 50 запоминания первой цепочки, куда записывается сумма квадратов напряжений гармоник (формула (6)) с выхода накапливающего сумматора 49.

Для определения действующего значения напряжения прямой последовательности единичный сигнал с выхода триггера 42 проходит через элемент И 46 и подается на триггер 48, который, изменяя состояние, открывает ключ 35 и разрешает прием информации в блоке 59 запоминания. При этом выходная величина U+> сумматора 29, г представляющая собой составляющую основной гармоники напряжения прямой последовательности, через ключ 35 записывается в блок 59 запоминания. Ilo окончании вычисления данной гармоники импульс с выхода элемента И 23 изменяет состояние триггера 48 и ключ 35 закрыт. На другом выходе триггера 48 появляется единичный сигнал, который проходит через элемент И 39 и открывает ключ 33. Выходные

5 сигналы сумматора 29, начиная с второй до

N-й гармоники, через последний поступают на накапливающий сумматор 49 второй цепочки.

Таким образом, в накапливающем сум10 маторе по окончании анализа данной реализации напряжения образуется значение

U,2t,, которое записывается в блок 50

II =2 запоминания второй цепочки.

Для определения действующего значения напряжения обратной последовательности импульсы с выхода элемента И 23 проходят через элемент И 40 и замыкают ключ 34, через который с выхода сумматора

29 квадраты действующих значений гармоник напряжения обратной последовательности поступают на накапливающий сумматор 54, на выходе которого по окончаниц анализа данной реализации напряже25

N ния формируется значение, ; U . При г этом на выходе элемента И 44 появляется единичный сигнал, который подается одно30 временно на разрешающие считывание входы блоков 50 и 59 запоминания трех цепочек и на управляющий вход ключа 55.

Таким образом, выходная величина блока 50 запоминания первой цепочки поступа35 ет на блок 62 извлечения квадратного корня, на выходе которого образуется значение Uo (формула (6)), которое является действующим напряжения нулевой последовательности и оно поступает на блок 31 индикации.

40 Выходные сигналы блоков 59 и 50 запоминания второй цепочки суммируются на сумматоре 60 и нэ его выходе образуется

N значение U+1 + g U+ . Выходная ин =г формация сумматора поступает на блок 61 извлечения квадратного корня. На выходе последнего формируется значение U+ (формула (7)), представляющее собой действующее значение напряжения прямой последовательности, которое поступает на блок 31 индикации. Выходная величина накапливающего сумматора 54 через ключ 55 поступает на блок 63, где проходит извлечение из. нее квадратного корня. На выходе блока 63 извлечения квадратного корня образуется значение 0- (формула (8)), которое является действующим значением напряжения обратной последовательности, и оно поступает на блок 31 индикации.

1725166

5

25

35

45

Для определения коэффициента несимметрии выходные сигналы накапливающего сумматора 54 и блока 59 запоминания поступают на соответствующие входы блока

56 деления, на выходе которого получается подкоренное значение выражения (9). Выходная величина блока деления подается на блок 57 извлечения квадратного корня, затем поступает на масштабирующий блок 58.

Так как коэффициенгт передачи последнего равен 100, то на его выходе образуется величина Ко (формула (9)), представляющая собой коэффициент несимметрии, которая поступает на блок 31 индикации.

Для определения коэффициента неуравновешенности выходные сигналы блоков 59 и 50 запоминания первой цепочки поступают на соответствующие входы блока

51 деления, на выходе которого формируется подкоренное значение выражение (10).

Это значение с выхода блока деления подается на блок 52 извлечения квадратного корня, затем поступает на масштабирующий блок 53 с коэффициентом передачи 100. Выходная информация Кцр (формула (10)) масштабирующего блока является коэффициентом неуравновешенности и она поступает на блок 31 индикации.

Для определения коэффициента несинусоидальности выходные сигналы блоков

59 и 50 запоминания второй цепочки делятся в блоке 51 деления и на его выходе образуется подкоренное значение формулы (11), которое подается на блок 52 извлечения квадратного корня, затем поступает на масштабирующий блок 53, имеющий коэффициент передачи равный 100. Выходная величина Кнс (формула (11)) представляет собой коэффициент несинусоидальности трехфазного напряжения и поступает на блок 31 индикации.

Предлагаемое устройство, в отличие от известного, позволяет измерять не только все симметричные составляющие основной частоты и гармоник напряжений трехфазной сети, но и действующие значения напряжений прямой, обратной и нулевой последовательности, и коэффициенты несимметрии и неуравновешенности, а также несинусоидальности трехфазного напряжения, что способствует значительному расширению функциональных возможностей устройства.

Формула изобретения

1. Устройство для измерения симметричных составляющих напряжений трехфазной сети, содержащее блок суммирования напряжений, переключатель, блок умножения, блок индикации, блок сдвига фазы, умножитель частоты, преобразователь кода в число импульсов, задатчик гармоники, дешифратор, выполненный в виде четырех элементов И, первый и второй из которых подключены к элементу ИЛИ, делитель напряжения, два фильтра низких частот, счетчик, состоящий их двух последовательно соединенных триггеров, два элемента И и пять управляемых ключей, причем входные шины через блок суммирования напряжений и переключатель подключены к входам первого, второго и третьего ключей, управляющие входы которых подключены к выходам дешифратора, а выходы ключей объединены и подключены к входу блока умножения, к двум установочным входам которого подключены выходы двух элементов И, к управляющему входу— выход преобразователя кода в число импульсов, управляющим входом соединенного с задатчиком гармоники, одна из входных шин через умножитель частоты подключена к входу преобразователя кода в число импульсов и к первому входу блока сдвига фазы, второй вход которого через первый фильтр низкой частоты и четвертый управляемый ключ, а третий вход через делитель напряжения, второй фильтр низкой частоты и пятый управляемый ключ подключен к выходу блока умножения, выход блока сдвига фазы подключен к первым входам двух элементов И и к входу первого триггера счетчика, выходы которого подключены к первым входам элементов И дешифратора и к вторым входам двух элементов И, выходы второго триггера — к вторым входам элементов

И дешифратора и к управляющим входам четвертого и пятого ключей, о т л и ч а ю щ ее с я тем, что, с целью расширения функциональных возможностей путем измерения действующих значений напряжений симметричных составляющих и коэффициентов несимметрии и неуравновешенности, а также несинусоидальности трехфазной сети, в него дополнительно введены первый и второй квадраторы, сумматор, блок извлечения квадратного корня, второй счетчик, состоящий из двух последовательно соединенных триггеров, третий, четвертый, пятый и шестой элементы И, триггер дешифратор, выполненный в виде трех элементов И, шестой, седьмой, восьмой и девятый управляемые ключи и вычислительный блок, причем входы квадраторов соединены с выходами фильтров низких частот, а выходы подключены к входам сумматора, выходом подключенного через блок извлечения квадратного корня к блоку индикации и через шестой, седьмой, восьмой и девятый ключи — к входам вычислительного блока, 18

1725166

Составитель В.Майер

Техред М;Моргентал Корректор Э.Лончакова

Редактор Е.Папп

Заказ 1174 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 выходы которого подключены к блоку индикации, управляющим входом объединенному с первым входом триггера, третьими входами первого и третьего элементов И второго дешифратора и подключенному к выходу второго элемента И первого дешифратора, выход четвертого элемента И которого подключен к управляющему входу первого ключа, а выход элемента ИЛИ вЂ” к управляющему входу третьего ключа, первый выход первого триггера второго счетчика подключен к первым входам второго элемента И второго дешифратора, третьего, четвертого и пятого элементов И, а второй выход — к первым входам первого и третьего элементов И второго дешифратора и шестого элемента И, первый выход второго триггера второго счетчика подключен к вторым входам третьего элемента И второго дешифратора, третьего и шестого элементов И, а второй выход — к вторым входам первого и второго элементов И второго дешифратора, четвертого и пятого элементов И, третий вход которого объединен с входом первого триггера второго счетчика и подключен к второму выходу задатчика номера гармоники, а выход пятого элемента И соединен с вторым входом триггера, первым выходом подключенного к третьему входу второго элемента И второго дешифратора, а вторым выходом — к управляющим входам девятого ключа и вычислительного блока, выходы первого, второго и третьего элементов И второго дешифратора подключены соответственно к управляющим входам шестого, седьмого и восьмого ключей, выходы третьего, четвертого и шестого элементов И под10

35 ключены к другим управляющим входам вычислительного блока.

2. Устройство по и. 1, о т л и ч а ю щ е ес я тем, что вычислительный блок содержит два блока извлечения квадратного корня и четыре цепочки, первая и вторая из которых состоят из последовательно соединенных накапливающего сумматора, блока запоминания, блока деления, блока извлечения квадратного корня и масштабирующего блока, третья — из накапливающего сумматора, ключа, блока деления, блока извлечения квадратного корня и масштабирующего блока, а четвертая — из блока запоминания, сумматора и блока извлечения квадратного корня, причем входы накапливающих. сумматоров трех цепочек и блока запоминания четвертой цепочки подключены к входам вычислительного блока, к одному из управляющих входов которого подключены и с которым объединены вторые входы блоков запоминания трех цепочек и ключа третьей цепочки, а к другим — третьи входы блоков запоминания, вторые входы блоков деления трех цепочек объединены и подключены к выходу блока запоминания четвертой цепочки, второй вход сумматора которой соединен с первым входом блока деления второй цепочки, а входы первого и второго блоков извлечения квадратного корня соединены с первым входами блоков деления первой и третьей цепочек соответственно, при этом выходы блока извлечения квадратного корня четвертой цепочки, масштабирующих блоков трех цепочек и двух блоков извлечения квадратного корня являются выходами вычислительного блока.