Цифровой коррелятор

Иллюстрации

Показать всеРеферат

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (ы)з 6 06 F 15/336 0 !

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4847273/24 (22) 02.07.90 (46) 15.04.92. Бюл. № 14 (72) В. И. Зарицкий, Н. К. Бондарь, С. А.

Малышкин и И..И. Обод (53) 683(088. 8) (56) Авторское свидетельство СССР

¹ 1201846, кл. G 06 F 15/336, 1989, ! (54) ЦИФРОВОЙ КОРРЕЛЯТОР (57) Изобретение относится к измерительной и вычислительной технике и может быть

Изобретение относится к измерительной и вычислительной технике и может быть использовано для измерения функции взаимной корреляции между двумя случайными процессами, задержанными один относительно другого.

Целью изобретения является повышение быстродействия.

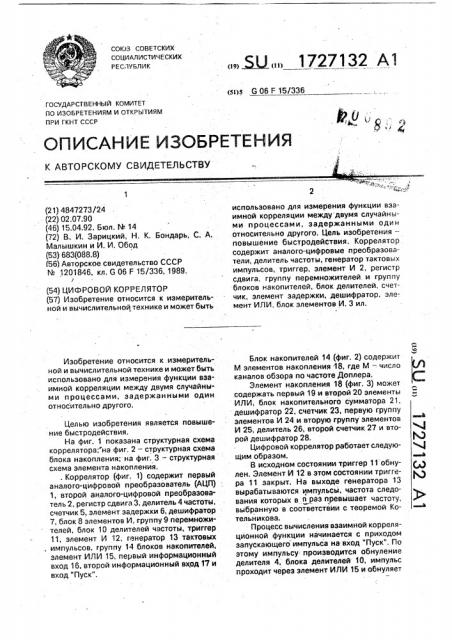

На фиг. 1 показана структурная схема коррелятора; на фиг, 2 — структурная схема блока накопления; на фиг. 3 — структурная схема элемента накопления. . Коррелятор (фиг. 1) содержит первый аналого-цифровой преобразователь (АЦП)

1, второй аналого-цифровой преобразователь 2, регистр сдвига 3, делитель 4 частоты, счетчик 5, элемент задержки 6, дешифратор

7, блок 8 элементов И, группу 9 перемножителей, блок 10 делителей частоты, триггер

11, элемент И 12, генератор 13 тактовых, импульсов, группу 14 блоков накопителей, элемент ИЛИ 15, первый информационный вход 16, второй информационный вход 17 и вход "Пуск".

„„ЯЦ„„1727132 Al использовано для измерения функции взаимной корреляции между двумя случайными процессами, задержанными один относительно другого, Цель иэобретения— повышение быстродействия. Коррелятор. содержит аналого-цифровые преобразователи, делитель частоты, генератор тактовых импульсов, триггер, элемент И 2, регистр сдвига, группу перемножителей и группу блоков накопителей, блок делителей, счетчик, элемент задержки, дешифратор, элемент ИЛИ, блок элементов И. 3 ил.

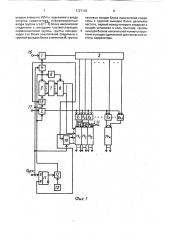

Блок накопителей 14 (фиг. 2) содержит

M элементов накопления 18, где М вЂ”. число каналов обзора по частоте Доплера.

Элемент накопления 18 (фиг. 3) может содержать первый 19 и второй 20 элементы

ИЛИ, блок накопительного сумматора 21, дешифратор 22, счетчик 23, первую группу элементов И 24 и вторую группу элементов

И 25, делитель 26, второй счетчик 27 и второй дешифратор 28, Э

Цифровой кор релятор работает следуюЩим образом. аЪ

В исходном состоянии триггер 11 обну- р лен. Элемент И 12 в этом состоянии триггера 11 закрыт. На выходе генератора 13 вырабатываются импульсы, частота следо- „ вания которых в и раз превышает частоту, выбранную в соответствии с теоремой Котельниковаова.

Процесс вычисления вэаимйой корреляционной функции начинается с приходом запускающего импульса на вход "Пуск". По этому импульсу производится обнуление делителя 4; блока делителей 10, импульс проходит через элемент ИЛИ 15 и обнуляет

1727132 счетчик 5, а также устанавливает триггер 11 в единичное состояние. Установление триггера 11 в единичное состояние разрешает работу элемента И 12. Импульсы с выхода генератора 13 проходят через элемент И 12 и поступают на синхровход АЦП 2, на входы счетчика 5, элемента задержки 6 и делителя

4. Импульсы, поступающий на синхровход

АЦП 2, осуществляют преобразование входных аналоговых сигналов в цифровой код с частотой в и раз превышающей частоту, выбранную по правилу Котельникова. Коэффициент деления делителя 4 выбирается

: равным h. Следовательно на выходе делителя 4 частота следования синхроимпульсов соответствует частоте, выбранной по правилу Котельникова. Импульсы с выхода делителя 4 поступают на синхровход АЦП 1, в котором осуществляется преобразование входных аналоговых сигналов, поступающих на первый вход 15 коррелятора, в цифровой код. Цифровые коды с выхода АЦП 1 сдвигаются по импульсам делителя 4 в регистре 3, т.е. осуществляется размножение сигналов по времени запаздывания. Импульсы с выхода делителя 4 проходят через элемент ИЛИ 15 и производят обнуление . счетчика 5. Таким образом, на выходе счетчика 5 код изменяется от 0 до h. Выходной код счетчика 5 поступает на дешифратор 7, с выхода которого снимается последовательность импульсов, В элементе задержки

6, величина задержки которого выбирается равной времени срабатывания перемножителя 9, тактовые импульсы задерживаются и в дальнейшем проходят через соответствующий элемент И блока 8, Таким образом, на выходе блока элементов И 8 появляются серия из и последовательных импульсов.

Выходные цифровые коды с АЦП 2 и с соответствующих выходов регистра 3 перемножаются в перемножителях 9 и результаты перемножения поступают на информационные входы соответствующих блоков накопителей 14. В блоках накопителей 14 осуществляется вычисление взаимной корреляционной функции с обзором по времени запаздывания т.е. номер блока накопления соответствует соответствующей временной задержке и на фиг. 1 показано, что обзор осуществляется как по времени запаздывания, так и с обзором по частоте Доплера, в каждом из каналов. С выходов блока делителей 10 снимаются импульсы для управления блоком накопления при обзоре по частоте Доплера. Коэффициент деления первого из делителей блока 10 выбирается равным N, где N — обьем выборки. При появлении импульса на выходе этого делителя триггер 11:устанавливается в нулевое состоэлемента пояснен на принципе обзора по

50 частоте Доплера и заключается в том, что в начале осуществляется накопление первого результата перемножения, а затем, при появлении импульса на втором синхровходе блока, осуществляется переключение эле55 мента (соответствующего) на накопление следующего результата перемножения.

Каждый второй синхровход определяет работу соответствующего элемента накопления, Для управления работой элемента накопления 18> импульс с второго синхров5

45 яние. Этим заканчивается процесс вычисления. взаимной корреляционной функции, ординаты которой с обзором как по времени запаздывания, так и с обзором по частоте

Доплера выдаются на выход коррелятора. В дальнейшем работа цифрового коррелятора аналогична.

Принцип обзора по частоте Доплера вытекает из следующих соображений. Наличие частоты Доплера приводит к "сжатию" или "растяжению" входных сигналов. При вычислении же взаимной корреляционной функции это приводит.к тому, что корреляционная точка движется и скорость этого движения определяется частотой Доплера.

Для нулевого канала обзора частоте Доплера в процессе накопления накапливаются результаты перемножения одноименного канала во всем интервале накопления. Для других же каналов обзора по частоте Доплера в процессе накопления вначале накапливаются. результаты перемножения одноименного канала, а затем; в зависимости от номера этого канала, а также от требуемой точности вычисления взаимной корреляцианной функции начинают накапливаться результаты перемножения смежного канала и т, д. Переключение процессом накопления осуществляет импульс с соответствующего делителя блока 10, Для повышения точности вычислений, т.е. интервалов, через которые осуществляется накопление, частота дискретизации АЦП 2 и выбрана в и раз выше по сравнению с частотой Котельникова. Значение п полностью определяется требуемой точностью дискретности вычисления взаимной корреляционной функции при обзоре по частоте Доплера.

Рассмотрим работу блока накопителей

14 (фиг. 2).

Блок накопителей 14 содержит М элементов накопления 18. Каждый элемент накопления 18 осуществляет вычисление взаимной корреляционной функции в конкретном диапазоне доплеровских частот, т.е. первый элемент накопления 18> осуществляет обзор от 0 до Жд, второй элемент — от

Д fä до 2(д и т.д. Принцип работы каждого

1727132

20

35

50 хода не нужен, так как этот элемент осуществляет обзор нулевой доплеровской частоты. Этот импульс определяет конец накопления и может использоваться для перезаписи ординат взаимной корреляцион-. 5 ной функции в выходные регистры.

Элемент накопления 18 (фиг. 3) работает следующим образом.

Для пояснения работы элемент накопления приведен для М канала. При поступлении импульса запуска на вход коррелятора этот импульс производит обнуление делителя 26 и счетчиков 23 и 27 элемента накопления (на фиг, 1 связь запуска блока накопления не показана). На информационные входы элемента поступают результаты перемножения. Сразу после прихода импульса запуска счетчика 23 и 27 находятся в нулевом состоянии. При таком состоянии счетчиков на первых выходах дешифраторов 22 и 28 высокий потенциал, что вызывает открывание элементов И 25 и 24, Необходимо отметить, что импульс запуска обнуляет также и накопительный сумматор 21. В этом состоянии на информационный вход накопительного сумматора 21 постуг,ает результат перемножения с первого входа через открытый элемент И 24> и элемент ИЛИ 19, а синхроимпульс — с первого входа первых синхровходов через открытый элемент И

25> и элемент ИЛИ 20. В накопительном сумматоре 21 происходит накопление результата перемножения. При поступлении импульса на второй сийхровход счетчик 23 переключается во второе состояние и высокий потенциал появляется на втором выходе дешифратора 22, что вызывает открывание элемента И 25 . В результате этого на синхровход накопительного сумматора 21 проходят, импульсы с второго входа первых синхровходов, Это приводит к тому, что накапливаться начинает результат перемножения второго синхроимпульса, т,е, код первого АЦП 1 с кодом второго АЦП 2, который синхронизирован $TopblM синхроимпульсом в серии, Так продолжается до следующего прихода импульса на второй синхровход, что приводит к очередному переключению счетчика 23 и как, следствие к переключению синхроимпульса, поступающего на синхровход накопительного сумматора 21, Т.е, в дальнейшем работа элемента накопления аналогична вышеописанному.

Коэффициент деления делителя 26 равен и.

При появлении импульса на выходе делителя 26 счетчик 27 переключается в следующее состояние, что приводит к тому, что высокий потенциал появляется на втором выходе дешифратора 28, что приводит к открыванию элемента И 24 . Все это указывает на то, что на накопление íà пинают пере даваться результаты перемножения следующего канала обработки. Все это указывае на то, что время движения корреляционной точки превысило интервал квантования. Б дальнейшем при появлении импульсов на выходе делителя 26 счетчик 27 переключается в следующее положение и все это приводит к переключению выходного высокого потенциала дешифратора 28 и как следствие к открыванию очередных элементов И

24, В дальнейшем работа элемента накопления аналогична.

Формула изобретения

Цифровой коррелятор, содержащий два аналого-цифровых преобразователя, делитель частоты, регистр сдвига, группу перемножителей, блок накопителей, элементы

И, элементы ИЛИ, счетчик, блок элементов

И, генератор тактовых импульсов, триггер, причем информационные входы первого и второго аналого-цифровых преобразователей являются соответствующими информационными входами коррелятора, вход установки в единицу триггера является входом запуска коррелятора, выход триггера соединен с первым входом элемента И, выход которого соединен с счетным входом счетчика, выход делителя частоты соединен с сдвиговым входом регистра сдвига и синхровходом первого аналого-цифрового преобразователя, выход которого соединен с информационным входом регистра сдвига, выходы группы которого соединены с первыми входами соответствующих .перемножителей группы, вторыЕ входы которых соединены с выходом второго аналого-цифрового преобразователя, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия, в него дополнительно введены блок делителей частоты, элемент задержки, дешифратор, К вЂ” 1 (К вЂ” число каналов обзора по задержке) блоков накопителей, причем выход генератора тактовых импульсов соединен с вторым входом элемента И, .выход которого соединен с информационным входом делителя частоты, с синхровходом второго аналого-цифрового преобразователя и через элемент задержки с управляющим входом блока элементов И, группа информационных входов которого соединена с группой выходов дешифратора, группа входов которого соединена с группой разрядных выходов счетчика, вход обнуления которого соединен с выходом элемента

ИЛИ, первый вход которого соединен с информационным входом блока делителей частоты и выходом делителя частоты, вход установки которого соединен. с входом установки блока делителей частоты, с вторым

1727132 входом элемента ИЛИ и подключен к входу запуска коррелятооа, информационные входы группы l-ro (l=1 ) блока накопителей соединены с выходами соответствующих перемножителей группы, группы синхровходов i-го блока накопителей соединены с группой выходов блока элементов И, группы тактовых входов блока накопителей соединены с группой выходов блока делителей частоты, первый выход которого соединен с входом установки в ноль триггера, группы

Б выходов блоков накопителей являются группами выходОв одинаковой доплеровской частоты коррелятора.

1727132

@uz. 2

1727132

Составитель В.Орлов

Техред M.Mîðãåíòàë Корректор Э.Лончакова

Редактор Н.Каменская

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 1279 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5