Устройство для поклеточного умножения матриц

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в составе специализированных матричных вычислителей. Цель изобретения - повышение быстродействия. Цель достигается тем, что в устройство, содержащее М2 регистров (М - порядок перемножаемых матриц), М2 блоков вычисления скалярного произведения и блок синхронизации, введены М мультиплексоров и М2 групп элементов И. Перед началом работы в регистры записывается числовая управляющая матрица, в соответствии с которой происходит отключение соответствующих входов блоков вычисления скалярного произведения в процессе работы, и таким -образом, происходит поклеточное умножение матриц. Зил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК" (51)5 G 06 F 15/347

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ. ГКНТ СССР

10 (>

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4710747/24 (22) 26.06.89 (46) 15.04.92. Бюл. № 14 (71) Институт кибернетики им. В. М. Глушкова (72) В. А, Вышинский, Б, М. Тихонов и Н. Б.

Фесенко (53) 681.3(088,8) (56) Авторское свидетельство СССР

¹ 647687, кл. 6 06 F 15/347, 1976, Авторское свидетельство СССР

¹ 1444819, кл. G 06 F 15/347, 1986. (54) УСТРОЙСТВО ДЛЯ IlOIGlETO×HOÃÎ

УМКОЖЕНИЯ МАТРИЦ (57) Изобретение относится к автоматике и вычислительной технике и может быть исИзобретение относится к автоматике и вычислительной технике и может быть использовано в составе специализированных вычислительных машин для перемножения матриц.

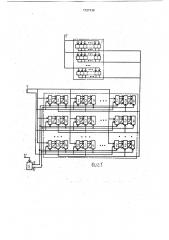

Цель изобретения — повь:шение быстродействия. . На фиг. 1 показана структурная схема устройства; на фиг. 2 — пример выполнения

M-разрядного мультиплексора; на фиг. 3— схема соединения элементов И в группе.

Устройство (фиг. 1) содержит М регистров 1 (М-порядок обрабатываемых матриц), М2 мультиплексоров 2, М групп 3 элементов И, M блоков 4 вычисления скалярного произведения векторов, блок 5 синхронизации, первую 6, вторую 7 и третью 8 группы информационных входов устройства, второй 9 и первый 10 выходы блока синхрони„„. Ж„„172713б А1 пользовано в составе специализированных матричных вычислителей. Цель изобретения — повышение быстродействия. Цель достигается тем, что в устройство, содержащее

M регистров (М вЂ” порядок перемножаемых

2 матриц), М2 блоков вычисления скалярного произведения и блок синхронизации, введены М мультиплексоров и М групп элементов И. Перед началом работы в регистры записывается числовая управляющая матрица, в соответствии с которой происходит отключение соответствующих входов блоков вычисления скалярного произведения в процессе работы, и таким -образом, происходит поклеточное умножение матриц. 3 ил. зации, вход 11 начальной установки устройства.

Каждый мультиплексор (фиг. 2) может содержать 2М триггеров 12, M элементов

И-ИЛИ 13 и управляющий вход мультиплек- 3 сора 14. и

Каждая группа 3 элементов И (фиг. 3) () содержит М элемент>в И 15, (Устройство для поклеточного умножения матрицы перемножает матрицы A=)l А Я и B=f18>II/ с различными размерами клеток.

Каждому размеру клеток соответствует своя управляющая числовая. матрица, которая перед началом работы через информационные входы устройства. первой группы записывается в регистры 1. Для обычного умножения матриц (размер клетки равен размерности матрицы) значение числовой

-управляющей матрицы равно нулю, во все

1727136 разряды регистров 1 записываются нулевые значения.

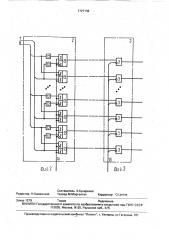

Через вторую группу информационных входов 7 на первые информационные входы мультиплексоров 2 поступают значения .разрядов элементов векторов — строк матрицы А, через третью группу информационных входов 8 на вторые информационные входы мультиплексоров 2 поступают значения разрядов элементов векторов — столбцов матрицы В, которые синхронизируются по управляющему входу мультиплексора.

На выходах нечетных элементов И вЂ” ИЛИ 13, мультиплексоров 2 образуются пары а2 be, а4| Ь!4, ..., amI birn, а2| Ь|2 .1 п 1 и 1 и. 2 и-1

a4I Ь!4

2 п-1., n 1

amI Ь!и, .... а2| Ь!г, a4I Ь!4, amI" birn, где n — разрядность элементов матриц, i=1.М. j=1,М. На выходах четных элементов

И-ИЛИ 13 образуются пары: а1 Ьп, аз| Ь!з, ..., ап|-1I birn-1, а1| Ьп .! n 1 п 1 п, 2 и-1 аз1 Ь з а|п-1| Ь!п-1" ",...,а1|"Ь!2 аЗ|"Ь|З ...ап-1|"

1.

ЬЬ-1 °

Нулевые сигналы с выходов k ro регистра (М=1.М1 ) поступят на вторые входы элементов И k-й группы и k-я группа элементов

И пропустит информацию с k-го мультиплексора без изменения, По окончании работы устройства в блоках 4 вычисления скалярного произведения векторов образуется результат умножения матриц.

Для случая, отличного от обычного умножения матриц, числовая управляющая матрица содержит информацию, соответствующую предстоящему вычислительному процессу. Каждая числовая управляющая матрица соответствует размеру клеток — сомножителей и указывает, какую часть образованных k-м мультиплексором 2 пар элементов матриц |1АЦИ и 1|Е,цЦ необходимО отключить в ходе вычислительного процесса. Отключение производится подачей единичного сигнала с выхода i-ro разряда k-го регистра 1 на второй вход I-го элемента И

5 k-й группы.

Поклеточное произведение матриц

C=AB вычисляется устройством, как поэлементное произведение матриц, в которых элементами выступают клетки НА||!1и 1!В Я то

10 есть llC|)l=fl4|JВ|gll, Формула изобретения

Устройство для поклеточного умножения матриц, содержащее M регистров (M—

15 порядок обрабатываемых матриц), М2 блоков вычисления скалярного произведения векторов и блок синхронизации, первый выход которого подключен ко входам запуска блоков вычисления скалярного произведе20 ния векторов информационный вход k ãî регистра (k=1,М ) является k-м информационным входом первой группы устройства, вход начальной установки блока синхронизации является одноименным входом уст25 ройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройство содержит М М-разрядных мультиплекг соров и M групп элементов И, причем

В

- выход 1-.го разряда k-ro мультиплексора

30 ||=1.М) соединен с первым входом!-го элемента И k-й группы, второй вход которого соединен с выходом i-ro разряда k-ro регистра, выход I-ro элемента И k-й группы соединен с 1-м информационным входом k-ro

35 блока вычисления скалярного произведения векторов, первый и второй информационные входы k ro мультиплексора являются информационными входами соответственно второй.и третьей групп устройства, вто40 рой выход блока синхронизации подключен к управляющим входам всех мультиплексоров.

1727136

1727136

Составитель К.Кухаренко

Редактор Н.Каменская Техред М.Моргентал Корректор О.ципле

Заказ 1279 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул, Гагарина, 101