Устройство для умножения s-х цифр в позиционно-остаточной системе счисления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных устройств , работающих в позиционно-остаточной системе счисления. Цель изобретения - сокращение аппаратурных затрат. В устройство , содержащее два коммутатора 14, 15, два блока 1,2 хранения констант, два блока 5, 6 умножения, первый элемент 7 задержки , шесть блоков 8-13 элементов И и два сумматора 3, 4, введены второй элемент 26 задержки, два регистра 24 и 25 и два мультиплексора 22 и 23, что позволило вывести из состава устройства два блока умножения, объем которых во много раз превышает объем введенных блоков. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (s1)s G 06 F 7/72

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ (21) 4700100/24 (22) 02.06.89 (46) 30.04;92. баюл, ¹ 16 4 (л)

О ()с

М

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (72) В.Г.Евстигнеев, А.Н. Кошарновский и С.Е.Ревзин (53) 681,325(088.8) (56) Авторское свидетельство СССР № 1236472, кл. G 06 F 7/72, 1984.

Авторское свидетельство СССР

¹ 1633401, кл. G 06 F 7/72, 1989. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ S-X

ЦИФP В ПОЗИЦИОННО-ОСТАТОЧНОЙ

СИСТЕМЕ СЧИСЛЕНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных устройств, работающих в позиционно-остаточной системе счисления. Цель изобретения— сокращение аппаратурных затрат. В устройство, содержащее два коммутатора 14, 15, два блока 1, 2 хранения констант, два блока

5, 6 умножения, первый элемент 7 задержки, шесть блоков 8-13 элементов И и два сумматора 3, 4, введены второй элемент 26 задержки, два регистра 24 и 25 и два мультиплексора 22 и 23, что позволило вывести из состава устройства два блока умножения, объем которых во много раз превышает объем введенных блоков. 3 ил.

1730625

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих арифметических устройств, работающих в позиционно-остаточной системе счисления.

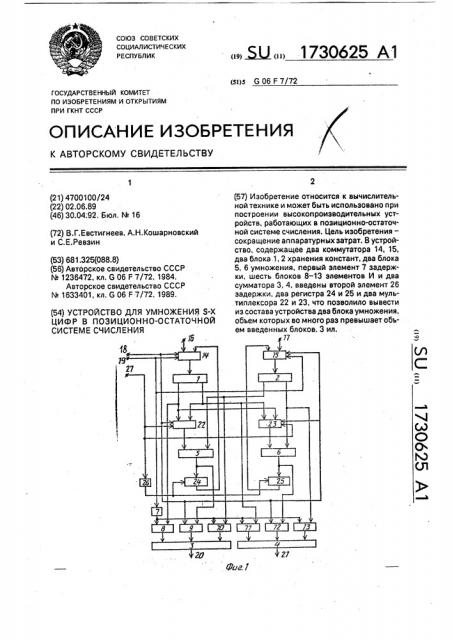

Цель изобретения — сокращение аппаратурных затрат, На фиг, 1 представлена функциональная схема устройства; на фиг, 2 — временная диаграмма токовых сигналов; на фиг. 3— функциональная схема мультиплексоров.

Устройство содержит два блока 1 и 2 хранения констант, два сумматора 3 и 4, два блока 5 и 6 умножения, первый элемент 7 задержки, шесть блоков 8 — 13 элементов И, два коммутатора 14 и 15, входы первого 16 и второго 17 операндов устройства, первый

18 и второй 19 тактовые входы устройства, выходы старшего 20 и младшего 21 разрядов произведения устройства, два мультиплексора 22 и 23, два регистра 24 и 25, второй элемент 26 задержки и третий 27 тактовый вход устройства.

В основу работы устройства для умножения S-x цифр в позиционно-остаточной системе счисления положено следующее.

Запишем произведение двух S-x цифр в виде а. b = (а1 + ao)(b1 1/ $ + bo) =

= а1Ь1 S + aob1 $ + a1bo $+

+ аоЬо = f1S + foS

1 о

Запишем второе и третье слагаемое в виде

apb1S a1bpS 1

+ — c1S + со + d1S + dp, 1

S S где fi = a1b1+ с1+ d1;

fo = аоЬо+ со + оо ао = rest(a/ V/$);

a1= ent(a/ Vá$);

Ь = гезу(Ь/ 4/$);

Ь1= ent(b/ V $); со = rest (aob1/ V/$);

С1 = ЕМ (аоЬ1/ I/$);

dp = test(a1bo/ /$);

d1= ent(a1bo/ V $) где rest (X/Y) — остаток от деления X íà У;

ent (X/Y) — целое частное от деления X на Y.

Известно, что цифры в S-й позиционноостаточной системе счисления представля5 ются по модулям системы (СОК) в виде а = (а1, аг,..., ак );

Ь =(P1,Д ..,.,Д), 10 где а; = rest(a/Ð;);

j3; = rest (b/Р;);

)=1,К;

P1 — модули СО К, удовлетворяющие ус15 ловию П PI o 2S (простые числа).

) — — 1

Для согласования с устройствами, работающими в двоичной системе счисления,в позиционно-остаточных устройствах обычно выбирают S = 2m, Удобнее всего принять

m = 8 и соответственно S = 2 = 256, а с еди

8 модулей СОК иметь один, равный $, в частном случае пусть P1 = 91256 = 16, Это позволяет при аппаратной реализации блоков 1 и 2 хранения констант получить экономичные решения.

Устройство для умножения S-x цифр в позиционно-остаточной системе счисления работает следующим образом.

По первому тактовому сигналу, поступающему на устройство по входу 18, А =

= (а1, аг,..., а, ) и В = (p1, Д,..., />, ), представленные кодом СОК по модулям Р1, 35 P2, „., PK, по входам 16 и 17 поступают на. коммутаторы 14 и 15, с выходов которых передаются на входы соответствующих блоков 1 и 2 хранения констант. Эти блоки конструктивно представляют собой блоки

40 постоянной памяти íà 2I-разрядных слов

К каждый, где! =, I; II — двоичная разряд)=1 ность вычета й1 или pj, B этих блоках в соот45 ветствии с выражением (3) формируются величины а1, ао и Ь1, bp соответственно. Величина а с первого выхода блока 1 хранения констант через первый информационный вход первого мультиплексора 22 поступает на его выход, с которого поступает на первый вход первого блока 5 умножения, на второй вход которого с первого выхода второго блока 2 хранения констант поступает величина b1. Одновременно с второго выхода первого блока 1 хранения констант величина о поступаег на первый информационный вход второго мультиплексора 23, открытый первый вход второго блока 6 умножения, на второй вход которого с второго выхода блока 2 хранения констант поступа1730625

15

25

40

50

55 ет величина Ьо; С выхода первого блока 5 умножения величина аоЬО поступает на первый вход второго блока 9 элементов И, пройдя который, поступает в первый сумматор 3. С выхода второго блока 6 умножения величина aobo поступает на первый вход пятого блока 12 элементов И, пройдя который, поступает во второй сумматор 4; Через некоторое время на устройство поступает третий тактовый сигнал по входу 27 (см. фиг.

2), По этому сигналу закрываются первые информационные входы мультиплексоров

22 и 23 и открываются их вторые информационные входы. На их выходах появляются соответственно величины ао и а1, поступающие на первые входы соответственно блоков 5 и 6 умножения, на вторые входы которых поступают величины Ьо и b1. На выходах блоков 5 и 6 умножения формируютсЯ величины aob1 и а1Ь,, котоРые по третьему тактовому сигналу, задержанному на элементе 26 задержки, заносятся соответственно на первый 24 и второй 25 реги.стры. После этого снимаются первый по входу 16 и третий по входу 27 тактовые сигналы. На этом заканчивается первый такт работы устройства, Второй такт работы устройства начинается снятием с первого 18 и третьего 27 тактовых входов сигналов и подачей на второй тактовый вход 19 устройства сигнала (фиг. 2), По этому сигналу величины аоЬ1 и

a1bo через коммутаторы 14 и 15 проходят на входы блоков 1 и 2 хранения констант, на первых и вторых выходах которых формируются величины с1со и d1do. К этому времени задержанный первым элементом 7 задержки второй тактовый сигнал открывает по вторым входам блока 8, 10, 11 и 13 элементов И, на первые входы которых с выходов первого 1 и второго 2 блоков хранения констант поступают величины с1, d1, cp, do coответственно и, пройдя их, поступают в соответствующие сумматоры 3 и 4. В результате, в этих сумматорах формируются старший и младший S-e разряды произведения S-x цифр в позиционно-остаточной системе счисления.

Формула изобретения

Устройство для умножения S-x цифр в позиционно-остаточной системе счисления, содержащее два блока хранения констант, два коммутатора, два блока умножения, первый элемент задержки, шесть блоков элементов И и два сумматора, выходы которых соединены соответственно с выходами старшего и младшего разрядов произведения устройства, входы первого и второго операндов которого соединены соответственно с информационными входами первой группы первого и второго коммутаторов, первые управляющие входы которых соединены с первым тактовым входом устройства и первыми входами элементов И первого и второго блоков, вторые входы которых соединены соответственно с выходами первого и второго блоков умножения, выходы первого и второго коммутаторов соединены соответственно с входами первого и второго блоков хранения констант, первый выход первого блока хранения констант соединен с первыми входами элементов И третьего блока, вторые входы которых соединены с первыми входами элементов И четвертого, пятого и шестого блоков и выходом первого элемента задержки, вход которого соединен с вторыми управляющими входами первого и второго коммутаторов, второй выход первого блока хранения констант соединен с вторыми входами элементов И пятого блока, первый выход второго блока хранения констант соединен с входом первого сомножителя первого блока умножения.и вторыми входами элементов И четвертого блока, второй выход второго блока хранения констант соединен с входом первого сомножителя второго блока умножения и вторыми входами элементов И шестого блока, выходы элементов И третьего, первого и четвертого блоков соединены соответственно с входами первого, второго и третьего слагаемых первого сумматора, выходы элементов И пятого, второго и шестого блоков соединены соответственно с входами первого, второго и третьего слагаемых второго сумматора, о т л и ч а ю щ е е с я тем, что. с целью сокращения аппаратурных затрат, в него введены два мультиплексора, два регистра и второй элемент задержки, выход которого соединен с управляющими входами первого и второго регистров, выходы которых соединены с информационными входами второй группы первого и второго коммутаторов соответственно, а информационные входы— соответственно с выходами первого и второго блоков умножения, входы вторых сомножителей соединены соответственно с выходами первого и второго мультиплексоров, первые управляющие входы которых соединены с первым тактовым входом устройства, третий тактовый вход которого соединен с входом второго элемента задержки и вторыми управляющими входами первого и второго мультиплексоров, информационные входы первой группы которых соединены с первым выходом первого блока хранения констант, второй выход которого соединен с информационными входами второй группы первого и второго мультиплексоров, 1730625

Г7 биг. 8

45

Составитель Е.Мурзина

Редактор Л.Пчолинская Техред М.Моргентал Корректор Н, Ревская

Заказ 1512 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 б;)

Ec f3 (а)

Ио (И1)

3U 2,3

3, d0) (С) Qi6f Q0 50

Qo gl а1 80