Устройство цикловой синхронизации

Иллюстрации

Показать всеРеферат

Изобретение относится к технике передачи дискретной информации. Цель изобретения - упрощение устройства. Устройство содержит регистр сдвига 1, мультиплексор 2, блок 3 сравнения, регистр 4 эталона, блок 5 опроса каналов, блок 6 управления. Устройство позволяет на одном и том же оборудовании производить обработку информации , поступающей от нескольких источников , организованных по принципу байтового временного уплотнения, что приводит к достижению поставленной цели. 8 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУбЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ь ,Сл) О (д) (л)

> (21) 4626779/09 (22) 26.12,88 (46) 30.04,92. Бюл, N 16 (72) B.Í. Данилов, Д.В. Паниткин. В,Ц. Жапов и А.Н. Петрунин (53) 621.396.662(088.8) (56) Авторское свидетельство СССР

N 512592, кл. Н 04 (7/10, 1973.

Авторское свидетельство СССР

N -563737,,кл. Н 04 L 7/08, 1975.

Авторское свидетельство СССР

¹ 11110044667799,, кКл, Н 04 1. 7/08, 1983.

Устройство относится к технике передачи дискретной информации, в частности к устройствам синхронизации по циклам и кадрам.

Цель изобретения — расширение функциональных возможностей путем обработки многоканальных сигналов со знаковым уплотнением, поступающих от нескольких источников.

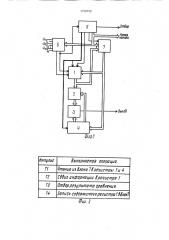

Структурная схема устройства приведена на фиг. 1; на фиг. 2 — программа работы устройства; на фиг. 3 — организация блока памяти; на фиг. 4 — структурная схема регистра эталона; на фиг, 5 — блок-схема мультиплексора и программа управления его работой; на фиг. 6 — структурная схема блока управления; на фиг. 7 — временная диаграмма входного сигнала и импульсов управления; на фиг. 8 — структурная схема блока опроса каналов, Устройство содержит регистр 1 сдвига. мультиплексор 2, блок 3 сравнения. регистр

4 эталона, блок 5 опроса каналов. блок 6

„„Ы2„„1730733 А1 (s»s Н 04 L 7/08. Н 04 J 3/06 (54) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ (57) Изобретение относится к технике передачи дискретной информации, Цель изобретения — упрощение устройства, Устройство содержит регистр сдвига 1, мультиплексор

2, блок 3 сравнения, регистр 4 эталона, блок 5 опроса каналов, блок 6 управления.

Устройство позволяет на одном и том же оборудовании производить обработку информации, поступающей от нескольких источников, организованных по принципу байтового временного уплотнения, что приводит к достижению поставленной цели, 8 ил. управления и блок 7 памяти. Мультиплексор

2 содержит битовые коммутаторы 8. Блок 6 управления содержит генератор 9, счетчик

10, дешифратор 11 и элемент И 12. Блок 5 опроса каналов содержит триггеры 13.1l3.п и 14.1-14.п. мультиплексоры 15, 16, дешифратор 17 и формирователи коротких импульсов 18.1 — 18,п.

Устройство производит опрос входных каналов со знаковой структурой цикла информации и поиск в каждом канале синхрокомбинации. Для каждого канала синхрокомбинации может иметь свое значение и разрядность.

Устройство работает следующим образом.

Перед началом работы производится нулевая начальная установка всех блоков и элементов устройства. В блок 7 памяти в область хранения эталона производится запись эталонных искомых синхрокомбинаций и их длин в соответствии с номером канала. Цепи установления начальных усло1730733

55 вий и занесения настроечных данных, а также цепи синхронизации не показаны.

Блок 5 опроса с помощью тактовых импульсов производит побитную регистрацию входной информации на триггерах 14 независимо по каждому каналу. По номеру канала, поступающему от блока управления 6, на выход блока 6 подается зарегистрированное значение информационного бита и сигнала "Запрос", который формируется по тактовому импульсу, сопровождающему информационный бит. Наличие сигнала "Запрос" свидетельствует о том, что на вход устройства по данному каналу поступил очередной информационный бит, Блок 6 управления на каждом цикле обработки информации одного канала формирует четные управляющие импульсы (фиг, 6 и 7), В начале цикла обработки блок 6 устанавливает адрес очередного канала. По управляющему импульсу Т, действующему на первом входе блока 6, в регистр 4 заносятся значения эталонной синхрокомбинации опрашиваемого канала и ее длина из области хранения эталона блока 7 памяти. Длина регистра 4 составляет (Р+А) бит, где Р— разрядность максимальной синхрокомбинации, А — количество разрядов, в которые записывается код длины комбинации. Одновременно из области хранения входной информации блока 7 производится чтение информации, накопленной по данному каналу. Считанная информация заносится в регистр сдвига 1, разрядность которого равна P.

По управляющему импульсу Т2 при наличии сигнала запроса от блока 5 производится сдвиг содержимого регистра 1 на один разряд и запись в него очередного входного бита из блока 5.

Мультиплексор 2 подключает ко входам блока 3 сравнения то количество разрядов регистра 1, которое было задано настроечным словом, записанным в младших разрядах регистра эталона 4. На другую группу входов блока 3 со старших разрядов регистра 4 поступает эталонная синхрокомбинация.

При обнаружении синхрокомбинации блок 3 подает на выход устройства импульс сравнения, Момент отбора результата поиска onределяется по сигналу "Отбор", формируемому управляющим импульсом Тз.

Формирование импульса Тз в блоке 6 управления производится только при наличии управляющего сигнала "Запрос" от блока 5.

Принадлежность результата поиска определяется на выходе устройства по номеру канала, поступающего от блока 6, 5

Затем по управляющему импульсу Т4 по адресу этого же канала в блок 7 памяти записывается содержимое регистра 1, Затем блок 6 управления, меняет номер канала и программа работы устройства (фиг.

2) повторяется, но уже с данными нового канала, В случае отсутствия сигнала "Запрос" работа устройства по данному каналу сводится к чтению накопленных данных и настроечных данных в соответствующие регистры и последующему занесению их обратно в блок памяти, т,е. происходит сохранение накопленных данных.

Чтобы избежать потерь входной информации, время обработки всех каналов должно быть меньше наименьшей длительности информационного бита самого скоростного канала, Таким образом осуществляется многоканальная обработка сигналов с синхрокодами в виде знака.

На фиг,З представлена структура организации блока памяти 7. Весь объем блока памяти делится на область хранения входной информации и область хранения эталона (эталонной синхрокомбинации и ее длины), Разделение этой информации производится соответствующей разрядностью, а разделение информации каналов задается соответствующей адресацией. Область хранения эталона используется только в режиме чтения.

На фиг.5а представлена структурная схема мультиплексора 2, на фиг, 5,б — программа его работы. Под длиной здесь подразумевается количество информационных разрядов, пропускаемых мультиплексором

2 на блок сравнения, остальные разряды будут лог, нулями, соответственно записывается и настроечное слово в блок памяти, Мультиплексор имеет четыре разряда и состоит из битовых коммутаторов 8.

На фиг, 6 представлена структурная схема блока 6 управления, состоящего из генератора 9, счетчика 10, дешифратора 11 и элемента И 12, причем выход младших разрядов счетчика 10 подключен к дешифратору 11, на выходах которого формируются управляющие импульсы, а выходы старших разрядов счетчика 10 являются выходом номера канала. Третий импульс управления и сигнал "Запрос" с выхода блока 5 опроса каналов поступает на соответствующие входы элемента И 12, выход которого является выходом отбора информации устройства, На фиг. 7 представлены временные диаграммы входного сигнала: а — информационный бит, б — тактовый импульс и управляющие импульсы блока 6 управле. 1730733

55 ния; в, г, д, е — соответственно импульсы

Т -Т4 управления, По перепаду 0 — 1 сопровождающего тактового импульса триггер 13 данного канала устанавливается в состояние лог. 1.

Выходной сигнал этого триггера по тактовому входу управляет триггером 14 этого же входного канала. По перепаду 0 — 1 на выходе тактового триггера 13 триггер 14 устанавливается в состояние входного информационного сигнала, т.е. производится регистрация информационного значения данного входного канала. По адресу опрашиваемого канала мультиплексорами 15 и

16 производится коммутация значений соответствующих триггеров (установленных в значениях входного сигнала, т.е, информационного и тактового значений) на выходы блока, Наличие сигнала "Запрос" (взведен триггер 13 по поступившему тактовому импульсу) по данному каналу говорит о том, что в устройстве содержится по данному каналу информация, требующая обработки и поступающая на выход блока через мультиплексор 15. Обнуление информационного триггера 14 и тактового триггера 13 — одного канала производится при переходе к следующему.

Применение изобретения позволяет сократить объем оборудования по каждому каналу по сравнению с устройством-прототипом за счет применения блока памяти для накопления информации и хранения эталонных синхрокомбинаций.

Формула изобретения

Устройство цикловой синхронизации, содержащее последовательно соединенные регистр сдвига и блок памяти, последовательно соединенные регистр эталона и блок сравнения, а также мультиплексор и блокуправления,отл ичаю щееся тем, что, с целью расширения функциональных

5 возможностей путем обработки многоканальных сигналов со знаковым уплотнением, поступающих от нескольких источников, введен блок опроса каналов, при этом информационный выход блока опроса каналов

10 соединен с информационным входом регистра сдвига, управляющий вход которого соединен с выходом сигнала запроса блока опроса каналов и со входом блока управления, выход сигнала "Номер канала" которо15 го соединен с адресными входами блока опроса каналов и блока памяти, выходы блока памяти соединены с входами параллельной информации регистра сдвига и регистра эталона, другие выходы регистра эталона

20 соединены с управляющими входами мультиплексора, ко входам которого подключены выходы регистра сдвига, а выходы мультиплексора соединены с другими входами блока сравнения, первый выход блока

25 управления соединен с управляющими входами параллельной записи регистра эталона и регистра сдвига, управляющий вход сдвига регистра соединен со вторым выходом блока управления, третий выход кото30 рого соединен с входом чтения) запись блока, причем информационные входы и тактовые входы блока опроса каналов и информационный выход блока сравнения являются соответственно информационными, 35 тактовыми входами и информационным выходом устройства, выходами сигнала отбора информации и номера канала которого являются соответствующие выходы блока управления.

1730733

Отбор

НамеР анала

1730733

ХЛОкаг1 1ы

Оадлокаб От блока 7

КУлпк а,4

К 670/

1730733

К &оку5

Уар. сигналы ймео канат

Ombre

1730733

Тамп

gnр. игю 71

Упр.

Й ФП U

Упр. июп 73

Упр.

gptff, T4

Фггг. T

И1

r, tï

Тп рос

OKQH иБ

Ваг,в

Составитель В.Микуцикий

Техред М.Моргентал Корре ор Э,Лончакова

Реда кто р Т. Орл овс кая

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101

Заказ 1518 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35. Раушская наб., 4/5