Частотный детектор

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и может быть использовано для демодуляции , частотно-модулированных сигналов в телевизионных приемниках системы СЕ- КАМ Цель изобретения - повышение точности детектирования. Частотный детектор содержит информационный вход и вход сигнала синхронизации, квадраторы, элемент задержки сумматоры, умножители, делитель , инвертор, коммутаторы, элементы памяти , выход, фазовращатели. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ, КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

О ,(лЭ

i (21) 4820763/09 (22) 03.05,90 (46) 30,04,92. Бюл, N" 16 (71) Таганрогский научно-исследовательский институт связи (72) И,Г,Дорух, А,П. Дорух и В.Г. Косторниченко (53) 621,397(088,8) (56) Авторское свидетельство СССР

N1483591,,кл. Н 03 NЗ/00,,1987.

Изобретение относится к радиотехнике и может быть использовано для демодуляции частотно-модулированных сигналов в телевизионных приемниках системы СЕКАМ.

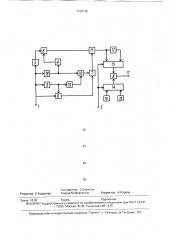

Цель изобретения — повышение точности детектирования, На черте>ке представлена электрическая структурная схема частотного детектора.

Частотный детектор содержит информационный вход 1 и вход 2 сигнала синхронизации частотного детектора, первый 3 и второй 4 квадраторы, элемент задержки 5. третий сумматор 6, второй сумматор 7. первый сумматор 8. первый 9 и второй 10 умножители, делитель 11. инвертор 12, первый

13 и второй 14 коммутаторы. первый 15 и второй 16 элементы памяти выход 17 частотного детектора, первый 18 и второй 19 фазовращатели, Частотный детектор работает следующим образом, Входной частотно-модулированный сигнал U»x(t) вида!

Ы 1730738 А1 (лис Н 04 N 9/00; Н 03 О 3/00 (54) ЧАСТОТНЫЙ ДЕТЕКТОР (57) Изобретение относится к радиотехнике и может быть использовано для демодуляции частотно-модулированных сигналов в телевизионных приемниках системы СЕKAM. Цель изобретения — повышение точности детектирования. Частотный детектор содержит информационный входи вход сигнала синхронизации, квадраторы, элемент задержки. сумматоры, умножители, делитель, инвертор, коммутаторы, элементы памяти, выход, фазовращатели. 1 ил.

U))x(t)= R cos rr>t, (1) где t — текущее время;

R и (о — амплитуда и круговая частота

Входного сигнала, через информационный вход частотного детектора поступает на входы фазовращателя 18, первого квадратора 3, элемента

5 задержки и первого умножителя 9.

Первый фазовращатель 18 осуществляет поворот фазы сигнала на л /2. На его выходе формируется сигнал U<(t), который может быть записан в виде

Uq(t) = R cos(o>t+ л/2)= — R sin rr>t (2/ )

Этот сигнал с выхода первого фазовращателя 18 поступает на вход второго квадратора 4 и на второй вход второго умн о >кител я 10.

Элемент 5 задержки осуществляет задержку входного сигнала на период T тактовой частоты. На его выходе формируется сигнал 0® вида

1730738

U5(t) = КЗВ (8) (4) + сов(2 вт-вr)) (5) U11(t)=cos вr

05 (t) = R с08 (в (t )) 1 (3) который поступает на вход второго фазовращателя 19 и на вход первого умножителя 9.

Первый умножитель 9 осуществляет перемножение поступающих на его вход сигналов Uex(t) и Ue(t) и íà его выходе формируется сигнал U5(t), который может быть записан в виде г

Ug(t) = KgUei(t)U5(t) = К9 — (cos в + где Kg — коэффициент передачи первого умножителя 9, Этот сигнал поступает на вход второго сумматора 7, Второй фазовращатель 19 осуществляет поворот фазы сигнала 05() на л/2. На

его выходе формируется сигнал U2(t), который может быть записан в виде

U2 (t) — R COS (в (t — t:) + — )— — R sin (в(с — г)), Этот сигнал с выхода второго фазовращателя 19 поступает на первый вход второго умножителя 10.

Второй умножитель 10 осуществляет перемножение поступивших на его входы сигналов U1(t) и 02(t). На его выходе формируется сигнал U10(t), который может быть записан в виде

R2

U10(t) = R1001(t)U2(t) = K10 — х(сов cut — cos(2 в t — вг)). (6) Этот сигнал поступает на вход второго сумматора 7.

Первый 3 и второй 4 квадраторы осуществляют возведение в квадрат поступающих на их входы сигналов и на их входах формируются сигналы соответственно Us(t) и 04(t), которые могут быть записаны в виде

Ua(t) = Кз0,2(t) = Кзйг cosг в1, U4(t) = К401 (t) = K4R sit1 в t; где Кз и К4 — коэффициенты передачи первого 3 и второго 4 квадраторов соответственно.

Сигналы Uz(t) и U4(t) поступают на входы третьего сумматора 6. На его выходе формируется сигнал 05(t), определяемый равенством

Ua(t) = U (t) + U4(t) = R (Кз cos в t+

+ K4sin вт) (7)

5 При выборе коэффициентов Кз и К4 получим

10 Таким образом, на выходе третьего сумматора 6 формируется постоянный сигнал, уровень которого пропорционален квадрату амплитуды входного сигнала. Этот сигнал поступает на вход делителя 11.

15 На выходе второго сумматора 7 формируется сигнал U7(t), равный сумме поступающих на его входы сигналов Ug(t) и U10(t) U7(t) = Ug(t)+0 10(t)

При выборе коэффициентов Kg=K10 получим

R2

07(с) = Kg — cos вt

2 (9)

Этот сигнал поступает на вход делителя 11, На его выходе формируется сигнал

011(t), пропорциональный отношению поступающих на его входы сигналов

U11(t) = К11 = сов в с, (10)

0 » К11КО

L4 (t) 2 Кз где К11 — коэффициент передачи делителя.

Выбирая коэффициенты Кз, Kg и К11 из

К11К9 условия = 2, получим

Кз

Сигнал 011(т) поступает на информационный вход первого коммутатора 13 и на вход инвертора 12. На выходе инвертора 12 формируется инверсный сигнал

U12(t) = U11(t) = cos (l) т, который поступает на другой информациОнный ВХОД перВого коммутатора 13.

На первый и второй информационные входы второго коммутатора 14 поступают сигналы 015 и 015.

Первый 13 и второй 14 коммутаторы управляются сигналом цветовой синхронизации полустрочной частоты, поступа;Ощим на их управляющие входы с входа 2 частотного детектора, на который он в свою очередь поступает со схемы цветовой синхрониза1730738

50

55 ции цифрового декодера системы СЕКАМ.

Под воздействием этого сигнала первый . коммутатор 13 подключает периодически от строки к строке к первому входу первого сумматора 8 сигнал 08в-4, а второй коммутатор 14 подключает к второму входу первого сумматора 8 сигнал USR-у. В результате на выходе первого сумматора 8 и выходе 17 частотного детектора поочередно от строки к строке будут формироваться сигналы

08в-У = 015+ cos (вв — y г)

08в-У = 0ю — cos (и я — y т), (11) где вв — y и вр — y — круговые частоты цветоразностных сигналов  — У и R — Y соответстве н но.

Уравнения (11) можно записать в виде

08в-y= Uл+cos ((в +Лвв — y)г) =

=

= f c0 — y cos (A o)o к — y 7), где во — круговая резонансная частота цепи высокочастотных предискажений системы

СЕ КАМ, Лй4 в — y, ЛN> R — у — частотные сдвиги нулевых поднесущих цветоразностных сигналов В-Y u R — Y соответственно, Формула изобретения

Частотный детектор, содержащий первый квадратор, первый и второй сумматоры, инвертор, делитель, первый коммутатор, первый и второй информационные входь. которого соединены соответственно с входом и выходом инвертора, а выход — с первым входом первого сумматора, выход

5 которого является выходом частотного детектора, второй коммутатор, первый и второй элементы памяти, выходы которых соединены соответственно с первым и вторым информационными входами второго

10 коммутатора, управляющий вход которого объединен с управляющим входом первого коммутатора и является входом сигнала синхронизации частотного детектора, а также элемент задержки, вход которого объе15 динен с входом первого квадратора и является информационным входом частотного детектора, о т л и ч а ю щ и,й с я тем, что, с целью повышения точности детектирования, в него введены второй квадратор, 20 первый умножитель, первый вход которого соединен с входом элемента задержки, а выход — с первым входом второго сумматора, последовательно соединенные первый фазовращатель, вход которого соединен с

25 входом первого квадратора, и второй умножитель, выход которого соединен с вторым входом второго сумматора, третий сумматор, первый вход которого соединен с выходом первого квадратора, второй вход — с

30 выходом второго квадратора, вход которого соединен с выходом первого фазовращателя, а выход — с первым выходом делителя, второй вход которого соединен с выходом второго сумматора, а выход — c входом ин35 вертора, а также второй фазовращатель, вход которого объединен с вторым входом первого умножителя и с выходом элемента задержки, а выход соединен с вторым входом второго умножителя.

1730738

40

50

Составитель Э.Борисов

Техред М,Моргентал Корректор Н,Король

Редактор 3.Ходакова

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 1518 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб„4/5