Таймер

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, может быть использовано в управляющих вычислительных системах для обеспечения работ в реальном масштабе времени. Целью изобретения является повышение достоверности функционирования таймера за счет исключения возможности выдачи ложного кода. Поставленная цель достигается тем, что выход первого разряда группы разрядных выходов счетчика соединен с третьим входом формирователя сигнала чтения, содержащего триггер, элементы И и НЕ, в который введены элементы И и ИЛИ. 1 з.п.ф-лы, 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si)s G 06 F 1/04

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ф

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1531081 (21) 4832353/24 (22) 31.05.90 (46) 07.05.92. Бюл. ¹ 17 (71) Специальное конструкторское бюро

Производственного объединения "Коммунар" (72) B.À.Ñåëèsàíoâ и А.П.Шляхов (53) 681.3(088,8) (56) Авторское свидетельство СССР № 1531081, кл. G 06 F 1/04, 1988, (54) ТАЙМЕР

Изобретение относится к вычислительной технике, может быть использовано в управляющих вычислительных системах для обеспечения работы в реальном масштабе времени и является усовершенствованием таймера по авт.св. ¹ 1531081.

Целью изобретения является повышение достоверности функционирования таймера.

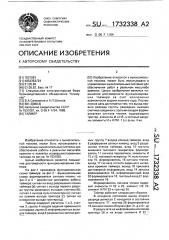

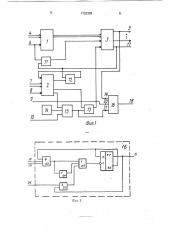

На фиг.1 приведена функциональная схема таймера; на фиг,2 — функциональная схема формирователя сигнала чтения; на фиг.3 и 4 — временные диаграммы работы таймера: сигнал на вход разрешения чтения таймера (а); сигнал с выхода первого разряда группы разрядных выходов счетчика (б); сигнал с выхода мультиплексора (в); сигнал на прямом выходе триггера (г); сигнал на инверсном выходе триггера (д).

Таймер содержит регистры 1 и 2, счетчик 3, группу 4 входов задания временного интервала, группу 5 информационных выходов таймера, вход 6 разрешения записи дан„.,!Ж„„1732338 А2 (57) Изобретение относится к вычислительной технике, может быть использовано в управляющих вычислительных системах для обеспечения работ в реальном масштабе времени. Целью изобретения является IlQвышение достоверности функционирования таймера за счет исключения возможности выдачи ложного кода. Поставленная цель достигается тем, что выход первого разряда группы разрядных выходов счетчика соединен с третьим входом формирователя сигнала чтения, содержащего триггер, элементы И и НЕ, в который введены элементы И и ИЛИ. 1 з.п.ф-лы, 4 ил. ных, группу 7 входов команд таймера, вход

8 разрешения записи команд, вход 9 разрешения чтения таймера, вход 10 частоты внешнего тактового генератора, формирователь 11 сигнала перезаписи, элементы И

12 и 13, тактовый генератор 14, мультиплексор 15, формирователь 16 сигнала чтения, выход 17 сигнала отсчета заданного интервала времени таймера, выход 18 признака достоверной информации, вход 19 запуска формирователя 16, информационный вход

20 формирователя 16, тактовый вход 21 формирователя 16, Формирователь сигнала чтения содержит элементы И 22 и 23, элемент HF 24, элемент ИЛИ 25 и триггер 26.

Таймер работает следующим образом.

В исходном состоянии выход второго разряда регистра 2 находится в состоянии логического "0", триггер 26 формирователя

16 сигнала чтения обнулен (фиг.Зг, д и 4 г, д).

В результате на информационном входе триггера 26 и на входе элемента И 22—

1732338

55 логическая "1", на входе элемента И 23— логический "0", что препятствует прохождению тактовых импульсов на синхровход триггера 26, а элемент И 23 подготовлен к приему сигналов, В регистр 1 и счетчик 3 импульсом с входа 6 записывается цифровое значение временного интервала. В регистр 2 импульсом с входа 8 записывается код требуемого режима счета таймера.

Для организации режима многократного запуска таймера в регистр 2 записывается код, устанавливающий логический "0" на выходе третьего разряда и логическую "1" на выходе второго разряда регистра 2. Логическая "1" на выходе второго разряда регистра 2 разрешает передачу через элемент

И 13 импульсов тактового генератора 14 или с выхода 10 внешнего тактового сигнала через мультиплексор 15 на счетный вход счетчика 3.

После отсчета заданного интервала времени на выходе переполнения счетчика

3 появляется импульс, который подается на выход 17 сигнала отсчета заданного интервала времени и через формирователь 11 сигнала перезаписи восстанавливает в счетчике 3 цифровое значение временного интервала, хранящееся в регистре 1, после чего счет интервала повторяется.

Если в регистр 2 записать импульсом с входа 8 код, устанавливающий логический

"0" на выходе второго разряда регистра 2, то закрывается элемент И 13 и прекращается поступление импульсов на счетный вход счетчика 3, Для организации режима однократного запуска таймера в регистр 2 импульсом с входа 8 записывается код, устанавливающий логическую "1" на выходах его второго и третьего разрядов. В этом случае после отсчета заданного интервала времени сигналом с выхода переполнения счетчика 3, поступающим через элемент И 12 на вход сброса в "0" второго разряда регистра 2, устанавливается логический "0" на выходе второго разряда регистра 2 и повторный запуск таймера не производится.

При появлении во время счета импульсов счетчиком 3 сигнала на входе 9 чтения таймера (фиг,За и 4а) с выхода формирователя 16 сигнала чтения таймера поступает импульс, обеспечивающий считывание достоверной информации.

Логическая "1" с входа 9 чтения таймера подается на вход элемента И 22, на его второй вход поступает в зависимости от предыдущего состояния счетчика 3 пере5

45 дний (фиг,За) или задний (фиг,4а) фронт импульса с выхода первого разряда счетчика 3, По переднему фронту импульса триггер

26 взводится (фиг,3r) по цепи элемент И 22 — элемент ИЛИ 25 — синхровход триггера 26.

По заднему фронту импульса триггер 26 взводится (фиг.4г) по цепи элемент И 22— элемент НЕ 24 — элемент ИЛИ 25 — синхровход триггера 26. Сигнал логического "0" с инверсного выхода взведенного триггера 26 (фиг.Зд и 4д) закрывает элемент И 22, что препятствует прохождению импульсов с выхода первого разряда счетчика 3, а логическая "1" с прямого выхода триггера 26 (фиг,Зг и 4г) открывает логический элемент

И 23. Ближайший тактовый импульс с выхода мультиплексора 15 (фиг,Зв и 4а) своим передним фронтом по цепи: элемент И 23— элемент ИЛИ 25 — синхровход триггера 26, устанавливает триггер 26 в исходное состояние (фиг.Зг и 4г).

Таким образом, формирователь 16 сигнала чтения устанавливается в исходное состояние, а на его выходе сформирован сигнал разрешения чтения от момента времени t1 (фиг.Зг и 4г), когда в счетчике 3 переходной процесс закончился, до момента времени t2 (фиг.Зг и 4г), когда по приходу тактового импульса он еще не начался, а это значит, что чтение информации из счетчика

3 в момент времени t< — tz происходит без искажения информации, Формула изобретения

1. Таймер по авт.св. N 1531081, о т л ич а ю шийся тем, что, с целью повышения достоверности функционирования, первый разрядный выход счетчика соединен с входом запуска формирователя сигнала чтения.

2. Таймер по п,1, отличающийся тем, что формирователь сигнала чтения содержит триггер, два элемента И, элемент Н Е и элемент ИЛИ, причем выход первого элемента И соединен с первым входом элемента ИЛИ и через элемент НŠ— с вторым входом элемента ИЛИ, третий вход которого соединен с выходом второго элемента И, первый и второй входы которого соединены соответственно с тактовым входом формирователя и прямым выходом триггера, инверсный выход которого соединен. с информационным входом триггера и первым входом первого элемента И, второй и третий входы которого являются соответственно входом запуска и информационным входом формирователя, выход элемента

ИЛИ соединен с синхровходом триггера, прямой выход которого является выходом формирователя.

1732338

Фиг. 2

1732338 Рог, М

Составитель И,Сафронова

Редактор И.Дербак Техред M.Ìîðãåíòàë Корректор М.Максимишинец

Заказ 1583 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101