Генератор тестов

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники. Цель изобретения - повышение полноты генерируемого теста. Генератор содержит узел 1 синхронизации, формирователь 2 потока адресов, узэл 3 памяти , узел 4 периодической коррекции ячеек , вход 5 запуска, выходы 6. Множество генерируемых тестовых воздействий больше множества ячеек узла 3. Гарантируется корректность теста. Тестовые воздействия генерируются с частотой работы узла 3. 2 з.п.ф-лы, 6 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК si s G 06 F 11/26

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (54) ГЕНЕPATOP ТЕСТА (21) 4887407/24 (22) 30.11.90 (46) 07.05.92. Бюл. ¹ 17 (75) Н.Д.Стукач (53) 681.3 (088.8) (56) Авторское свидетельство СССР

¹ 1226472, кл. G 06 F 11/26, 1986.

Авторское свидетельство СССР

¹ 1221654, кл. G 06 F 11/16, 1986, ) 0 1732347 А1 (57) Изобретение относится к области вычислительной техники. Цель изобретения— повышение полноты генерируемого теста.

Генератор содержит узел 1 синхронизации, формирователь 2 потока адресов, узел 3 памяти, узел 4 периодической коррекции ячеек, вход 5 запуска, выходы 6, Множество генерируемых тестовых воздействий больше множества ячеек узла 3, Гарантируется корректность теста. Тестовые воздействия генерируются с частотой работы узла 3. 2 з.п.ф-лы, 6 ил, 1

;(гд

Ю (л)

1732347

Изобретение относится к области вычислительной техники и может использоваться в быстродействующих тестерах, предназначенных для проверки цифровых узлов типа плат и микросхем.

Цель изобретения — повышение полноты генерируемого теста за счет увеличения множества генерируемых тестовых воздействий и цепочек тестовых воздействий.

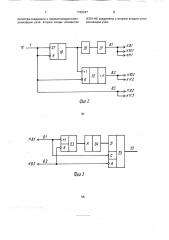

На фиг. 1 приведена структурная схема генератора; на фиг, 2 — функциональная схема узла синхронизации; на фиг. 3 — функциональная схема формирователя потока адресов; на фиг. 4 — функциональная схема узла памяти; на фиг. 5 — функциональная схема узла периодической коррекции ячеек; на фиг. 6 — функциональная схема генератора N импульсов.

Генератор теста (фиг. 1) содержит узел

1 синхронизации, формирователь 2 потока адресов, узел 3 памяти и узел 4 периодической коррекции ячеек и имеет вход 5 запуска и выходы 6. Вход 5 соединен с входом 7 запуска узла 1. Выходы 8 узла 1 соединены с входами 9 — 11 синхронизации соответственно формирователя 2, узла 3 и узла 4.

Выходы 6 соединены с выходами 12 узла 3.

Выходы 13 формирователя 2 соединены с входами 14 адреса чтения узла 3. Входы 15 адреса записи и информационные входы 16 узла 3 соединены соответственно с первыми 17 и вторыми 18 выходами узла 4.

Узел 1 синхронизации (фиг, 2) содержит генератор 19 N импульсов, элемент 20 задержки, одновибратор 21, счетчик 22.

Формирователь 2 потока адресов (фиг. 3) содержит счетчик 23, блок 24 памяти и регистр 25.

Узел 3 памяти содержит (фиг, 4) первый

26 и второй 27 мультиплексоры, первый 28 и второй 29 блоки памяти, первый 30 и второй 31 элементы ИЛИ-НЕ, элемент НЕ 32 и регистр 33.

Узел 4 периодической коррекции ячеек (фиг. 5) содержит генератор 34 псевдослучайных чисел, блок 35 памяти и регистр 36.

Генератор 19 N импульсов содержит (фиг. 6) генератор 37 синхросерии, счетчик

38, элемент 39 И, триггер 40 и элемент И 41, Генератор теста работает следующим образом.

После запуска генератора теста через вход 5 формирователь 2 генерирует конечный поток адресов. По каждому адресу, генерируемому формирователем 2, из узла 3 происходит чтение тестового воздействия на выходы 6.

Каждому адресу Ь узла 3 ставят в соответствие определенное множество Tb допустимых (с точки зрения корректности

10

20

25 чании запускающего импульса запуска30 ется генератор 19, который выдает N

55

50 генерируемого теста) тестовых воздействий. После запуска генератора теста узел 4 время от времени записывает в ячейку с адресом b узла 3 новое значение, в качестве которого использует произвольно выбранное тестовое воздействие множества Tb.

Перед первым запуском генератора тестов содержимое ячеек узла 3 не определено. Поэтому первую генерацию теста не используют. По окончании первой (как и любой последующей) генерации в ячейке с адресом Ь узла 3 (для каждого Ь) будет находиться одно из тестовых воздействий множества Tb.

При многократном чтении ячейки с адресом b узла 3, выполняемом по ходу любой генерации теста, начиная с второй, на выход

7 будут считываться разные тестовые воздействия множества Tb. При этом множество генерируемых тестовых воздействий будет больше, чем множество ячеек узла 3, Рассмотрим работу узлов генератора теста.

Узел 1 синхронизации (фиг. 2 работает следующим образом. Запускающий импульс, поступающий на вход 7 через вход 5, представляет собой кратковременный "0".

Этот "0" сбрасывает генератор 19 и счетчик

22 и транслируется на выход 8.3. По оконсинхроимпульсов, где К вЂ” число тестовых воздействий в генерируемом тесте. Каждый синхроимпульс переключает счетчик 22 и через элемент 20 (обеспечивающий задержку на время окон.ания переходных процессов, которые вызываются в генераторе теста переключением счетчика 22) запускает одновибратор 21, формирующий строб на выходе 8.1. Счетчик 22 выдает "1" на выход 8.2 в каждом и-м такте (о значении п см. ниже).

Формирователь 2 потока адресов (фиг. 3) работает следующим образом, "0", поступающий на вход 9,2, сбрасывает счетчик 23 и регистр 25, По окончании каждого поступающего на вход 9.1 строба переключается счетчик 23, работающий с коэффициентом пересчета m, равным числу ячеек блока 24, Счетчик 23 задает адрес блоку 24, Считываемое из блока 24 слово заносится в регистр

25, с выходом которого поступает на выходы

13, В последовательные ячейки блока 24 в ходе его программирования должны быть занесены соответствующие адреса, составляющие формируемый поток адресов. Чтобы адреса многократно встречались в этом потоке, они должны быть записаны во многие ячейки блока 24. Кроме того, если сделать N много больше m, то по ходу генерации теста поток адресов, генерируемый формирователем 2, будет циклически повторяться.

1732347

Узел 3 памяти (фиг. 4) работает следующим сбразом, В зависимости от состояния

Х старшего разряда (поступающего через вход 14.2) адреса чтения выполняется чтение в регистр 33 (no адресу, поступающему через входы 14.1) из блока 28 (при X = 1) или блока 29 (при Х = О). Если чтение выполняется из блока 28, то блок 29 доступен для записи (по адресу, поступающему через входы 15) тестового воздействия, поступающего через входы 16. В противном случае роли блоков 28 и 29 меняются местами.

Узел 4 периодической коррекции ячеек (фиг. 5) работает следующим образом, "0", поступающий на вход 11,3, сбрасывает генератор 34 и регистр 36. По окончании строба, поступающего на вход 11.1, переключаются генератор 34 и регистр 36, но только в этом случае, если на вход 11.2 поступает "1". Последняя приходит в каждом п-м такте, где и — число тактов, в течение которых происходит операция чтения из блока 35. Генератор 34 вырабатывает псевдослучайный адрес для блока 35. Читаемое из блока 35 слово заносится в регистр ЗЬ, причем оно содержит поле "Адрес", поступающее на выходы 17, и поле "Тестовое воздействие", поступающее на выходы 18.

Поле "Адрес" содержит какой-то адрес Ь узла 3, а поле "Тестовое воздействие" — одно из тестовых воздействий множества Tb

Генератор 19 N импульсов (фиг. 6) работает следующим образом. Генератор 37 генерирует непрерывную синхросерию, Если триггер 40 находится в состоянии "1", то она через элемент 41 проходит на выход генератора 19, а также вызывает переключения счетчика 38, Триггер 40 устанавливается в

"0" через элемент 39 подачей "0" через вход

R генератора 19, или же сигналом с выхода переноса счетчика 38. Счетчик 38 и триггер

40 по концу синхроимпульса, вырабатываемого генератором 37, сбрасываются в "0", если на вход" С " генератора 19 подана "1".

Формула изобретения

1. Генератор теста, содержащий формирователь потока адресов и узел памяти, причем выходы узла памяти являются выходами генератора, входы адреса чтения узла памяти соединены с выходами формирователя потока адресов, отличающийся тем, что, с целью повышения полноты генерируемого теста, в него введены узел периодической коррекции ячеек и узел синхронизации, причем входы адреса записи узла памяти соединены с первыми выходами узла периодической коррекции ячеек, информационные входы узла памяти соединены с вторыми выходами узла периодиче5

55 ской коррекции ячеек, вход запуска у=лг синхронизации соединен с входом запуска генератора, первый выход узла синхронизации соединен с первыми входами синхронизации формирователя потока адресов, узла памяти и узла периодической коррекции ячеек, второй выход узла синхронизации соединен с вторыми входами синхронизации узла памяти и узла периодической коррекции ячеек, третий выход блока синхронизации соединен с третьими входами синхронизации формирователя потока адресов и узла периодической коррекции ячеек.

2. Генератор по и. 1, о т л и ч а ю щ и йс я тем, что узел периодической коррекции ячеек содержит генератор псевдослучайных чисел, блок памяти и регистр, причем выходы генератора псевдослучайных чисел соединены с адресными входами блока памяти, выходы которого соединены с информационными входами регистра, первые и вторые выходы которого соединены соответственно с первыми и вторыми выходами узла, входы синхронизации генератора псевдослучайных чисел и регистра соединены с первым входом синхронизации узла, входы разрешения переключения генератора псевдослучайных чисел и регистра соединены с вторым входом синхронизации узла, входы сброса генератора псевдослучайных чисел и регистра соединены с третьим входом синхронизации узла, 3, Генератор по пп, 1 и 2, о т л и ч а юшийся тем, что узел памяти содержит два мультиплексора, два блока памяти, два элемента ИЛИ-НЕ, элемент HE и регистр, причем первые информационные входы мультиплексоров соединены с входами адреса записи узла, вторые информационные входы мультиплексоров сединены с входами адреса чтения узла, исключая последний вход адреса чтения узла, соединенный с адресным входом первого мультиплексора, входом разрешения чтения первого блока памяти, первым входом первого элемента

ИЛ И-Н Е и входом элемента Н Е; выход которого соединен с адресным входом второго мультиплексора, входом разрешения чтения второго блока памяти и первым входом второго элемента ИЛИ-НЕ, выходы блоков памяти соединены с информационными входами регистра, выходы которого являются выходами узла, адресные входы первого блока памяти соединены с выходами первого мультиплексора, адресные входы второго блока памяти соединены с выходами второго мультиплексора, информационные входы блоков памяти соединены с информационными входами узла, входы разрешения выборки блоков памяти и вход синхронизации

1732347

55 регистра соединены с первым входом синхронизации узла, вторые входы элементов

ИЛИ-НЕ соединены с вторым входом синхронизации узла.

Х102 ./(113

/ГЫ

/(1/5

1732347 к 8Л к 82

1732347

45

Составитель А.Сиротская

Техред М.Моргентал Корректор С. Шевкун

Редактор Е,Папп

Заказ 1584 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101