Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих аналогоцифровых преобразователей. Цель изобретения - повышение динамической точности достигается введением в устройство инверторов 14 и 15 тока и элемента 16 связи на конденсаторе, а также новым построением дифференциальных усилителей 10, 11. Устройство также содержит коммутатор 1, входную 13 и выходную б шины, шину 2 управления, повторитель 3 напряжения, накопительный элемент 4 на конденсаторе, входной резистор 12 и резистор 7 обратной связи, форсирующий конденсатор 9, генератор 8 тока, шину 5 нулевого потенциала. Указанная совокупность признаков позволяет повысить перезаряд элемента 4, ограничивая его лишь предельными значениями параметров транзисторов в импульсном режиме . 3 з. п. ф-лы, 1 ил. Ё 1 00 hO GO 00 ю ю

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)з 6 11 С 27/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1325567 (21) 4775563/24 (22) 29.12.89 (46) 07.05.92. Бюл. М 17 (71) Научно-исследовательский электромеханический институт (72) 10.В. Тимкин, М,П. Минаева, Л,Ю. Равер, А.А. Солодимов и l0.8. Полубабкин (53) 681.327.66 (088.8) (56) Авторское свидетельство СССР

М 1325567, кл. G 11 С 27/00, 1986, (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих аналогоцифровых преобразователей. Цель изабре„„5U„„1?32382 А2 теНия — повышение динамической точности достигается введением в устройство инверторов 14 и 15 тока и элемента 16 связи на конденсаторе, а также новым построением дифференциальных усилителей 10, 11. Устройство также содержит коммутатср 1, входную 13 и выходную 6 шины, шину 2 управления, повторитель 3 напряжения, накопительный элемент 4 на конденсаторе, входной резистор 12 и резистор 7 обратной связи, форсирующий конденсатор 9, генератор 8 тока, шину 5 нулевого потенциала.

Указанная совокупность признаков позволяет повысить перезаряд элемента 4, ограничивая его лишь предельными значениями параметров транзисторов в импульсном режиме. 3 з, и. ф-лы, 1 ил.

1732382

10

40

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, может быть использовано при построении аналого-цифровых преобразователей и является усовершенствованием изобретения по авт. св. hb 1325567.

Известно устройство, содержащее коммутатор, управляющий вход которого соединен с шиной управления, первый и второй информационные входы — с выходами соответственно первого и второго дифференциальных усилителей, неинвертирующие входы которых соединены с шиной нулевого потенциала, инвертирующие — через форсирующий конденсатор с входом генератора тока и непосредственно с точкой соединения входного резистора и резистора обратной связи, второй вывод которого, соединен с выходной шиной устройства, выходом генератора тока и выходом повторителя напряжения, вход которого соединен с выходом коммутатора и через накопительный элемент на конденсаторе с шиной нулевого потенциала, второй вывод входного резистора соединен с входной виной устройства.

Недостаток известного устройства заключается в принципиально существующем ограничении тока заряда накопительного конденсатора, что ограничивает динамическую точность устройства, Ток заряда накопительного элемента на конденсаторе определяется величиной тока через транзисторы дифференциального усилителя, который не зависит от режима работы устройства (выборка — хранение) и по этой причине принципиально ограничен допустимой мощностью, рассеиваемой на транзисторах дифференциального усилителя.

Цель изобретения — повышение динамической точности;

В устройство введены элемент связи на конденсаторе, первый и второй выводы которого соединены с вторыми выходами— точками соединения эмиттеров транзисторов соответственно первого и второго дифференциальных усилителей, и первый и второй инверторы тока (токовые зеркала), входы которых соединены с третьими выходами соответственно первого и второго дифференциальных усилителей, выходы — с первыми выходами соответственно первого и второго дифференциальных усилителей.

Кроме того, второй выход дифференциального усилителя соединен с эмиттерами первого и второго транзисторов, коллектор первого транзистора — с третьим выходом дифференциального усилителя.

Таким образом, обеспечивается возможность заряда накопительного элемента на конденсаторе током, величина которого ограничена лишь импульсными возможностями по току транзисторов устройства, Резистивная нагрузка дифференциального усилителя оказывается подключенной параллельно транзистору инвертора тока, что способствует сохранению частотных свойств устройства в режиме статического слежения.

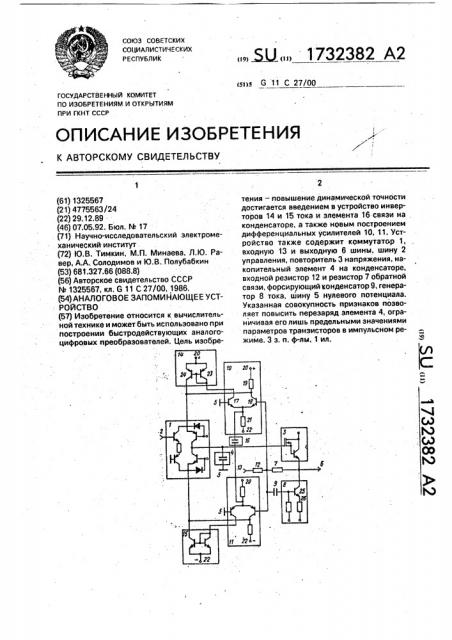

На чертеже приведена электрическая функциональная схема устройства, Аналоговое запоминающее устройство содержит коммутатор 1, управляющий вход которого соединен с шиной 2 управления, выход- с входом повторителя 3 напряжения и накопительным элементом 4 на конденсаторе, другой вывод которого соединен с шиной 5 нулевого потенциала устройства, выход повторителя 3 напряжения соединен с выходкой шиной 6, первым выводом резистора 7 обратной связи и выходом генератора 8 тока, вход которого через форсирующий конденсатор 9 соединен с вторым выводом резистора 7 обратной связи, инвертирующими входами первого 10 и второго 11 дифференциальных усилителей, неинвертирующие входы которых подключены к шине 5 нулевого потенциала, и с первым выводом входного резистора 12, второй вывод которого соединен с входной шиной 13. Первые выходы первого 10 и второго 11 дифференциальных усилителей соединены соответственно с первым и вторым входами коммутатора 1 и с выходами соответственно первого 14 и второго 15 инверторов тока, второй выход первого дифференциального усилителя 10 через элемент 16 связи на конденсаторе соединен с вторым выходом второго дифференциального усилителя 11, третий выход которого соединен с входом второго инвертора 15 тока, вход первого инвертора 14 тока соединен с третьим выходом первого дифференциального усилителя 10.

Каждый из дифференциальных усилителей 10 и 11 содержит первый 17 и второй 18 транзисторы, базы которых соединены соответственно с неинвертирующим и инверти рующим входами дифферен циального усилителя, первый выход которого через первый резистор 19 соединен с первой шиной 20 питания устройства и непосредственно с коллектором второго транзистора

18, эмиттер которого соединен через второй резистор 21 с второй шиной 22 питания устройства и непосредственно с вторым выходом дифференциального усилителя и эмиттером первого транзистора 17, коллектор которого соединен с третьим выходом дифференциального усилителя. Каждый ин1732382 изменяется и компенсирует прямое прохождение входного сигнала на шину 6 (через резисторы 12 и 7 и паразитные емкостные связи), Токи транзисторов 17 и

18 усилителя 10 (аналогично и усилителя 11) приблизительно равны между собой, а их величина определяется величиной резистора 21 и источника 22. Указанные токи через инвертор 14 замыкаются на источник 20.

При этом втекающий в первый информационный вход коммутатора 1 ток определяется величинами резистора 19 и источника 20.

При подаче на шину 2 низкого потенциала элемент 4 оказывается подключенным к первому и второму информационным входам коммутатора 1, При этом начинается перезаряд элемента 4, происходящий до тех пор, пока напряжения на шинах 6 и 13 не удовлетворят соотношению, сп раведли вому для операционных усилителей:

Овых = ЙосЮвх Bx где Овь х и U x — напряжение соответственно на шинах 6 и 13; асс и R x — величины сопротивлений резисторов соответственно 7 и 12, Однако до выполнения указанного соотношения в суммирующей точке, образованной точкой соединения резисторов 12 и

7, появляется напряжение рассогласования, поступающее на инвертирующие входы усилителей 10 и 11. Если полярность

45 вертор 1 4 и 15 тока содержит первый 23 и второй 24 транзисторы одного типа проводимости, эмиттеры которых соединены с соответствующей шиной (20 или 22) питания устройства, базы — с коллектором первого 5 транзистора 23 и входом инвертора тока, выход которого соединен с коллектором второго транзистора 24. Для обеспечения симметричности и линейности характеристик устройства дифференциальные усили- 10 тели 10 и 11 и инверторы 14 и 15 тока выполнены по комплементарной структуре.

Генератор 8 тока содержит транзистор 25 с большим коэффициентом усиления и токо- задающий резистор 26, 15

Аналоговое запоминающее устройство работает следующим образом, В исходном состоянии на шину 2 поступает высокий потенциал, обеспечивающий отключение элемента 4 коммутатором 1 от 20 его информационных входов (устройство находится в режиме хранения), при этом токи, поступающие на инфррмационные входы коммутатора 1, замыкаются между собой. Напряжение с элемента 4 через по- 25 вторитель 3 поступает на шину 6. Изменения напряжения на шине 13 через резистор

12 и конденсатор 9 поступают на базу транзистора 25 генератора 8, ток которого этого напряжения положительная, то увеличивается ток через второй транзистор 18 усилителя 10, что приводит к уменьшению токов через транзистор 17 усилителя 10 и через транзисторы инвертора 14. Это приводит к соответствующему уменьшению втекающего в первый информационный вход коммутатора 1 тока, Одновременно уменьщается ток, протекающий через второй транзистор усилителя 11, но увеличивается ток, протекающий через первый транзистор усилителя 11 и транзисторы инвертора 15, что приводит к увеличению вытекающего из второго информационного входа коммутатора 1 тока.

Разность токов первого и второго информационного входов коммутатора 1 перезаряжает элемент 4 до тех пор, пока выходное напряжение устройства не соответствует указанному соотношению. Элемент 16 исключает ограничение токов инверторов 14 и 15 и усйлителей 10 и 11 в динамическом режиме. При подаче на шину

2 высокого потенциала аналоговое запоминающее устройство вновь переходит из режима слежения в режим хранения.

Проведенное математическое моделирование показало, что по сравнению с известным устройством возможно уменьшение времени слежения (времени выборки) в сотни раз, а быстродействие устройства ограничивается лишь предельными значениями токов через транзисторы в импульсном режиме и быстродействием самих транзисторов, При подаче на шину 13 устройства сиг.налов с несанкционированной скоростью нарастания в реальном устройстве (при низкоомных источниках питания) возможен выход из строя транзисторов устройства, Для исключения этого явления ток перезаряда элемента 4 должен быть ограничен известными техническими приемами. например введением резистора в цепь элемента 4 или в цепь элемента 16, формула изобретения

1. Аналоговое запоминающее устройство по авт. св, N 1325567, о т л и ч а ю щ е ес я тем, что, с целью повышения динамической точности, в него введены первый и второй инверторы тока и элемент связи на конденсаторе, первый и второй выводы которого подключены соответственно к вторым выходам соответственно первого и второго дифференциальных усилителей, третьи выходы которых подключены к вхо- дам соответственно первого и второго инверторов тока, выходы которых подключены к первым выходам соответственно первого и второго дифференциальных усилителей, 1732382

Составитель Ю.Тимкин

Техред М.Моргентал Корректор T.Màëåö

Редактор И.Шулла

Заказ 1585 . Тираж: Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

2. Устройство по и, 1, о т л и ч а ю щ е ес я тем, что каждый инвертор тока содержит первый и второй транзисторы одного типа проводимости, эмиттеры которых обьединены и подключены к соответствующей шине питания, базы обьединены и подключены к коллектору первого транзистора и к входу инвертора тока, выход которого подключен к коллектору второго транзистора соответствующего тока.

3. Устройство по и. 1, о т л и ч а ю щ e eс я тем, что первый и второй инверторы тока выполнены по комплементарной структуре.

4. Устройствопоп,1, отличающеес я тем, что коллектор первого транзистора дифференциального усилителя является выходом дифференциального усилите10 ля.