Устройство цифровой фазовой автоподстройки частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к технике электросвязи и может быть использовано в устройствах когерентной обработки фазоманипулированных сигналов с углом фазовой манипуляции 180° в частности в аппаратуре каналов передачи дискретной информации. Цель изобретения - увеличение допустимого времени пропадания входного фазоманипулированного сигнала и повышение быстродействия. Устройство содержит усилитель-ограничитель 1. два D- триггера 2 и 3, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, накопитель 5. управляемый делитель 6 частоты, опорный генератор 7. формирователь 8 импульсов и делитель 9 частоты на два. Цель обеспечивается введением элемента 10 задержки и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11, а также выполнением накопителя с выходом запрета, что позволяет исключить из подсчета ошибочные импульсы. 3 з. п. ф-лы, 1 ил.

СОЮЗ COBF.tñêÈÕ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5!)5 Н 031 7/00

ГОСУДАРСТВЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4805135/09 (22) 21.03.90 (46) 07.05.92. Бюл. N 17 (71) Новосибирский электротехнический институт связи им. Н. Д. Псурцева (72) А, M . Ш т а н ю к, С, Н . А р х и п о в и В. И. Сединин (53) 621.396.662(088,8) (56) Авторское свидетельство СССР

Гл 1626382, кл. Н 03 L 7/00, 1982, (54) УСТРОЙСТВО ЦИФРОВОЙ ФАЗОВОЙ

АВТОПОДСТРОЙКИ ЧАСТОТЫ (57) Изобретение относится к технике электросвязи и может быть использовано в устройствах когерентной обработки фазоманипулированных сигналов с углом фазовой манипуляции 180 . в частности в

„„5U „„1732466 А1 аппаратуре каналов передачи дискретной информации. Цель изобретения — увеличение допустимого времени пропадания входного фазоманипулированного сигнала и повышение быстродействия. Устройство содержит усилитель-ограничитель 1. два Отриггера 2 и 3, первый элемент

ИСКЛЮЧАЮЩЕЕ.ИЛИ 4, накопитель 5, управляемый делитель 6 частоты, опорный генератор 7, формирователь 8 импульсов и делитель 9 частоты на два. Цель обеспечивается введением элемента 10 задержки и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

11, а также выполнением накопителя с выходом запрета. что позволяет исключить из подсчета ошибочные импульсы. 3 з. и. ф-лы, 1 ил.

1732466

Изобретение относится к технике связи и может быть использовано в устройстве когерентной обработки фазоманипулированнь|х сигналов с углом фазовой манипуля180о

Цель изобретения — увеличение допустимого времени пропадания входного фазоманипулированного сигнала, достижение независимости скорости подстройки фазы выходного колебания от знака расстройки и получение симметрии полосы удержания.

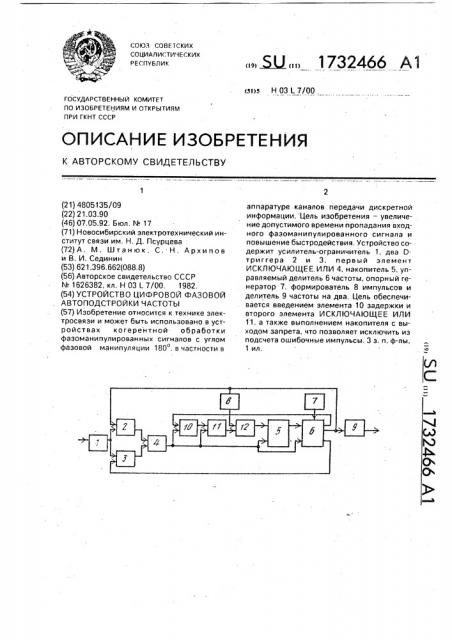

На чертеже представлена структурная электрическая схема предлагаемого устройства цифровой фазовой автоподстройки частоты.

Устройство содержит усилитель-ограничитель 1, первый 2 и второй 3 О-триггера, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, реверсивный счетчик(накопитель) 5, делитель

6 частоты, опорный генератор 7, формирователь 8 импульсов, делитель 9 частоты на два, элемент 10 на О-триггер, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11 и ключ 12, Устройство работает следующим образом, На вход устройства поступает, аналоговый фазоманипулированный сигнал. Усилитель-ограничитель преобразует его в бинарный, D-триггеры 2 и 3 стробируют сигнал, поступающий с выхода усилителя-ограничителя 1, и запоминают результат до следующего стробирования, Моменты стробирования задаются передними фронта двух противофазных колебаний, поступающих на тактовые входы соответствующих

D-триггеров 2 и 3. Они определяют границы опережения-запаздывания и запаздывания-опережения между областями и, соответственно, сами эти области.

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4 сравнивает напряжения на выходах О-триггеров

2 и 3. Совпадение напряжений указывает, что а области, для которой момент последнего стробмрования является задней границей, переход через ноль отсутствует, несовпадение говорит о наличии перехода.

8 первом случае с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 выдается низкий уровень напряжения. во втором случае— высокий. Этим сигналом задается направление счета реверсивного счетчика 5.

На счетный вход реверсивного счетчика

5 подаются импульсы от формирователя 8, Эти импульсы должны поступать на счетный вход после установления соответствующего напряжения на входе управления "Направления счета" реверсивного счетчика. Частота следования импульсов должна соответствовать частоте следования переходов через ноль (частоте появления фрон10

25

30 на наличие или отсутствие переходов через нуль. Если переходы через нуль обнаруже35 ны или, наоборот, необнаружены в двух

40 ржит ключ 12 в закрытом состоянии.

Реверсивный счетчик 5 ведет насчет поступающих импульсов. При переполнений

55 тов и срезов) выходного колебания. Для выполнения этих условий работа формирователя 8 импульсов синхронизирована с колебанием. задающим моменты стробирования для одного из D-триггеров 2 или 3.

В рассматриваемой схеме блокировка работы реверсивного счетчика для предотвращения воздействия ложных импульсов осуществляется путем прерывания подачи импульсов от формирователя 8. Для этого в цепи между выходом формирователя 8 и счетным входом реверсивного счетчика 5 установлен ключ 12..Сигнал управления для . ключа 12 вь;рабатывает второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11. На один вход этого элемента подается напряжение с выхода первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 непосредственно, а на второй вход поступает этот же сигнал, но задержанный. Задержка выполняется с помощью D-триггера 10.

Величина задержки определяется частотой колебания, снимаемого с промежуточного выхода управляемого делителя 6 частоты и подаваемого на тактовый вход D-триггера

10. Величина задержки определяется частотой колебания, снимаемого с промежуточного выхода управляемого делителя 6 частоты и подаваемого на тактовый вход

О-триггера 10. Схема, образованная элементом задержки на О-триггере 10 и вторым элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 11, выполняет сравнение двух смежных областей смежных областях, то элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11 выдает сигнал низкого уровня, который ао время появления очередного импульса на выходе формирователя 8 дена его выходе появляется короткий импульс и счетчик возвращается в исходное состояние.

Импульсы переполнения реверсивного счетчика 5 поступают на первый вход управления управляемого делителя 6 частоты и служат сигналами на изменение коэффициента деления, Установление пониженного или повышенного коэффициента деления согласовано с тем, при каком режиме работы (сложении или вычитании) произошло переполнение реверсивного счетчика 5. Такое согласование обеспечивается за счет того. что второй вход управляемого делителя 6 частоты подключен параллельно входу управления реверсивного счетчика 5 и на них подается один и тот же сигнал с выхода первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4.

1732466

30

50

Изменение коэффициента деления управляемого делителя 6 частоты происходит за один цикл деления. После этого делитель возвращается к работе с номинальным коэффициентом деления, но фаза выходного колебания сдвигается на один шаг подстройки.

Управляемый делитель 6 частоты имеет два противофазных выхода и дополнительный промежуточный вход. Период колебания на промежуточном выходе определяет задержку, вносимую элементом задержки на 0-триггере 10, Промежуточным выходом может бь|ть выход любого промежуточного каскада управляемого делителя 6 частоты.

При номинальном коэффициенте деления частота колебаний на противофазных выходах управляемого делителя 6 частоты равна удвоенной номинальной частоте несущей фазоманипулированного сигнала.

Эти колебания используются для задания границ областей опережения и запаздывания. Рационально задавать размеры областей одинаковыми. Это обеспечивается, когда скважность колебаний на парафазных выходах равна двум.

При однократном изменении коэффициента деления согласно изменению фазы выходных колебаний изменяют на один шаг свое положение области опережения и запаздывания, Направление сдвига областей определяется положением переходов через нулевой уровень несущей входного фазоманипулированного сигнала относительно областей опережения и запаздывания, Направление сдвига сохраняется до тех пор, пока моменты перехода. несущей через нуль не переместятся в смежные области. например из области запаздывания в область опережения. После этого направление сдвига изменяется на противоположное. В результате такого механизма работы в схеме устанавливается режим фазирования, т. е. режим динамического равновесия, при котором моменты перехода через нуль оказываются совмещенными с границами между областями запаздывания и опережения.

Выходным блоком всего рассматриваемого устройства цифровой фазовой автоподстройки частоты является делитель 9 частоты на два. Он из выходного сигнала управляемого делителя 6 частоты формирует колебание с частотой фазоманипулированного сигнала, Ф ронты и срезы выходного колебания жестко связаны с границами между областями опережения и запаздывания. Соответственно, в установившемся режиме динамического равновесия выходное колебание оказывается сфазировэнным с несущей входного фазоманипулированного сигнала.

Формула изобретения

1, Устройство цифровой фазовой автоподстройки частоты, содержащее усилитель-ограничитель, вход которого является входом всего устройства, первый и второй

0-триггеры. информационные входы которых подключены к выходу усилителя-ограничителя, первый элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены с выходами первого и второго 0-триггеров, накопитель, опорный генератор, управляемый делитель частоты, счетный вход которого подключен к выходу опорного генератора, вход счета и вход управления добавлением-вычитанием импульсов соединены соответственно с выходом переполнейия накопителя и выходом первого элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, а прямой и инверсный выходы подключены к тактовым входам первого и второго 0-триггеров соответственно, а один из выходов соединен также с входом формирователя импульсов, делитель частоты на два, выход которого является выходом всего устройства, а вход подключен к одному из выходом управляемого делителя частоты, выходы формирователя импульсов и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к входу сигнала и входу управления знаком накопления накопителя, о т л и ч а ю щ е е с я тем, что, с целью увеличения допустимого времени пропадания входного фазоманипулированного сигнала и повышения быстродействия, в устройство введены элемент задержки, вход которого подключен к выходу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ., второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого подключены соответственно к входу и выходу элемента задержки, а накопитель снабжен входом запрета, который подключен к выходу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, 2. Устройство по и. 1, о т л и ч а ю щ е ес я тем, что накопитель выполнен в виде реверсивного. счетчика с входом запрета счета, а элемент задержки выполнен в виде элемента задержки с инверсией, при этом вход запрета счета является входом запрета накопителя счетный вход является входом сигнала накопителя, а вход управления направлением счета является входом управления знаком накопления накопителя.

3. Устройство по и. 1, отл ича ю ще ес я тем, что накопитель выполнен в виде последовательно соединенных ключа и реверсивного счетчика, при этом вход ключа является сигнальным входом накопителя, 1732466

Составитель С. Архипов

Техред M.Моргентал Корректор М. Максимишинец

Редактор С, Пекарь

Заказ 1589 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб.. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101 управляюгций вход ключа является входом запрета накопителя, а вход управления направлением счета реверсивного счетчика является входом управления знаком накопления накопителя.

4. Устройство по п. 1, о т л и ч а ю щ е ес я.тем, что элемент задержки выполнен на третьем D-триггере. управляемый делитель частоты выполнен с промежуточным выходом, который соединен с тактовым входом

О-триггера, информационный вход D-триг5 гера является входом элемента задержки,