Устройство для свертки по произвольному модулю

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении диагностируемых систем. Цель изобретения - сокращение аппаратурных затрат устройства. При подаче сигнала запуска на вход 13 устройства на регистр 2 через коммутатор 1 переписывается контролируемое число с информационного входа 21 устройства , а на регистр 3 - модуль контроля со входа 22 устройства. Блоки сравнения группы 4 сравнивают содержимое регистра 2 (выход 14) с содержимым регистра 3 (выход 15), умноженным на 2, где 1 j k (k - число блоков в группе 4). В блоках вычита

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (s1)s G 06 F 11/08

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4793422 /24 (22) 19;02.90 (46) 15.05.92. Бюл. N. 18 (71) Московский институт инженеров гражданской авиации (72) С.Ж.Кишенский, С,B,Êàìåícêèé, А,Л. Кузьмин и О.Ю.Христенко (53) 681.3(088.8) (56) Авторское свидетельство СССР

N 1401463, кл. G 06 F 11/08, 1986, Авторское свидетельство СССР

М 1509903, кл. G 06 F 11/08, 1987. (54) УСТРОЙСТВО ДЛЯ СВЕРТКИ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ (57) Изобретение относится к вычислительной технике и может быть использовано при построении диагностируемых систем. Цель изобретения — сокращение аппаратурных затрат устройства. При подаче сигнала запуска на вход 13 устройства на регистр 2 через коммутатор 1 переписывается контролируемое число с информационного входа 21 устройства, а на регистр 3- модуль контроля со входа 22 устройства, Блоки сравнения группы 4 сравнивают содержимое регистра 2 (выход 14) с содержимым регистра 3 (выход

15), умноженным на 2, где 1< j < k (k— число блоков в группе 4). В блоках вычита1734094

Изобретение относится к вычислитель- м ной технике и может быть использовано при т по„ | роении диагностируемых систем. ф

Цепь изобретения — сокращение аппа- Н ратурных затрат устройства. 5 э

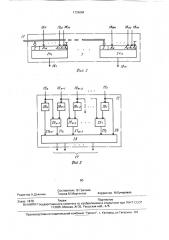

На фиг, 1 приведена функциональная схема устройства; на фиг, 2, 3 — примеры т реализации мультиплексора и дешифрато- к р|а, у

Устройство (фиг. 1) содержит коммута- 10 ч тор 1, регистры 2 и 3, группу блоков 4 срав- к нения, блок 5 сравнения, группу блоков 6 е вычитания, мультиплексор 7, группу эле- т ментов И 8, элемент НЕ 9, элемент И 10„ генератор 11 тактовых импульсов, дешиф- 15 ратор 12, вход 13 запуска устройства, выходь. :14, 15 первого и второго регистров 2 и 3 соответственно, выходы 16 блоков 4 сравнения группы, выход 17 дешифратора 12, выходы 18 блоков 6 вычитания группы, выход 20

"9 мультиплексора 7, информационный выход 20 устройства, информационный вход

21 устройства, вход 22 задания модуля контроля устройства, элемент ИЛИ 23, Мультиплексор 7 (фиг. 2) содержит ком- 25 мутаторы 24, Дешифратор 12 (фиг, 3) содержит группу элементов И 25, шифратор 26, входы 27 шифратора 26, группу 28 элементов НЕ.

Устройство работает следующим обра- 30 зом, В исходном состоянии регистры 2, 3 либо обнулены (цепи сброса не показаны), либо содержит данные от предыдущего вычисления остатка (на регистре 2 — двоичный код 35 остатка, на регистре 3 — двоичный код модуля), В первом случае с выхода "Меньше" блока 5 сравнения снимается нулевой сигнал и элементы И 8 группы закрыты, а единичный сигнал с выхода элемента НЕ 9 разрешает 40 тактовому сигналу с генератора 11 пройти через элемент И 10 и элемент ИЛИ 23 на вход записи регистра 2, что не оказывает влияния на работу устройства. Во втором случае с выхода блока 5 сравнения снимает- 45 ся единичный сигнал, открывающий эления группы 6 происходит вычисление разнос ги между содержимым регистра 2 и содержимь,м регистра 3, умноженным на 2 .

Выходь 18 блоков 6 вычитания поступают на входы мул ьтиплексора 7, который управляется выходом 17 дешифратора 12, пропускающим на выход 19 мультиплексора 7 наименьшую разность между содержимым регистров 2 и 3. Эта наименьшая разность через коммутатор 1 записывается снова в регистр, Процесс продолжается, пока содержимое регистра 2 не станет меньше содержимого регистра. В этом случае сигнал с выхода блока 5 сравнения разрешит прохождение кода с выхода 14 регистра 2 через элементы

И группы 8 на информационный выход 20 устройства. Организация цикла вычислений остатка обеспечивается элементом НЕ 9, элементом И 10, генератором 11 тактовых импульсов и элементом ИЛИ 23. 1 табл., 3 ил. енты И 8 группы и пропускающий резульат вычисления с выхода регистра 2 на инормационный выход 20 устройства. улевой сигнал с выхода элемента НЕ 9 в то время закрывает элемент И 10.

Работа устройства подготавливается усановкой на входе 21 устройства двоичного ода контролируемого числа, а на входе 22 стройства — кода модуля контроля. С подаей сигнала запуска на вход 13 устройства оммутатор 1 на короткое время, определямое длительностью импульса запуска, усанавливается в состояние, подключающее содержимое входа 21 устройства к выходу коммутатора 1, Одновременно формируется единичный сигнал на входах записи регистров 2 и 3 и на этих регистрах оказываются записанными контролируемое число и модуль контроля соответственно. Эти коды поступают на соответствующие информационные входы блоков 4 сравнения группы и блока 5 сравнения. На выходах "Меньше" этих блоков единичный сигнал формируется в случае, когда двоичное число на выходе 14 меньше соответствующим образом подключенного к блокудвоичного числа с выхода 15 (если принять контролируемое число за К, а модуль контроля — за М, то в блоке сравнения 4j группы производится сравнение чисел К и

Мх2 ", где 1 «) К, где Š— число блоков сравнения в группе 4), При разрядности контролируемого числа, равной и, разрядности модуля контроля, равной m, получается, что k = n - m, Сигналы с выходов блоков 4 сравнения поступают на дешифратор 12, имеющий следующую таблицу истинности для случая k = 5, Выход 17 дешифратора 12 поступает на управляющий вход мультиплексора 7.

На блоках 6 вычитания определяются двоичные значения разностей. Для j-ro блока 6 определяется разность

К - Mx2

Сигналы с выходов блоков 6 поступают на информационные входы 18 мультиплек1734094 сора 7. Код на управляющем входе мультиплексора 7 пропускает на его выход наименьшую разность при К > Mx2i либо нулевой сигнал при К < M. 50

По первому тактовому импульсу в регистр 2 через коммутатор 1 записывается первая минимальная разность. Далее процесс продолжается до тех пор, пока с выхода "Меньше" блока 5 сравнения не поступит 55 нулевой сигнал, говорящий, что число на регистре 2 меньше числа на регистре 3 (кода модуля контроля), При этом на выход 20 устройства передаетсь через элементы И группы 8 остаток по модулю. При этом нулевой сигнал с выхода элемента HE 9 запрещает прохождение сигналов генератора 11 через элемент И 10 на вход записи регистра

2 и работа устройства заканчивается.

Новый цикл работ . устройства начина- 5 ется подачей новых кодов на входы 21 и 22 устройства и сигнала запуска на вход 13 устройства.

Если при запуске устройства. сразу выполняется условие К< М, то содержимое ре- 10 гистра 2 с помощью блока 5 сравнения сразу же предается на выход 20 устройства.

Формула изобретения

Устройство для свертки по произвольному модулю, содержащее два регистра, группу элементов И, группу блоков сравнения, группу блоков вычитания и мультиплексор, причем выход первого регистра 20 соединен с входами уменьшаемого блоков вычитания группы, выходы результата которых соединены с соответствующими инфор мационными входами мультиплексора, информационный вход второго регистра яв- 25 ляется входом задания модуля контроля устройства, каждый i-й разряд выхода второго регистра соединен с (i+j-1)-м разрядом первого информационного входа )-го блока сравнения группы (1 < i < m, где m — разрядность модуля контроля, 1 j k, k = o-m, где и — разрядность контролируемого числа), о т л и ч а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, устройство содержит дешифратор, коммутатор, блок сравнения, генератор тактовых импульсов, элемент НЕ, элемент И и элемент

ИЛИ, причем выход мультиплексора соединен с первым информационным входом коммутатора, второй информационный вход которого является информационным входом устройства, выход коммутатора соединен с информационным входом первого регистра, выход которого соединен с первым информационным входом блока сравнения и вторыми информационными входами блоков сравнения группы, выход второго регистра соединен с вторым информационным входом блока сравнеНия, выход "Меньше" которого соединен с первыми входами элементов И группы и входом элемента НЕ, выход которого соединен с первым входом элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с входом записи первого регистра, второй вход элемента ИЛИ, управляющий вход коммутатора и вход записи второго регистра подключены к входу запуска устройства, выход генератора тактовых импульсов соединен с втОрым входом элемента И, выходы "Меньше" блоков сравнения группы соединены с соответствующими информационными входами дешифратора, выход которого соединен с управляющим входом мультиплексора, каждый i- é разряд выхода второго регистра соединен с (!+)-1)-м разрядом входа уменьшаемого j-го блока вычитания группы, разряды выхода первого регистра соединены с вторыми входами соответствующих элементов И группы, выходы которых подключены к соответствующим разрядам информационного входа устройства.

1734094

Мю АЬ абдт

lюа 1Ю11

1бт

Составитель B.Ãðå÷íåâ

Техред M.Ìîðãåíòàë Корректор М.Кучерявая

Редактор А.Долинич

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

Заказ 1670 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5