Логический элемент на мдп-транзисторах

Иллюстрации

Показать всеРеферат

Назначение: использование в МДП-интегральных схемах в качестве многофункционального логического элемента. Сущность изобретения: устройство содержит пять транзисторов первого типа и четыре транзистора второго типа, четыре выходные шины и две входные шины. 1 ил.

COIO3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 Н 03 К 19/094, 19/21

ГОСУДАРСТВ Е ННЫ Й КОМИТЕ!

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

4 (гд () О 0 »

К АВТОРСКОМУ СВИ4ЕТЕЛЬСТВУ (21) 4869990/21 (22) 13.08,90 (46) 15.,05.92. Бюл. ¹ 18 (71) Научно-исследовательский центр физики и технологии (72) А.А, Кураев (53) 621.374(088.8) (56) Авторское свидетел ьство СССР

¹1295512,,кл,,Н 03 К 19/094, 1985, Авторское свидетельство СССР

¹1480116,,кл,,Н 03 К 19/094, 1987.

Изобретение относится к вычислительной технике и можег быть использовано в

МДП интегральных схемах в качестве многофункционального логического элемента, Известен логический элемент на МДП транзисторах, содержащий семь транзисторов первого типа и семь транзисторов второго типа.

Недостатком такого устройства является значительное количество транзисторов.

Наиболее близким по технической сущности к заявляемому устройству является выбранный в качестве прототипа логический элемент на КМДП транзисторах, содержащий шесть транзисторов первого типа м пять транзисторов второго типа, Недостатком известн зго устройства является значительное число транзисторов, уменьшение числа которых в интегральном исполнении позволит уменьшить площадь устройства и, следовательно, повысить процент выхода годных ИС, а в дискретном исполнении — повысить надежность.

Цель изобретения — увеличение процента выхода годных ИС в случае интегрального исполнения и увеличение надежности в слуБЫ 1734206 А1 (54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДПТРАНЗИСТОРАХ (57) Назначение: использование в МДП-интегральных схемах в качестве многофункционального логического элемента. Сущность изобретения: устройство содержит пять транзисторов первого типа и четыре транзистора второго типа, четыре выходные шины и две входные шины, 1 ил, чае дискретного исполнения логического элемента на МДП транзисторах.

Указанная цель достигается тем, что в логический элемент на МДП транзисторах, содержащий пять транзисторов первого типа и четыре транзистора второго типа, истоки первого, третьего транзисторов первого типа подключены к шине питания, а истоки первого, третьего, четвертого транзисторов второго типа подключены к первой входной шине, затвор пятого транзистора первого типа и затворы второго, четвертого, транзисторов второго типа подключены к второй входной шине, сток второго транзистора первого типа, стоки третьего, четвертого транзисторов второго типа подключены к первой выходной шине, стоки третьего и четвертого транзисторов первого типа подключены к второй выходной шине, сток пятого транзистора первого типа подключен к третьей выходной шине, стоки первого транзистора первого типа и первого транзистора второго типа подключены к четвертой выходной шине, введены исток пятого транзистора первого типа подключенный к первой входной шине, исток второго транзистора первого типа.

1734206

55 подключенный к второй выходной шине, исток четвертого, затвор второго транзисторов первого типа и сток второго транзистора второго типа, подключенные к третьей выходной шине, затвор четвертого транзистора первого типа и исток второго транзистора второго типа, подключенные к четвертой выходной шине.

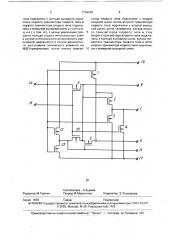

На чертеже представлена принципиальная схема логического элемента на МПД транзисторах.

Логический элемент на МПД транзисторах содержит первую выходную шину 1, к которой подключены сток второго транзистора 2 первого типа, стоки третьего 3 и четвертого 4 транзисторов второго типа, вторую выходную шину 5, к которой подключены стоки четвертого 6 и третьего 7, исток второго 2 транзисторов первого типа, третью выходную шину 8, к которой подключены сток пятого 9, исток четвертого 6, затвор второго 2 транзисторов первого типа, сток второго 10 транзистора второго типа, четвертую выходную шину 11, к которой подключены сток первого 13, исток второго

10 транзисторов второго типа, первую входную шину 14, к которой подключены затворы третьего 7, первого 12, исток пятого 9 транзисторов первого типа, затворы первого 13, третьего 3 транзисторов второго типа, вторую входную шину 15, к которой подключены затворы пятого 9 транзистора первого типа, затвор второго 10, четвертого 4 транзисторов второго типа, шину питания 16, к которой подключены истоки первого 12, третьего 7 транзисторов первого типа, общую шину 17, к которой подключены истоки первого 13, третьего 3, четвертого 4 транзисторов второго типа.

Устройство работает следующим образом.

На входные шины 14 и 15 подаются логические сигналы. На первой выходной шине 1 реализуется функция конъюнкции дополняющих входных логических сигналов

Y1 = X1 Х2. На второй выходной шине 5 реализуется функция дизьюнкции тех же сигналов Y2 = X1+X2. На третьей выходной шине 8 реализуется функция сравнения

Y3 = X1X2 + X1X2, а на четвертой выходной шине 11 — функция отрицания Y4 = Х1, При подаче на входные шины набора

0,0 соответственно первый 12, второй 2, третий 7, пятый 9 транзисторы первого типа открыты, а четвертый 6 транзистор первого типа, первый 13, второй 10, третий 3, четвертый 4 транзисторы второго типа закрыты.

При этом на первой 1, второй 5, и четвертой

11 выходных шинах устанавливается сигнал

"1", а на третьей 8 выходной шине — "0".

При подаче на входные шины набора 1, 15 соответственно, первый 12, второй 2, третий 7, пятый 9 транзисторы первого типа закрыты, а четвертый 6 транзистор первого типа и первый 13, второй 10, третий 3, четвертый 4 транзисторы второго типа открыты, При этом на всех выходных шинах 1, 5, 8, 11 устанавливается сигнал "0", При подаче на входные шины набора 1,0 соответственно, первый12, второй 2, третий

7 транзисторы первого типа и второй 10, четвертый транзисторы второго типа закрыты, а четвертый 6, пятый 9 транзисторы первого типа и первый 13, третий 3 транзисторы второго типа открыты. При этом на первой 1 и четвертой 11 выходных шинах устанавливается сигнал "0", а на второй 5 и третьей 8 выходных шинах устанавливается сигнал "1", При подаче на входные шины набора 0,1 соответственно, первый 12, третий 7 транзисторы первого типа и второй 10, четвертый 4 транзисторы второго типа открыты, а второй 2, четвертый 6, пятый 9 транзисторы первого типа и первый 13, третий 3 транзисторы второго типа закрыты. При этом на первой 1 выходной шине устанавливается сигнал "0", а на второй 5, третьей 8 и четвертой 11 выходных шинах устанавливается сигнал "1", Уменьшение количества транзисторов позволит уменьшить площадь устройства в интегральном исполнении, что в свою очередь повысит процент выхода годных ИС, а в дискретном исполнении позволит повысить надежность устройства.

Формула изобретения

Логический элемент на МДП-транзисторах, содержащий пять транзисторов первого типа и четыре транзистора второго типа, истоки первого, третьего транзисторов первого типа подключены к шине питания, а истоки первого, третьего и четвертого транзисторов второго типа подключены к общей шине, затворы первого и третьего транзисторов первого типа и первого и третьего транзисторов второго типа подключены к первой входной шине, затвор пятого транзистора первого типа и затворы второго и четвертого транзисторов второго типа подключены к второй входной шине, сток второго транзистора первого типа, стоки третьего и четвертого транзисторов второго типа подключены к первой выходной шине, стоки третьего и четвертого транзисторов первого типа подключены к второй выходной шине, сток пятого транзистора первого

1734206

Составитель А.Кураев

Техред М.Моргентал Корректор Э.Лончакова

Редактор М.Товтин

Заказ 1676 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул,Гагарина, 101 типа подключен к третьей выходной шине, стоки первого транзистора первого типа и первого транзистора второго типа подключены к четвертой выходной шине, о т л и ч а юшийся тем, что, с целью увеличения процента выхода годных интегральных схем в случае интегрального исполнения и увеличения надежности в случае дискретного исполнения логического элемента на

МДП-транзисторах, исток пятого транзистора первого типа подключен к первой входной шине, исток второго транзистора первого типа подключен к второй выходной шине, исток четвертого, затвор второ5 го транзисторов первого типа и сток второго транзистора второго типа подключены к третьей выходной шине, затвор четвертого транзистора первого типа и исток второго транзистора второго типа подключе10 ны к четвертой выходной шине.