Ik-триггер

Иллюстрации

Показать всеРеферат

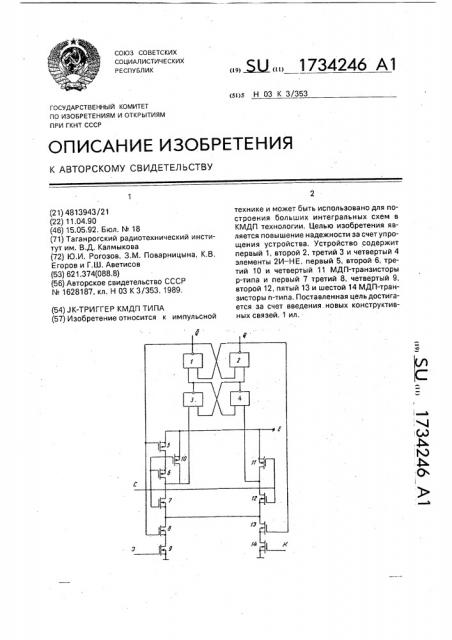

Изобретение относится к импульсной технике и может быть использовано для построения больших интегральных схем в КМДП технологии. Целью изобретения является повышение надежности за счет упрощения устройства. Устройство содержит первый 1, второй 2, третий 3 и четвертый 4 элементы 2И-НЕ, первый 5, второй 6, третий 10 и четвертый 11 МДП-транзисторы р-типа и первый 7 третий 8, четвертый 9, второй 12, пятый 13 и шестой 14 МДП-транзисторы n-типа. Поставленная цель достигается за счет введения новых конструктивных связей. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)я Н 03 К 3/353

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4813943/21 (22) 11.04.90 (46) 15.05.92, Бюл. М 18 (71) Таганрогский радиотехнический институт им. В.Д. Калмыкова (72) Ю.И. Рогозов, З.M. Поварницына, К.В, Егоров и Г,Ш, Аветисов (53) 621.374(088.8) (56) Авторское свидетельство СССР

М 1628187, кл. Н 03 К 3/353, 1989. (54) JK-ТРИГГЕР КМДП ТИПА (57) Изобретение относится к импульсной

„„5LI„„1734246 А1 технике и может быть использовано для построения больших интегральных схем в

КМДП технологии. Целью изобретения является повышение надежности за счет упрощения устройства. Устройство содержит первый I, второй 2, третий 3 и четвертый 4 элементы 2И вЂ” НЕ, первый 5, второй 6, третий 10 и четвертый 11 МДП-транзисторы р-типа и первый 7 третий 8, четвертый 9, второй 12, пятый 13 и шестой 14 МДП-транзисторы п-типа, Поставленная цель достигается за счет введения. новых конструктивных связей. 1 ил.

1734246

20

35

Изобретение относится к импульсной технике и может быть использовано для построения больших интегральных схем в

КМДП технологии.

Известен J К-триггер КМДП типа, содержащий основной и вспомогательный триггеры, а также устройство управления (МС

140276). Между основным и вспомогательным триггерами, а также между элементами каждого из триггеров включены двунаправленные ключи (см. описание схем в каталоге фирмы МОТОРНО А за 1978 г,), Основным недостатком триггера является низкая помехоустойчивость за счет использования двунаправленных ключей, которые требуют обеспечения синхронного парафазного управления. Из-за того, что обеспечить синхронность технологически трудно, в схеме возникают сквозные токи, приводящие к "состязанию" сигналов и снижению помехоустойчивости.

Наиболее близким к предлагаемому является JK-триггер, построенный по методу токовых соотношений, содержащий непосредственно связанные основной и дополнительные триггеры, а также устройство управления, состоящее из двух трехвходовых элементов И вЂ” Н Е и формирователя токовых соотношений.

Недостатком устройства является то, что для его построения необходимо большое число транзисторов и, как следствие, JK-триггер занимает достаточно большую площадь на кристалле.

Цель изобретения — повышение надежности за счет упрощения устройства.

Поставленная цель достигается -.ем, что в устройство, содержащее дополнительный триггер с непосредственными связями на первом и втором элементах 2И вЂ” НЕ, причем выходы последних соответственно соединены с инверсным и прямым выходами устройства, первый, второй, третий и четвертый

МДП-транзисторы р-типа, первый и второй

МДП-транзисторы п-типа, истоки первого, третьего и четвертого МДП-транзисторов ртипа объединены с шиной питания, сток первого и исток второго МДП-транзисторов р-типа объединены, стоки второго и третьего транзисторов р-типа соединены со стоком первого транзистора п-типа, исток последнего объединен с истоком второго транзистора п-типа, сток которого соединен со стоком четвертого транзистора р-типа, затворы второго, третьего и четвертого транзисторов р-типа и затворы первого и второго транзисторов и-типа объединены с входной тактовой шиной, введены третий и четвертый элементы 2И-НЕ, третий, четвертый, пятый и шестой МДП-транзисторы итипа, причем третий и четвертый элементы

2И-НЕ образуют основной триггер с непосредственными связями, выходы третьего и четвертого элементов 2И вЂ” НЕ соответственно соединены с вторыми входами первого и второго элементов 2И вЂ” НЕ, стоки третьего и четвертого МДП-транзисторов р-типа соответственно соединены с вторыми входами третьего и четвертого элементов 2И вЂ” НЕ, выходы первого и второго элементов 2И вЂ” НЕ соответственно соединены с затворами первого МДП-транзистора р-типа, затвором третьего МДП-транзистора и-типа и затвором пятого МДП-транзистора п-типа, сток последнего соединен со стоком третьего

МДП-транзистора п-типа, истоки третьего и пятого МДП-транзисторов и-типа соответственно соединены со стоками четвертого и шестого МДП-транзисторов п-типа, истоки которых объединены с общей шиной, а затворы соответственно соединены с J- и Квходами устройства, На чертеже приведена электрическая принципиальная схема JK-триггера КМДПтипа, JK-триггер содержит первый 1, второй 2, третий 3 и четвертый 4 элементы 2И вЂ” НЕ, первый 5, второй 6, третий 10 и четвертый

11 МДП-тразисторы р-типа и первый 7, третий 8, четвертый 9, второй 12, пятый 13 и шестой 14 МДП-транзисторы и-типа. Выход элемента И вЂ” НЕ 1 соединен с первым входом элемента 2, с затворами транзисторов

5, 8 и инверсным выходом устройства; выход элемента 2 подключен к первому входу элемента 1, затвору транзистора 13 и прямому выходу устройства; выход элемента 3 соединен с вторым входом элемента 1 и первым входом элемента 4, выход последнего подключен соогветственно к второму входу элемента 2 и первому входу элемента

3, истоки транзисторов 5, 10, 11 объединены с шиной питания и подложками транзисторов 5, 10, 11, сток транзистора 10 соединен со стоками транзисторов 6, 7 и вторым входом элемента 3, второй вход элемента 4 соединен со стоками транзисторов 11, 12, стоки транзисторов 8, 13 объединены с истоками транзистора 7, 12, исток транзистора 8 соединен со стоком транзистора 9, исток последнего объединен с истоком транзистора 14, подложками транзисторов

9, 14 и общей шиной; затворы транзисторов

6. 7, 10, 11, 12 объединены с тактовой входной шиной; затворы транзисторов 9, 14 соответственно соединены с J- и К-входами устройства, исток транзистора 13 соединен со стоком транзистора 14, Прежде чем описывать работу устройства, остановимся на методе схемотехниче1734246

-ской реализации уравнения Qt=1-0м, которое соответствует режиму записи информации в JK-триггер (c=1 - О), Операция вычитания выполняется схемой сравнения на основе тактируемого триггера на третьем

3, четвертом 4 элементах 2И вЂ” Н Е, В качестве сравниваемых величин используются токи через транзисторы 5, 6, 10, 11. При этом предполагается, что входные емкости (C»<) и пороговые напряжения (U„oр) элементов

3, 4 идентичны.

Известно, что время нарастания напряжения до порогового уровня определяется

snop Свх соотношением tH —, где I»p — ток, 1зар протекающий через транзисторы 5, 6, 10 и

11. Если по тактовому импульсу закрыть инверторы 3, 4 (т.е. сформировать на их выходах потенциалы высокого логического уровня), то по окончании тактового импульса (с=1 - ° О) быстрее откроется тот из инвертором 3, 4, входной ток (на вторых входах) которого выше (при наличии на остальных входах инверторов 3, 4 сигналов высокого логического уровня).

Таким образом, предлагаемое соединение транзисторов 5, 6, 10, 11 позволяет получать различные соотношения между входными токами инверторов 3, 4. Если принять, например, что сопротивления каналов транзисторов 5, 6 равны R/6, транзистора

10 — R, транзистора 11 — R/2, то при различных комбинациях входных сигналов всегда будет выполняться соотношение между входными токами инверторов 3 (1з) и 4(14), равное 1/2 или 2, т,е. всегда один из токов больше другого в два раза.

Устройство работает следующим образом.

Предположим, что в режиме хранения (при с=0) на выходе устройства имеем сигнал Q=1, Q=O. На выходе инвертора 4 будем иметь сигнал низкого логического уровня, который будет фиксировать высокие логические уровни на выходах инверторов 2, 3.

Транзисторы 7 и 12 будут закрыты, поэтому изменения сигналов на J- и К-входах не будут влиять на состояние основного и дополнительного триггеров. При этом транзистор

8 закрыт, а транзисторы 5, 6, 10, 11, 13 открыты. Поскольку транзисторы 7, 12 закрыты, то независимо от состояния основного и дополнительного триггеров устройство будет находиться в режиме хранения.

С приходом тактового импульса с=1 транзисторы 7, 12 открываются, а транзисторы 6, 10, 11 переходят в закрытое состояние. Транзистор 8 закрыт, а транзистор 13

55 открыт (Q=O, 0=1), Если.1=1, K=O, то с приходом тактового импульса состояние основного триггера (на инверторах 3, 4) не изменяется, так как транзисторы 5, 8 закрыты. Если J=O, K=1, то транзисторы 13, 14 открыты и на вторых входах инверторов 3, 4 имеем сигнал низкого логического уровня (транзисторы 7, 12 открыты), что приведет к формированию на выходах инверторов 3. 4 сигналов высокого логического уровня. При этом состоя ние. до пол нител ьного триггера не изменяется. По срезу тактового импульса (c=1 0) транзисторы 7, 12 закрываются, транзисторы 6, 10, 11 переходят в открытое состояние. Поскольку транзистор 5 открыт (Q=0), то входной ток инвертора 3 в два раза больше входного тока инвертора 4. Поэтому инвертор 3 откроется быстрее, что приведет к изменению состояния дополнительного триггера на противоположное.

Предположим, что потактовому импульсу на входах устройства имеем сигналы высокого логического уровня .1=К=1. B этом случае транзисторы 7, 9, 14 открыты и сигнал низкого логического уровня на входах инверторов 3, 4 формируется по цепи, которая определяется состоянием дополнительного триггера на инверторах 1, 2. Если 0=1, то открыт транзистор 14, а если Q=O, то находится в открытом состоянии транзистор 8. В последнем случае сигнал низкого логического уровня на входах инверторов 3, 4 формируется соответственно через транзисторы 3, 8, 7, 12. Тогда по срезу тактового импульса в зависимостиот состояния дополнительного триггера 0=0 (транзистор 5 открыт) быстрее перейдет в открытое состояние инвертор 3 или при 8=1 (транзистор 5 закрыт) быстрее откроется инвертор 4. При веденный порядок переключения инверторов основного триггера (3, 4) определяется указанными выше соотношениями между их входными токами. Таким образом, при1=К=1 триггер работает в счетном режиме.

Из описания следует, что рассматриваемый триггер выполняет функцию управляемого по cpeayJK-триггера.

В отличие от схемы прототипа для реализации данной схемы требуется в 1,45 раза меньше транзисторов, что позволяет практически в два раза сократить площадь, занимаемую устройством на кристалле, Таким образом, повышается надежность триггера за счет его упрощения.

Формула изобретения

JK-триггер, на транзисторах КМДП типа, содержащий дополнительный триггер с непосредственными связями на первом и втором элементах 2И-НЕ, выходы которых соответственно соединены с инверсным и

1734246

30

40

50

Составитель Г.Аветисов

Редактор А.Маковская Техред М,Моргентал Корректор Н.Ревская

Заказ 1678 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, yn,Гагарина, 101 прямым выходами устройства, первый-четвертый МДП-транзисторы р-типа, первый и второй МДП-транзисторы п-типа, истоки первого, третьего и четвертого МДП-транзисторов р-типа соединены с шиной пита- 5 ния, сток первого и исток второго

МДП-транзисторов р-типа соединены, стоки второго и третьего транзисторов р-типа соединены со стоком первого транзистора п-типа, исток которого соединен с истоком 10 второго транзистора п-типа, сток которого соединен со стоком четвертого транзистора р-типа, затворы второго, третьего и четвертого транзисторов р-типа и затворы первого и второго транзисторов п-типа соединены с 15 входной тактовой шиной, о т л и ч а ю щ и йс я тем, что, с целью повышения надежности за счет упрощения устройства, в него введены третий и четвертый элементы 2И—

НЕ, третий, четвертый, пятый и шестой 20

МДП-транзисторы п-типа, причем третий и четвертый элементы 2И вЂ” НЕ образуют основной триггер с непосредственными связями, выходы третьего и четвертого элементов 2И-НЕ соответственно соединены с вторыми входами первого и второго элементов 2И вЂ” НЕ, стоки третьего и четвертого

МДП-транзисторов р-типа соответственно соединены с вторыми входами третьего и четвертого элементов 2И вЂ” HE, выходы первого и второго элементов 2И вЂ” НЕ соответственно соединены с затворами первого

МДП-транзистора р-типа, затвором третьего МДП-транзистора и-типа и затвором пятого МДП-транзистора п-типа, сток которого соединен со стоком третьего МДПтранзистора п-типа, и истоком первого

МДП-транзистора п-типа, истоки третьего и пятого МДП-транзисторов и-типа соответственно соединены со стоками четвертого и шестого МДП-транзисторов п-типа, истоки которых соединены с общей шиной, а затворы соответственно соединены с и К входами устройства,