Устройство для идентификации объектов распознавания

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и может быть использовано в системах управления работой роботов. Цель изобретения - повышение быстродействия устройства достигается введением третьего, четвертого, пятого и шестого элементов ИЛИ, второго, третьего, четвертого, пятого, шестого и седьмого элементов задержки, третьего и четвертого элементов И, третьей и четвертой групп элементов И и четвертого регистра Это позволяет использовать такое устройство для идентификации характерного кода объекта., 1 ил

СОЕЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„173 ())5 О 06 К 9/00

OrlHCAHHE ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPblTHRM

ПРИ ГКНТ CCCP

К АВТОРСИОМ,Ф СВИДЕТЕЛЬСТВУ

1 . (21) 4709464/24 (22) 23 ° 06.89 (46) 23.05.92, Бюл. М 19 . (71) Каунасский политехнический институт им. А. Снечкуса (72) В.Й. Ветерис, Л.-P.Â. Монтвилайте, P.-A,В. Ветярис и Э.К. Байорунас (53) 621 327 (088.8) (56) Патент США 4484306, кл. G 06 К 9/00, опублик. 1984. (54) УСТРОАСТВО ДЛЯ ИДЕНТИФИКАЦИИ

ОБЬЕКТОВ РАСПОЗНАВАНИЯ (57) Изобретение относится к автомаИзобретение относится к автоматике и может быть использовано в системах управления работой роботов.

Цель изобретения - повышение быстродействия устройства.

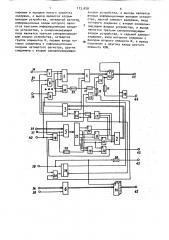

На чертеже представлена блок-схема предлагаемого устройства.

Устройство включает первый 1 и второй 2 блоки памяти, первый 3, второй 4, третий 5 и четвертый 6 ре" гистры, первую 7-9, вторую 10-12, третью 13 и четвертую 14 группы элементов И, дешифратор 15, первый 16, второй 17, третий 18, четвертый 19, пятый 20 и шестой 21 элементы ИЛИ, первый 22, второй 23 и третий 24 элементы И, первый 25, второй 26, третий 27, четвертый 28, пятый 29 и шестой 30 элементы задержки, триг-. гер 31 блокировки, четвертый элемент

И 32 и седьмой элемент 33 задержки.

2 тике и может быть использовано в системах управления работой роботов.

Цель изобретения - повышение быстродействия устройства достигается вве- . дением третьего, четвертого, пятого и шестого элементов ИЛИ, второго, третьего, четвертого, пятого, шестого и седьмого элементов задержки, третьего и четвертого элементов И, третьей и четвертой групп элементов

И и четвертого регистра. Это позволя. ет использовать такое устройство для идентификации характерного кода объекта. 1 ил.

На чертеже также показаны первая

34, вторая 35 и третья 36 группы инФормационных входов устройств, пер- вый 37, второй 38 и третий 39 синхронизирующие входы, вход 40 - установочный вход "Уст,0" устройства, а также первый 41 и второй 42 информационные выходы устройства, первый 43, второй 44 и третий 45 синхрониэирующие выходы устройства.

Перед началом работы устройства сигналом "Уст.0" регистры 3 и 4 сбрасываются в исходное состояние непосредственно, регистр 5 - через элемент ИЛИ 18, а триггер 31 - через элемент ИЛИ 20.

Перед началом работы устройства на информационные входы регистра 6 с входа 36 подается код базового адреса (идентифицируемого изображе- ния обьекта), который сигналом с

1735878

Базовый адрес с выхода блока 1 памяти поступает на информационные входы регистра 4, на синхронизирую5 щий вход которого подается тот же импульс считывания, прошедший через элемент ИЛИ 16 и задержанный элементом 25 задержки на время считывания базового адреса из блока 1 памяти.

После занесения базового адреса в регистр 4 импульсом, задержанным элементом 27 задержки на время пере- ходных процессов в регистре 4 и поступающим через элемент ИЛИ 21 на импульсные входы элементов И 13, ба-: зовый адрес выдается на выход 41. Тот же импульс считывания с. выхода элемента ИЛИ. 21, задержанный элементом

29 на время считывания кода, через элемент И 32, открытый по второму входу, выдается на выход 44 в качестве сигнала готовности приема параметров иэ памяти устройства.

По указанному адресу идет .обращение импульсом с выхода 44, и на экран дисплея выдается вся требуемая информация об объекте идентификации„

Для смены кадра и предъявления исследующего изображения объекта на

З-0 прямой вход триггера 31 подается сигнал, который устанавливает триггер 31 в единичное состояние, при котором элемент И 24 закрыт, а элемент И 23 открыт.

Кроме того, этим же импульсом, поступающим на входы элементов И 14, код адреса очередного. изображения объекта выдается на выход 42 устройства, а через элемент 30 задерж4О. ки, задерживающий импульс на время переписи кода, на выход 45 выдается импульс считывания изображения объек та на экран дисплея по указанному адресу.

Для распознавания этого объекта в регистр 5 вновь вводится идентификационный код объекта, подлежащего распознаванию, и описанные процедуры повторяются.

50 входа 39, подаваемым на синхровход, записывается в регистр б.

После этого устройство готово к работе и работает следуюцим образом.

Идентификационный код, характеризующий объект, подлежащий идентификации, с входа 35 поступает на вход регистра 5 и записывается в него синхросигналом с входа 37. Идентификационный код. расшифровывается дешифратором 15, и на входе одного из элементов И 10-12, соответствующего поступившему коду, будет высокий потенциал, открывающий, соответствующий элемент И 10-12 по одному входу, Иа другой вход указанного элемента И к этому моменту времени поступает импульс с выхода элемента 2о задержки, задержанный на время переходных процессов в регистре 5 и дешифраторе l5.

Поступивший импульс проходит через один из элементов И 10"12 прямо на вход считывания Фиксированной ячейки блока 2 памяти, в которой записано "кодовое слово", единичные значения разрядов которого характеризуют описание идентификационного объекта в пространстве признаков, которые поступают на его входы 34.

Содержимое .считанной Фиксированной ячейки поступает на информационные входы регистра 3, а сам импульс считывания "кодового слова" идентиФикации из блока 2 памяти и через элемент И 24, открытый по второму входу высоким потенциалом с нулевого выхода триггера 31, поступает на синхронизирующий вход регистра 3, записывая в него поступивший код

"слово идентификации".

В зависимости от состояния различ-. ных разрядов регистра 3 их выходными потенциалами определяется состояние элементов И 7"9, через которые поступают сигналы о наличии признаков, характеризующих объект идентификации.

Допустим, что по сигналу о наличии признака, поступившему через элемент И 7, соответствующий разряд регистра 3 находится в "единице".

Тогда этот импульс проходит через элемент И 7 на вход считывания фиксированной ячейки блока 1 памяти, где хранится базовый адрес, в котором записаны параметры, соответству- ющие упомянутому признаку.

Импульсом с входа 37, задержанным элементом 28 нв время переходных . процессов и проходящим через указанный элемент из элементов И 10-12,происходит обращение к фиксированной ячейке блока 2, B результате "кодовое слово" идентификации с выхода блока 2 выставляется на информацион-. ных входах регистра 3. Однако повтор1

1735878 ного занесения кода в регистр 3 не происходит, так как импульс считывания через элемент ИЛИ 17 и элемент

26 задержки не проходит на синхровход регистра 3, потому что элемент И 24 заперт низким потенциалом с нулевого выхода триггера 31 блокировки.

Элемент И 23 открыт, поэтому с выхода элемента 26 задержки импульс проходит через него и далее поступает на вход элемента 33 задержки, а также через элемент КЛИ 20 возвращает триггер 31 в исходное состояние, снимая блокировку элементов И 13 и 32.

Тот же импульс, задержанный элементом 33 на время срабатывания триггера 31, через элемент КЛИ 21 проходит на вход переписи содержимого базового адреса регистра 2 и через элементы И 13 на выход 41, а после переписи кода и задержки элементом

29 на время переписи кода этот импульс через элемент И 32 выдается на выход. ф о р и у л а изобретения

Устройство для идентификации объектов распознавания, содержащее первую группу элементов И, первые входы которых являются первыми информационными входами устройства, вторые соединены с выходами первого регистра, а выходы подключены к входу управления первого блока памяти и к входам первого элемента ИЛИ, первый элемент задержки, вход которого соединен с выходом первого элемента ИЛИ, второй регистр, информационные входы которого соединены с выходом первого блока памяти, синхронизирующий вход соединен с выходом первого элемента задержки, а вход сброса является установочным входом устройсТва, третий регистр, информационные выходы которого являются вторыми информациднными входами устройства, синхронизирующий вход является первым синхронизирующим входом устройства, а выходы соединены с входами дешифраторов, первый выход которого соединен с первым входом элементов И второй группы, выходы которых соединены с входами второго элемента ИЛИ и с входом управления второго блока памяти, выходы которого подключены к информационным входам первого регистра, ну50

55 торых соединены с информационным выходом второго регистра, с нулевым выходом триггера блокировки и с выходом шестого элемента ИЛИ, а выходы являются первым информационным выходом устройства, пятый элемент задержки, вход которого соединен с выходом шестого элемента ИЛИ, четвертый элемент И, входы которого соеди-, нены с нулевым выходом триггера блолевой вход которого соединен с установочным входом устройства, первый и второй элементы И, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия устройства, в него введены третий элемент ИЛИ, один вход которого соединен с установочным входом устройства, другой подключен к выходу первого элемента

И, а выход соединен с нулевым входом третьего регистра, второй элемент задержки, вход которого соединен с выходом второго элемента ИЛИ, а вы15 ход подключен к третьему входу третьего элемента ИЛИ и к одному входу второго элемента И, третий элемент

И, один вход которого соединен с выходом второго элемента задержки, а

1 выход соединен с синхронизирующим входом первого регистра, третий элемент задержки, вход которого соединен с выходом первого элемента задержки, четвертый элемент ИЛИ, входы которого соединены с вторым информационным выходом дешифратора, .а выход соединен с первым входом первого элемента И, четвертый элемент задержки, вход которого подключен к первому синхронизирующему входу устЗО ройства, а выход соединен с вторым входом элемента И второй группы и с вторым входом первого элемента И, выход которого является IlBpBblM вы.ходом устройства, пятый элемент ИЛИ, первый вход которого подключен к

35 .установочному входу устройства, Ь другой соединен с выходом второго элемента И, триггер блокировки, единичный вход которого является вторым п синхронизирующим выходом устройства, нулевой вход подключен к выходу пятого элемента ИЛИ, единичный выход триггера блокировки соединен с вторым входом второго эЛемента И, а ну„5 левой выход подключен к второму входу третьего элемента И, шестой элемент ИЛИ, один вход которого соединен с выходом третьего элемента задержки, третья группа элементов И, входы кокировки и выходом пятого элемента задержки, а выход является вторым выходом устройства, четвертый регистр, информационные входы которого являются третьими информационными входами .устройства, а синхронизирующий вход является третьим синхронизирующим входом устройства, четвертая группа элементов И, первые входы которых соединены с информационными входами четвертого регистра, другие соединены с вторым синхронизирующим

>73>878 8 входом устройства, а выходы являются вторым информационным выходом устройства, шестой элемент задержки, вход которого соединен с вторым синхронизирующим входом устройства, а выход является третьим синхронизирующим входом устройства, и седьмой элемент задержки, вход которого соединен с выходом второго элемента И, а выход подключен к другому входу шестого элемента ИЛИ.