Устройство для программной обработки цифровой информации @

Иллюстрации

Показать всеРеферат

Изобретение относится к технике обработки цифровых данных и может, найти применение для программной обработки цифровой информации. Целью изобретения является повышение эффективности использования за счет ускорения процесса обработки цифровой информации. Устройство работает по четырем тактам по программе, записанной в формирователе 4 команд программной обработки. На первом такте формируется управляющее слово, которое поступает на формирователь 10 сигналов управления, на коммутатор 8 адреса, на коммутатор 6 операнда А и на дешифратор 5 команд. На втором такте производится считывание операнда В, а блок 3 арифметико-логической обработки начинает выполнять заданную операцию. На третьем такте блок 3 арифметико-логической обработки заканчивает вычисление, а в формирователе 4 команд программной обработки записывается новое адресное слово. На четвертом такте результат обработки в блоке 3 арифметико-логической обработки записывается в блок 1 оперативной памяти и поступает по выходной шине прямого доступа в порт 2 вывода. 1 ил. (Л с.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 06 F 7/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ. (21) 4871394/10 (22) 03.10.90 (46) 30.05;92. Бюл. hb 20 (75) А.H.Æèxaðåâ, А.Л.Калныньш, Ю.Б.Шайкевич и В.Б.Дычаковский (53) 681.32(088,8) (56) Авторское свидетельство СССР

N 1513440, кл. G 06 F 7/00, 1987.

Microprocessor integrated circUits. San.

Diego, Data Corporation, 1984, р. 278-280. (54) УСТРОЙСТВО ДЛЯ ПРОГРАММНОЙ

ОБРАБОТКИ ЦИФРОВОЙ ИНФОРМАЦИИ (57) Изобретение относится к технике обра-. ботки цифровых данных и может. найти применение для программной обработки цифровой информации. Целью изобретения является повышение эффективности использования за счет ускорения процесса обработки Цифровой информации. Устройство

» . Ж 1737440 А1 работает по четырем тактам по программе, записанной в формирователе 4 команд программной обработки. На первом такте формируется управляющее слово, которое поступает на формирователь 10 сигналов управления, на коммутатор 8 адреса, на коммутатор 6 операнда "А" и на дешифратор 5 команд. На втором такте производится . считывание операнда "В", а блок 3 арифметико-логической обработки начинает выполнять заданную операцию. На третьем такте блок 3 арифметико-логической обработки заканчивает вычисление, а в формирователе 4 команд программной обработки записывается новое адресное слово. На четвертом такте результат обработки в блоке 3 арифметико-логической обработки записывается в блок 1 оперативной памяти и поступает по выходной шине прямого доступа в порт 2 вывода. 1 ил.

Ф

1737440

Изобретение относится к технике обработки цифровых данных, а именно к устройствам для программной обработки цифровой информации.

Известно устройство для программной обработки цифровой информации, содержащее блок oneðýòèâíoé памяти, соединенный с формирователем управляющих сигналов и включенный между портами ввода и вывода.

Недостаток известного устройства для программной обработки цифровой информации состоит. в том, что оно не позволяет обеспечить в ряде случаев требуемую производительность при обработке цифровой информации в режиме реального времени.

Известно также устройство для программной обработки цифровой информации, содержащее блок оперативной памяти, подключенный выходной шиной прямого доступа к входной шине прямого доступа порта вывода и соединенный входной шиной.данных с выходной шиной данных бло ка арифметика-логической обработки, подключенного выходной шиной переноса к входной шине переноса формирователя команд программной обработки и соединенного входной шиной сигнала управления с первой выходной шиной дешифратора команд, входная шина кода операций которогб подсоединена к выходной шине кода операций формирователя команд программной обработки, формирователь сигналов управления режимами работы, коммутатор .операнда "А"; коммутатор операнда "В", коммутатор адреса и порт ввода.

Недостаток этого устройства для программной обработки информации состоит в малой эффективности его использования, возникающей из-эа низкой скорости процесса обработки цифровой информации, Целью изобретения является повышение. эффективности использования устройства для программной обработки цифровой информации за счет ускорения процесса обработки цифровой информации.

С этой целью в устройстве для программной обработки цифровой информации, содержащем блок оперативной памяти, подключенный выходной шиной прямого доступа к входной шине прямого доступа порта вывода и соединенный входной шиНоА p3HHblx с выходной шиной данных блока арифметико-логической обработки, нодключейного выходной виной переноса к входной шине переноса формирователя команд программной обработки и соедиНеННого входной шиной сигнала управления с первой выходной шиной дешифратора команд, входная шина кода операций которого подсоединена к выходной шине кода операций формирователя команд программной обработки, формирователь сигналов управления режимами работы. коммутатор

5 операнда "А", коммутатор операнда "В", коммутатор адреса и порт ввода, выходная шина сигнала управления и выходная шина адреса формирователя команд программной обработки соединены соответственно с

30 входной шиной сигнала управления и входной шиной адреса формирователя сигналов управления режимами работы, который подключен первым, вторым, третьим и четверым выходами соответственно к входной

15 шине порта ввода, к входной шине сигнала управления коммутатора адреса, к входной шине сигнала управления коммутатора операнда "В" и к входной шине сигнала управления порта вывода, а входная шина даннйх

20 и выходная шина констант формирователя команд программной обработки соединены соответственнО с ВыхОднОЙ шиной данных блока арифметико-логической обработки и с входной шиной констант коммутатора

25 Операнда "А", подсоединенного входной шиной сигнала управления и входной шиной аккумулятора соответственно к второй выходной шине дешифратора команд и к выходной шине аккумулятора блока опера30 тивной памяти и соединенного выходной шиной с первой входной шиной данных блока арифметико-логической обработки, вторая входная шина данных которого подсоединена к выходной шине коммутато35 ра операнда "8", соединенного первой и второй входными шинами данных соответственно с выходной шиной порта ввода и с выходной шиной данных блока оперативной памяти. шина адреса которого подсое40 динена к выходной шине коммутатора адреса, соединенного первой и второй входными шинами данных соответственно с выходной шиной адреса формирователя команд программной обработки и с выход45 ной шиной индексного регистра блока оперативной памяти.

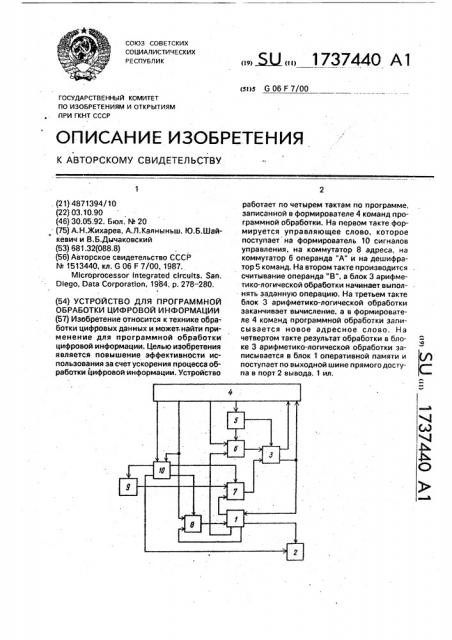

На чертеже изображен один из возможных вариантов предлагаемого устройства для программной обработки цифровой ин50 формации.

Устройство содержит блок 1 оперативной памяти, подключенный выходной шиной прямого достуйа к входной шине прямого доступа порта 2 вывода и соеди55 ненный входной шиной данных с выходной шиной данных блока 3 арифметико-логиче- ской обработки, формирователь 4 команд программной обработки, дешифратор 5 команд, коммутатор 6 операнда "А", коммутатор 7 операнда "В", коммутатор 8 адреса, 1737440 порт 9 ввода и формирователь 10 сигналов управления режимами работы. Блок 3 арифметико-логической обработки подключен выходной шиной переноса к входной шине переноса формирователя 4 команд програм- 5 мной обработки и соединен входной шиной сигнала управления с первой выходной шиной дешифратора 5 команд. подсоединенного входной шиной кода операций к выходной шине кода операций формирова- 10 теля 4 команд программной обработки.

Выходная шина сигнала управления и выходная шина адреса формирователя 4 команд программной обработки соединены соответственно с входной шиной сигнала 15 управления и входной шиной адреса формирователя 10 сигналов управления режимами работы, который подключен первым, вторым, третьим и четвертым выходами соответственно к входной шине порта 9 ввода, 20 к входной шине сигнала управления комму. татора 8 адреса, к входной шине сигнала управления коммутатора операнде "В" и к входной шине сигнала управления порта 2 вывода, При этом входная шина данных и 25 выходная. шина констант формирователя 4 команд программной обработки соединены соответственно с выходной шиной данных блока .3 арифметико-логической обработки и с входной шиной констант коммутатора 6 30 операнда "А". Коммутатор 6 операнда "А" подсоединен .входной шиной сигнала управления и входной шиной аКкумулятора соответственно к второй входной шине дешифратора 5 команд и к выходной шине 35 аккумулятора блока 1 оперативной памяти и соединен выходной шиной с первой входной шиной данных блока 3 арифметико-логической обработки. Вторая входная шина данных блока 3 арифметико-логической об- 40 работки подсоединена к выходной шине коммутатора операнда "B", соединенного первой и второй входными шинами данных соответственно с выходной шиной порта 9 ввода и с выходной шиной блока 1 оперативной 45 памяти. Шина адреса блока оперативной памяти подсоединена к выходной шине коаемутатора 8 адреса. соединенного первой м второй входными шинами данных соответственно с выходной шиной адреса формирова- 50 теля 4 команд программной обработки и с выходной шиной индексного регистра блока 1 оперативной. памяти,, Работа предлагаемого устройства для программной обработки цифровой имфор- 55 мации происходит следующим образом.

Формирователь 10 сигналов управления режимами работы управляет режимом работы порта 9 ввода, воздействующего на коммутатор 7 операнда "В". Коммутатор 7 операнда "В" обеспечивает подключение порта 9 авода к блоку 3 арифметико-логической обработки, что позволяет обрабатывать данные порта 9 ввода непосредственно через блок 3 эрифметико-логической обработки, Внешний сигнал из порта 9 ввода поступает на первую входную шину данных коммутатора 7 операнда "В", на вторую входную шинуданных которого подаются данные из блока оперативной памяти. При этом информация, поступившая с порта ввода и блока 1 оперативной памяти, в зависимости от сигнала на входной шине сигнала управлений, подаваемого с формирователя 10 сигналов управления режимами работы, проходит на вторую входную шину данных блока 3 арифметико-логической обработки.

На первую входную шину денных блока 3 эрифметико-логической обработки подается сигнал с выходной шинй коммутатора 6 операнде "А". который определяется сигналами с выходной шины констант формирователя 4 команд программной обработки или с выходной шины аккумулятора блока оперативной памяти в зависимости от сигнала на второй выходной шине дешифрато- . ра 5 команд, определяемого состоянием выходной шины кода операций формирова- теля 4 команд программной обработки. При этом блок 3 арифметико-логической обработки производит арифметико-логическую обработку информации в зависимости от состояния выходной шины кода операций формирователя 4 «омэнд программной обработки. Результат обработки в блоке 3 арифметико-логической обработки поступает на входные шины денных блока 1 оперативной памяти и формирователя 4. команд программной обработки и на входную шину переноса формирователя 4 команд программной обработки. Сигналы на входной шине данных и входной шине переноса формирователя 4 команд программной обработки определяют состояние его выходной шины кода операций. выходной шины констант, выходной шины адреса и выходной шины сигнала управления. При этом обеспечивается реализация последующей обработки информации пс программе, занесенной в память формирователя

4 команд программной обработки;

Устройство работает по программе, записанной в формирователе 4 команд программной обработки. При этом конкретный алгоритм каждого шага программы определяет управляющее слом формирователя 4 команд программной обработки. Устройство работает по четырем тактам. На первом такте формируется управляющее слово, которое поступает на формирователь 1О сигналов управления режимами работы, на

1737440 ной шиной прямого доступа к входной шине

40 прямого доступа порта вывода и соединенный входной шиной данных с выходной шиной данных блока арифметико-логической обработки, подключенного выходной шиной переноса к входной шине переноса формирователя команд программной обработки и соединенного входной шиной сигнала управления с первой выходной шиной дешифратора команд, входная шина кода операций которого подсоединена к

Составитель А. Жихарев

Редактор Т. Лошкарева Техред М,Моргентал Корректор М. Демчик

Заказ 1892 Тираж Подписное

ВНИИПИ Государственного комитете по изобретениям и открытиям при ГКНТ СССР

113035, Москве, Ж-35, Раушская нэб„4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101 коммутатор 8 адреса, на коммутатор 6 операндэ "А" и на дешифратор 5 команд. В зависимости от содержимого кода операций настраивается дешифратор 5 команд, выбирается операнд "А" (аккумулятор или константа) и определяются операции блока

3 арифметика-логической обработки. Если поле адресов управляющего слова содержит признак команд управления, формирователь 10 сигналов управления режимами работы вырабатывает сигналы управления, которые настраивают работу порта 9 ввода, коммутатора 8 адреса или коммутатора 7 операнда "В". На втором такте работы производится считывание операнда "В", а блок

3 арифметико-логической обработки начинает выполнять заданную операцию. На третьем такте блок 3 арифметико-логической обработки заканчивает вычисление, а в формирователе 4 команд программной обработки записывается новое адресное слово. На четвертом такте результат обработки в блоке 3 арифметико-логической обработки записывается в блок 1 оперативной памяти и поступает по выходной шине прямого доступа в порт 2 вывода. На следующем первом такте выбирается следующее управляющее слово и начинается новый цикл работы устройства, Предложенное устройство может быть выполнено в виде микросхемы и позволяет повысить производительность в режиме реального времени и эффективность использования аппэратурных средств.

<формула изобретения

Устройство для программной обработки цифровой информации, содержащее блок оперативной памяти, подключенный выход5

35 выходной шине кода операций формирователя команд программной обработки, формирователь сигналов управления режимами работы, коммутатор операнда "А", коммутатор операнда "В", коммутатор адреса и порт ввода, о т л и ч а ю щ е е с я тем, что, с целью повышения эффективности использования за счет ускорения процесса обработки цифровой информации, выходная шина сигнала управления и выходная шина адреса формирователя команд программной обработки соединены соответственно с входной шиной сигнала управления и входной шиной адреса формирователя сигналов управления режимами работы, который подключен первым, вторым, третьим и четвертым выходами соответственно к входной шине порта ввода, к входной шине сигнала управления коммутатора адреса, к входной шине сигна-. ла управления коммутатора операнда "В" и к входной шине сигнала управления порта вывода, а входная шина данных и выходная шина констант формирователя команд программной обработки соединены соответственно с выходной шиной данных блока арифметико-логической обработки и с входной шиной констант коммутатора операнда

"А", подсоединенного входной шиной констант управления и входной шиной аккумулятора соответственно к второй выходной шине дешифратора команд и к выходной шине аккумулятора блока оперативной памяти и соединенного выходной шиной с первой входной шиной данных блока арифметико-логической обработки,.вторая входная шина данных которого подсоединена к выходной шине коммутатора операнда "В", соединенного первой и второй входными винами данных соответственно с выходной шиной порта вводе и с выходной шиной данных блока оперативной памяти, шина адреса которого подсоединена к выходной шине коммутатора адреса, соединенного первой и второй входными шинами данных соответственно с выходной шиной адреса формирователя команд программной обработки и с выходной шиной индексного регистра блока оперативной памяти.