Устройство для запоминания трассы функционирования многопроцессорных систем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и позволяет восстановить реальную последовательность взаимодействия процессоров отлаживаемого устройства после окончания прогона отлаживаемых программ. Цель изобретения - расширение области применения за счет обеспечения возможности увеличения длины трассы межпроцессорных обменов. Устройство содержит два блока оперативной памяти, элемент НЕ, счетчик импульсов, мультиплексор . Дополнительно устройство содержит счетчик импульсов, мультиплексор, блок оперативной памяти, шифратор. Благодаря этим элементам и связям между ними создается положительный эффект, позволяющий за счет использования режима выборочной трассировки увеличить длину трассы межпроцессорных обменов. 2 ил.

СОЮЗ СОВЕТСКИХ

СО0ИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si)s G 06 F 11/28

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ. (21) 4826811/24 (22) 18.05.90 (46) 30,05.92. Бюл. М 20 (71) Инстьпут кибернетики им, В.M.Ãëóøêîâà (72) О.В.Цвелодуб (53) 681.3(088.8) (56) Электроника, 1980, т. 53, N. 17, с. 32-38.

Авторское свидетельство СССР

М 1446624, кл, G 06 F 11/28, 1987. (54) УСТРОЙСТВО ДЛЯ ЗАПОМИНАНИЯ

ТРАССЫ ФУНКЦИОНИРОВАНИЯ МНОГОПРОЦЕССОРНЫХ СИСТЕМ (57) Изобретение относится к вычислительной технике и позволяет восстановить реальную последовательность взаимодейстИзобретение относится к вычислительной технике и позволяет восстановить реальную последовательность взаимодействия процессоров отлаживающего устройства после окончания прогона отлаживаемых программ.

Цель изобретения.— расширение области применения за счет обеспечения возможности увеличения длины трассы межпроцессорных обменов.

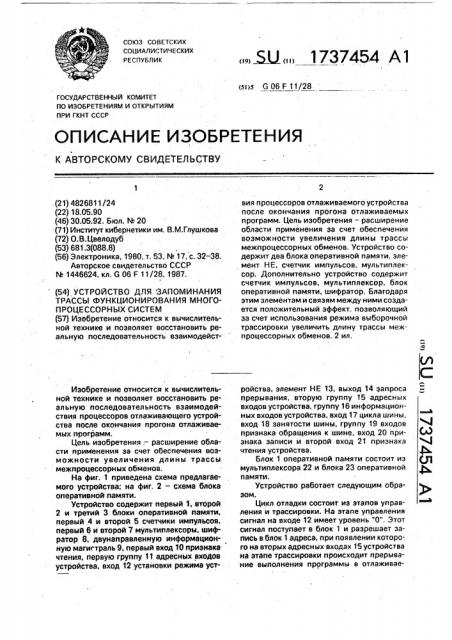

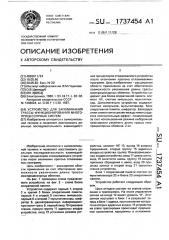

На фиг. 1 приведена схема предлагаемого устройства; на фиг. 2 — схема блока оперативной памяти.

Устройство содержи первый 1, второй

2 и третий 3 блоки оперативной памяти, первый 4 и второй 5 счетчики импульсов, первый 6 и второй 7 мультиплексоры, шифратор 8, двунаправленную информационную магистраль 9, первый вход 10 признака чтения, первую группу 11 адресных входов устройства, вход 12 установки режима уст„, БЦ„„1737454 Al вия процессоров отлаживаемого устройства после окончания прогона отлаживаемых программ. Цель изобретения — расширение области применения за счет обеспечения возможности увеличения .длины трассы межпроцессорных обменов. Устройство содержит два блока оперативной памяти, элемент НЕ; счетчик импульсов, мультиплексор. Дополнительно устройство содержит счетчик импульсов, мультиплексор, блок оперативной памяти, шифратор, Благодаря этим элементам и связям между ними создается положительный эффект. позволяющий за счет использования режима выборочной трассировки увеличить длину трассы межпроцессорных обменов. 2 ил. ройства, элемент НЕ 13, выход 14 запроса прерывания; вторую группу 15 адресных входов устройства, группу 16 информационЬ ных входов устройства, вход 17 цикла шины. вход 18 занятости шины, группу 19 входов признака обращения к шине, вход 20 при- Ы знака записи и второй вход 21 признака чтения устройства. фь

Блок 1 оперативной памяти состоит из (Я мультиплексора 22 и блока 23 оперативной ф памяти.

Устройство работает следующим образом.

Цикл отладки состоит иэ этапов управления и трассировки. На этапе управления сигнал на входе 12 имеет уровень "0", Этот сигнал поступает в блок 1 и разрешает запись в блок 1 адреса, при появлении которо-. го на вторых адресных входах 15 устройства на этапе трассировки происходит прерывание выполнения программы в отлаживэе1737454 мом устройстве. и адресов, по которым разрешается занесение информации а блок Z оперативной памяти. Аналогично программируется второе устройство для отладки многопроцессорных систем. Оптимальный отладочный комплекс может включать несколько узлов трассировки — no числу процессоров в отлаживаемом устройстве, и несколько узлов контроля шины — no числу межпроцессорных магистралей е отлажиаземом устройстве. Затем управляющая

3ВМ запускает выполнение программ в отлзживаемом устройстве и выставляет сигнал уровня "1" н& входе 12 режимз устрОйства, что ОзначаВт переход K этапу трассировки.

На этапе трассировки сигнал на входе

17 имеет уровень "1" в течение времени, пока длится цикл Мины первого процессора отлзживаемого устройстве, и уровень "0" в течение остального времени, Если циклы .шины идут непрерывно один за другим, то на входа 17 присутствуют короткие импульсы уровня "0". По положительному перепаду (переходу из низкого уровня в высокий) сигнала на входе 17 и наличии сигнвлауровня "1" на входе разрешения счета первого счетчика 4 импульсов значение на выходе счетчика 4 импульсов уввличиваетея нв единицу, приеутствукнций на управляющем входе мультиплексора б сигнал уровня ".1" разрешает передачу информаций Йз выходы мультиплексоре 6 с его второй группы информационных входоа. Код иа выходе счетчика 4 импульсоа является адресом занесения информации в блок 2 оперативной памяти, информация заносится по отрицательно перепаду (переходу из высокого уровня в низкий) сигнала нв входе 17 с информационной и адресной магистралей первого процаесора отлаживаемого устройства и является трассой выполнения программы этим процессором.

На этапе трассировки коды е магистрали адреса первого процессора отлвживаемого устройства поступают также в блок 1 и сравниваются с записанным там адресом оетановз; при совпадении адресов нв первом выходе блока 1 появляетея импульс уровня "1", который устанавливает счетчик

4 импульсов в нулевое состояние, запрещая счет, и через элемент HE 13 поступает нв выход 14 прерывания устройства. Аналогично работают узлы трассировки осталь ных устрбйетв для отладки многопроцессорных, систем. Выходы прерываний устройств обьединены по схеме МОНТАЖНОЕ

Или, причем нагрузочное сопротивление расположено в управляющей ЭВМ. Импульс прерывания,: появившййся на выходе 14 прерывания устройства, поступает во все устройства для отладки многопроцессорных систем и запись информации в блок

2 оперативной памяти одновременно пре5 кращается во всех устройствах.

На этапе трассировки коды с магистрали адреса nepsoro процессора отлажиааемого устройства сравниваются в блоке 1 также е адресами трассировки; при еовпз10 дении адресов на втором выходе блока 1. появляется импульс уровня "1". который разрешает счет в счетчике 4 импульсов. При этом информация о цикле шины,- содержащем данный адрес, заносится в трассу.

16 При наличии на втором выходе блока 1 оперативной памяти сигнала уровня "0" все записи в блок 2 оперативной памяти производятся по одному и тому же адресу, затирая друг друга.

20 Узел контроля шины отслеживает пере. сылки по межпроцессорной магистрали. На этапе трассировки сигнал нв входе 18 занятости имеет уровень "1" в течение времени, пока длится цикл обмена по межпроцессор26 ной магистрали, и уровень "0" в течение остального времени. Если циклы идут непрерывно один за другим, что имеет место при интенсивном обмене npoqeccopoa с общими ресурсами и большом числе процес36 соров в отлеживземом устройстве, то на входе 18 занятости присутствуют короткие импульсы уровня "0". По положительному нерепшу сигнала на входе 18 значение на выходе счетчика 6 импульсоа увеличивается

35 иа единицу, присутствующий на управляющем входе веультиилекеорв 7 сигнал уровня

"1" разрывает передачу информации нв выxe@s мультиплексора 7 с его первой группы информационных входов. Код на выходе

40 счетчика Ь импульсов является адресом занесения информации а блок 3 оперативной памяти, информация заносится по отрицателью перепаду сигнала не входы 18 е выходов еифратора 8, Входы шиф48 ратора 8 образуют группу 19 входов признака обращения к еине и подключаются еоответственно к увравляющим входам буферных элементов процессорных модулей, активизация которых (входов)

50 обеспечивает доступ процессорного модуля нз межпроцессорную магистраль. Поскольку в каждый момент времени межпроцессорная магистраль предоставляется а распоряженив о ому процессору, только

И на Одном из вхЩ ОЭ шифратора 8 имеется сигнал активного уровня, преобразованный на выходе шифратора 8 в номер процессора, осуществляющего Обман по межпроцес. сорной магистрали с общими ресурсами, Предлагаемое устройство непригодно для

1737454 отладки устройств нетрадиционной архи тектуры, когда доступ на межпроцессорную магистраль могут получать одновременно несколько процессоров, например один пишет, а остальные прямо с магистрали 5 . считывают. Таким образом. в блоке 3 оперативной памяти фиксируется последователь- ность разделения межпроцессорной магистрали между процессорами отлаживаемого устройства. Подробная информация о 10 циклах межпроцессорного обмена (адрес обращения, пересылаемые данные) содержится в блоке 2 оперативной памяти узла трассировки устройства.

Реагируя на полученное прерывание на 15 выходе 14-устройства, управляющая ЭВМ . останавливает выполнение программ процессорами отлаживаемого устройства и. переходит к этапу управления, устанавливая на входе режима 12 сигнал уровня "0". При 20 этом на выходы мультиплексора 6 поступа- . . ют коды с его первой группы информационных входов, а на выходы мультиплексора 7— коды с его второй группы информационных входов. Управляющая 3ВМ. выставляя со- 25 ответствующие коды на первых адресных входах, может прочитать трассироеочную информацию из ббаоков 2 и 3 оперативной памяти, стробируя чтение сигналами признака чтения на входах 10 и 21 соответст- 30 венно. Цикл отладки завершен.

Таким образом, анализируя адресную часть трассировочной информации из узла трассировки устройства, можно выделить циклы обмена по межпроцессорной мегист- 35 реае, а на основе трэссировочиой информа-. ции из узлов контроля шины устройства можно установить, е каком именно порядке процессоры получали доступ на межпроцассорную магистраль. Если в отлаживеемом 40 устройстве — телько одна межпроцессорная магистраль, зта информация в блоке 3 оперативной памяти кэждрго устройства для отладки многопроцессорных систем является одинаковой. Предлагаемое устройство не 45 позволяет соотнести между собой все циклы каждого процессора, но это для задач отладки многопроцессорных систем и не требуется, акцент делается на циклы межпроцессорного обмена. 50

Блок 1 оперативной памяти работает следующим образом.

Нэ этапе управления сигнал нэ упрзвля" ющем входе мультиплексора 22 имеет уровень "О", разрешая прохождение кодов на 55 выход мультиплексора с его первой группы входов, зти коды являются адресами, по «оторым управляющая ЭВМ записывает в блок 23 оперативной памяти информацию, . сопровождая ее управляющим сигналом по входу 20 записи. В блок 23 оперативной памяти в младший разряд двухразрядных ячеек памяти записывается единица по адресу прекращения трассировки и ноль — по остальным адресам. 8 старший разряд ячеек памяти блока 23 оперативной памяти записывается единица по трассируемым адресам, и ноль — по остальным адресам.

На этапе трассировки сигнал нэ управляющем входе мультиплексора 22 принимает уровень "1" и на адресные входы блока 23 оперативнрй памяти поступают коды с вторых адресных входов блока 1. При появлении на этих адресных входах адреса, совпадающего с заданным в качестве условия прекращения трассировки, на первом выходе блока 23 оперативной памяти появляется сигнал уровня "1". На этапе трассировки адреса с вторых адресных входов блока 1 определяют моменты появления сигнала уровня "1" на втором выходе блока

23 оперативной памяти.

Формула изобретения

Устройство для запоминания трассы функционирования многопроцессорных систем, содержащее пс.рвый и второй блоки оперативной памяти, элемент НЕ, первый счетчик импульсое, первый мультиплексор. причем первея группа адресных входов устройства соединена с первой группой адресных входов первого блоке оперативной памяти и первой группой информационных входов первого мультиплексора, группа выходов которого сеединена с rpynnoA адресных входов второго блоке оперативной памяти, информационные выходы второго блока оперативной памяти через двунаправленную информационную магистраль соединены с группой информационных входов первого блока оперативной памяти и группой информационных входов-выходов устройства. первый выход первого блока оперативной памяти через элемент НЕ соединен с выходом запроса прерывания устройства; группа информационных выходов первого счетчика импульсов соединена с второй группой информационных входов первогомультиплексора.входустановкирежима устройства соединен с входом обращения первого блока оперативной памяти и управляющим входом nepaoro мультиплексора, первый вход признака чтения устройства соединен с входом чтения второго блока оперативной памяти, вторая группа адресных входов устройства — с второй группой адресных входов первого блока оперативной памяти.и с первой группой информационных входов второго блока опера1737454

Кощлажи3аачощ устройстВу

Фиг /

1$ (Составитель А. Сошкин

Редактор Л. Пчолинская Техред М,Моргентал Корректор А. Осауленко

Заказ 1892 Тираж Подписное

ВНИИПИ Государственного комитете по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35. Раушская наб.. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101 тивной памяти, группа информационных входов устройства — с второй группой информационных входов второго блока оперативной памяти, вход признака записи устройства — с входом записи первого блока 5 оперативной памяти, вход цикла шины устройства — с входом чтения первого блока оперативной памяти, о т л и ч а ю щ е е с я тем, что. с целью расширения области применения путем обеспечения увеличения 10 длины трассы межпроцессорных обменов, s него введены второй счетчик импульсов, второй мультиплексор, третий блок оперативной памяти, шифратор, причем вход занятости шины устройства соединен с 15 тактовым входом второго счетчика импульсов и входом записи третьего блока оперативной памяти, группа информационных выходов которого соединена с группой информационных входов-выходов устройства, 20 вход начальной установки второго счетчика импульсов связан с входом начальной установки первого счетчика импульсов и выходом элемента НЕ, второй выход первого

11

I rz

3 6 ф

Ю блока оперативной памяти связан с входом разрешения счета первого счетчика импульсов. вход цикла шины устройства — с тактовым входом первого счетчика импульсов и входом записи второго блока оперативной памяти, группа выходов второго счетчика импульсов — с первой группой информационных входов второго мультиплексора, группа выходов которого соединена с группой адресных входов третьего блока оперативной памяти, вторая группа информационных входов второго мультиплексора связана с первой группой адресных входов устройства, управляющий вход второго мультиплексора соединен с входом установки режима устройства, вход чтенивтретьего блока оперативной памяти соединен с вторым входом признака чтения устройства, rpynna входов признака обращения к шине устройства подключена к группе входов шифратора, группа выходов которого подключена к группе информационных входов третьего блока оперативной памяти.