Устройство для сопряжения магистралей

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике может быть использовано в многомашинных и многопроцессорных вычислительных системах, в частности, для организации доступа процессоров к общему ресурсу. Целью изобретения является повышение быстродействия и достоверности функционирования устройства за счет сокращения времени занятия общей магистрали до длительности управляющих сигналов и за счет исключения несанкционированного доступа процессоров к отдельным участкам адресного пространства при записи информации, осуществляемое введением дешифраторов зон записи. Цель достигается тем, что в устройство, содержащее генератор тактовых импульсов, два регистра адреса, два коммутатора магистрали , два компаратора адреса, две группы магистральных усилителей сигналов адреса и управления и два триггера, дополнительно введены три элемента И-НЕ, элемент ИЛИ, три элемента задержки и два дешифратора зон записи. 2 ил. fe

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 06 F 13/14

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

1() 4

1р с) К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4808762/24 (22) 02,04.90 (46) 30.05,92, Бюл, М 20 (71) Ростовский филиал Всесоюзного научно-исследовательского и проектно-конструкторского института средств автоматизации МПС СССР (72) В,С, Прищепа и В.В, Кольцов (53) 681.325(088.8) (56) Авторское свидетельство СССР

N 1012235, кл, G 06 F 13/00, 1982.

Авторское свидетел ьство СССР

N 1283781, кл. G 06 F 13/14, 1986. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ МАГИСТРАЛЕЙ (57) Изобретение относится к вычислительной технике может быть использовано в многомашинных и многопроцессорных вычислительных системах, в частности, для организации доступа процессоров к общему

Изобретение относится к области вычислительной техники и может быть использовано в многомашинных и мно гоп роцессорн ых вычислител ьных системах, в частности, для сопряжения процессоров с общими магистралями или общими областями оперативной памяти, Известно устройство для управления доступом к памяти от двух ЦВМ. Однако оно имеет сложную схему и сложный алгоритм работы, что снижает его быстродействие и надежность.

Известно устройство для обмена данными, содержащее блок связи с магистралью, включающий в себя регистры адреса, данных, элементы И, ИЛИ, два триггера, элементы задержки, компаратор адреса и генератор тактовых импульсов. Однако его!

Ы,», 1737460 А1 ресурсу. Целью изобретения является повышение быстродействия и достоверности функционирования устройства за счет сокращения времени занятия общей магистрали до длительности управляющих сигналов и за счет исключения несанкционированного доступа процессоров к отдельным участкам адресного пространства при записи информации, осуществляемое введением дешифраторов зон записи. Цель достигается тем, что в устройство, содержащее генератор тактовых импульсов, два регистра адреса, два коммутатора магистрали, два компаратора адреса, две группы магистральных усилителей сигналов адреса и управления и два триггера, дополнительно введены три элемента И-НЕ, элемент ИЛИ, три элемента задержки и два дешифратора зон записи. 2 ил. схема не позволяет получить максимальное быстродействие системы при обмене данными.

Наиболее близким к предложенному является устройство для сопряжения двух магистралей, содержащее два триггера, генератор импульсов, два регистра адреса, два дешифратора зоны (компараторы адреса), блок памяти, два коммутатора магистрали, две группы элементов И, а также элементы НЕ, И.

Однако его схема также не обладает достаточным быстродействием, так как цикл обращения к блоку памяти продолжается от начала установки адреса устройства ао его снятия в следующем цикле работы процессора, в то время как длительность управляющих сигналов записи или чтения, по

1737460 которым собственно и производится обмен информацией, составил не более одной четвертой части цикла работы процессора, Кроме того, при работе нескольких процессоров с общей областью памяти в ней существуют зоны, которые должны быть доступны для записи только строго определенному процессору, а для чтения — для всех, Поэтому для повышения надежности устройства желательно, чтобы оно имело возможность защиты заданных зон общей памяти от несанкционированного доступа других процессоров.

Целью изобретения является повышение быстродействия устройства и достоверности работы за счет сокращения времени занятия общей магистрали со стороны каждой из сопрягаемых и за счет исключения несанкционированного доступа процессоров к отдельным участкам адресного пространства при записи .информации, осуществляемое введением дешифраторов зон записи.

Указанная цель достигается тем, что в устройство для сопряжения двух магистралей, содержащем первый и второй регистры адреса, информационные входы которых соединены соответственно с первыми информационными входами-выходами первого и второго коммутаторов магистрали и информационно-адресными шинами первой и второй магистралей, первый и второй компараторы адреса, информационные входы которых подключены соответственно к входам трансляции адреса магистральных усилителей сигналов адреса и управления первой и второй групп и выходам первого и второго регистров адреса, синхровходы Которых соединены соответственно с шинами управления обменом первой и второй магистралей, генератор тактовых импульсов, первый и второй триггеры, информационные входы которых соединены соответственно с выходами первого и второго компараторов адреса, а инверсные выходы — соответственно с входами сброса второго и первого триггеров и входами выборки магистральных усилителей сигналов адреса и управления первой и второй групп, первые выходы которых объединены и образуют шины адреса и управления общей магистрали, дополнительно введены два дешифратора зон записи, три элемента И вЂ” НЕ, элемент

ИЛИ и три элемента задержки, причем информационные входы и выходы первого и второго дешифраторов зон записи соединены соответственно с выходами первого и второго регистров адреса и первыми стробирующими входами первого и второго компараторов адреса, вторые стробирующие

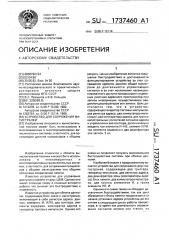

На фиг. 1 представлена функциональная схема устройства для сопряжения магистралей; на фиг. 2 — временные диаграммы, поясняющие его работу, 40 Устройство содержит (фиг, 1) первые и вторые 1 и 1 коммутаторы магистралей, ре1 гистры 2 и 2 адреса, группы 3 и 3 магист1 1 ральных усилителей сигналов адреса и управления, компараторы 4 и 4 адреса, де1

45 шифраторы 5 и 5 зон записи, элементы

И вЂ” НЕ 6 и 6, элементы 7 и 7 задержки, 1 1 триггеры 8 и 8; третий элемент И вЂ” НЕ 9, 1, элемент ИЛИ 10, третий элемент 11 задержки, генератор 12 тактовых импульсов, ши50 ны общей магистрали: 13 информационные, 14 — сигнала ответ, 15— адресные, шины первой и второй магистралей: 16 и 16 — информационно-адресные, 17 1 и 17" — сигнала "Ответ", 18 и 18 — сигнала

55 "Обмен" для записи адреса в регистр, 19 и

19 — сигнала чтения, 20 и 20 — сигнала

1 1 записи. Информационные входы регистров адреса 2 и 2 соединены соответственно с

1 информационно-адресными шинами пер10

35 входы которых соединены соответственно с шинами чтения первой и второй магистралей и входами направления обмена первого и второго коммутаторов магистрали, входами выборки подключенных соответственно к выходам первого и второго элементов И—

НЕ, первые входы которых соединены соответственно с выходами первого и второго компараторов адреса и входами трансляции запроса доступа магистральных усилителей сигналов адреса и управления первой и второй групп, вторые выходы которых подключены соответственно к шинам ответа первой и второй магистралей, а входы трансляции сигнала записи соответственно соединены с шинами записи первой и второй магистралей и входами стробирования первого и второго дешифраторов зон записи, выход генератора тактовых импульсов соединен с первыми входами третьего элемента И вЂ” НЕ и элемента ИЛИ, выходами подключенных соответственно к синхровходам первого и второго триггеров, а вторыми входами соответственно через первый и второй элементы задержки с инверсным выходом второго триггера и прямым выходом первого триггера, вторые входы первого и второго элементов И вЂ” НЕ соединены соответственно с прямыми выходами первого и второго триггеров, стробирующий вход генератора тактовых импульсов соединен с шиной ответа общей магистрали и через третий элемент задержки с входами трансляции ответа магистральных усилителей сигналов адреса и управления первой и второй групп.

1737460 вой 16 и второй 16 магистралей выходы— с входами первого 4 и второго 4 компара1 торов адреса и входами трансляции адреса первой 3 и второй 3 групп магистральных усилителей сигналов адреса и управления, а первые выходы последних объединены и образуют шины 15 адреса и управления общей магистрали. Входы — выходы первых 1 и вторых 11 коммутаторов магистралей включены соответственно между информационно-адресными шинами первой 16 и второй

16 и информационными шинами 13 общей

1 магистралей, а входы неаправления коммутации соединены с управляющим сигналом, например, "Чтение" 19 и 19 собственной магистрали. Информационные входы триггерое 8 и 8 подключены к выходам соответ1 ствующего компаратора 4 и 4 адреса, а инверсные выходы триггеров 8 и 8 подклю1 чены к входам сброса друг друга и входам выборки соответствующих магистральных усилителей 3 и 3 . Входы дешифраторов 5 и

5 зоны записи соединены с соответствую1 щими входами регистров 2 и 2 адреса и с шиной 20 (20 ) сигнала записи своей магист1 рали, а выходы соединены с одним из входов стробирования компаратора адреса своей магистрали, второй вход стробирования которых подключен к шине 19 (19 ) сиг1 нала чтения, а выходы дополнительно соединены с входом трансляции запроса доступа к общей магистрали своей группы магистральных усилителей и первыми входами первого 6 и второго 6 элементов И—

НЕ, вторые входы которых подключены к прямым выходам соответственно первого 8 и второго 81 триггеров, а выходы соединены с входами выборки первого 1 и второго 1 коммутаторов магистралей, Вход стробирования генератора 12 тактовых. импульсов подключен к шине 14 сигнала "Ответ" общей магистрали, выход — к первым входам третьего элемента И вЂ” НЕ и элемента 10

ИЛИ, вторые входы которых через первый 7 и второй 7 элементы задержки соединены соответственно с инверсным выходом второго 8 и прямым выходом первого 8тригге-, 1 ров. Шина 14 сигнала "Ответ" через третий элемент 11 задержки соединена с входами трансляции ответа обеих групп 3 и 3 маги1 стральных усилителей, соответствующие вторые выходы которых подключены к.шинам сигнала "Ответ" 17 и 17 своих магистралей.

Коммутаторы магистралей могут быть выполнены на двунаправленных шинных формирователях, например К555АП6. Группы магистральных усилителей эквивалентны группам элементов И в прототипе и могут быть выполнены на магистральных приемопередатчиках К555АП5. В общую магистраль может быть передан только один управляющий сигнал, например "Запись", при этом информацию о наличии второго несет в себе сигнал запроса доступа к общей магистрали, транслируемый с выхода компаратора адреса. Компараторы адреса, называемые в прототипе дешифраторами зоны, могут быть выполнены на схемах сравнения К555СА1, на которые подаются стар5

10 шие разряды адреса, сравниваемые с кодом перемычек на одноименных разрядах, при этом в качестве входов стробирования может быть использована свободная пара одноименных разрядов, на которую подаются

15 взаимоинверсные управляющие сигналы (" Чтение и запись", прошедший через дешифратор зоны записи). При отсутствии входа стробирования у генератора тактовых импульсов его времязадающая цепь может

20 быть соединена с шиной сигнала "Ответ" через диод, направление включения которого зависит от логического уровня активного состояния шины

Устройство работает следующим обра25 зом.

Во время функционирования обоих внешних устройств (процессоров) в регистры 2 и 2 заносятся коды адресов по фрон1

30 там сигналов "Обмен" на шинах 18 и 18" с каждым появлением в магистралях адресных кодов, При появлении адреса, совпадающего с зоной адресов общей магистрали в адресном пространстве, .например первой

35 магистрали, компаратор 4 адреса подготавливается, а с приходом одного из управляющих сигналов "Чтение" или "Запись" выдает сигнал запроса доступа к общей магистрали, который задерживается на его выходе до снятия управляющего сигнала. Сигнал "За40 пись" прежде чем поступить на вход компаратора адреса, должен пройти. через дешифратор 5 зоны записи, который дешифрирует адреса входящие уже в адресное пространство общей магистрали. Причем и первая и вторая магистраль обычно должны иметь или частично перекрывающиеся зоны для записи или отдельные общие участки

45 для организации, например, программного обмена информацией по системе "флажков".

Таким образом, если все условия соблю50 фронту очередного импульса генератора 12 тактовых импульсов, прошедшего через элемент И вЂ” НЕ 9. При срабатывании триггера 8 на вход сброса триггера 8" поступает сигнал блокирующего сброса, при наличии дены, то сигнал запроса доступа к общей магистрали поступает на информационный

55 вход триггера 8, который срабатывает по

1737460 которого триггер 81 не может срабатывать по синхровходу. Сигнал разрешения доступа к магистрали с выходов триггера 8 поступают также на вход выборки первой группы магистральных усилителей 3 и через эле- 5 мент И-НЕ 6 на вход выборки первого коммутатора 1 магистрали. Сигналы адреса, управления и запроса доступа с выхода магистральных усилителей 3 поступают в общую магистраль. Устройство памяти, 1 находящееся на общей магистрали, получив сигнал запроса доступа выдает или принимает данные с коммутатора 1 и формирует сигнал "Ответ" на шине 14, которые блокирует генератор 12 и, пройдя через элемент 1

11 задержки и один из магистральных усилителей 3, поступает на шину 17 первой магистрали.

Внешнее устройство — процессор, восприняв сигнал "Ответ", снимает сигнал уп- 2 равления (запись или чтение), на выходе компаратора 4 снимается сигнал запроса доступа к магистрали, который в свою очередь снимается через элемент И вЂ” НЕ 6 с входа выборки коммутатора 1 и с выхода 2 магистральных усилителей 3. Устройство памяти на общей магистрали снимает сигнал "Ответ", разблокируется генератор 12 и первый его импульс, пройдя через элемент

И вЂ” Н Е 9, сбрасывает триггер 8, так как íà его информационном входе уже снят сигнал запроса. Процесс передачи информации первой магистрали заканчивается, но вторая магистраль еще не может быть подключена . к общей, так как элемент ИЛИ 10 (его можно интерпретировать как элемент И для отрицательной логики) заблокирован сигналом элемента 7 задержки. Это необходимо для окончания переходных процессов на общей магистрали.

После окончания интервала задержки импульс генератора 12 проходит через элемент ИЛИ 10 на синхровход триггера 8 и, если на его информационном входе сформирован сигнал запроса, происходит аналогичный процесс обмена информацией между второй и общей магистралями, Одновременное срабатывание триггеров 8 и 8 исключено, так как сигналы на их синхровходах взаимно инверсны.

Связь шины сигнала ответ с генератором тактовых имульсов и как результат задержка переключения триггера в пассивное состояние после снятия управляющих сигналов служит для кратковременного удержания сигналов адреса на общей магистрали с целью исключения нежелательных переходных процессов в случае одновременного снятия сигналов управления и адреса, Временные диаграммы на фиг. 2 поясняют работу устройства, где цифры слева от диаграммы указывают номер шины или номер элемента (фиг. 1), на выходе которого действует данный сигнал, Предлагаемое устройство предназначено для сопряжения магистралей с совмещенной шиной адреса и данных, при сопряжении магистралей с разделенными

0 шинами адреса и данных регистры 2 и 2 могут быть исключены из схемы, В отличие от прототипа в устройстве результатом сопряжения выбрана общая магистраль, что дает возможность расшире5 ния системы при каскадном соединении устройств, когда полученная общая магистраль сопрягается еще с одной магистралью и т.д.

Формула изобретения

0 Устройство для сопряжения магистралей, содержащее первый и второй регистры адреса, информационные входы которых соединены соответственно с первыми информационными входами-выходами первого и

5 второго коммутаторов магистрали и информационно-адресными шинами первой и второй магистралей, первый и второй компараторы адреса, информационные входы которых подключены соответственно к

30 первым информационным входам магистральных усилителей сигналов адреса и управления первой и второй групп и выходам первого и второго регистров адреса, синхровходы которых соединены соответствен35 но с шинами управления обменом первой и второй магистралей, генератор тактовых импульсов, первый и второй триггеры, информационные входы которых соединены соответственно с выходами первого и вто40 рого компараторов адреса, а инверсные выходы — соответственно с входами сброса второго и первого триггеров и входами выборки магистральных усилителей сигналов адреса и управления первой и второй групп, 45 первые выходы которых обьединены и образуют шины адреса и управления общей магистрали, причем вторые информационные входы-выходы первого и второго коммутаторов обьединены и образуют информацион50 но-адресные шины общей магистрали, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия и достоверности работы устройства, в него введены два дешифратора зон записи, три элемента И55 НЕ, элемент ИЛИ и три элемента задержки, причем информационные входы и выходы первого и второго дешифраторов зон записи соединены соответственно с выходами первого и второго регистров адреса и первыми стробирующими входами первого и

1737460

10 второго компараторов адреса, вторые стробирующие входы которых соединены соответственно с шинами чтения первой и второй магистралей и входами направления обмена первого и второго коммутаторов магистрали, входами выборки подключенных соответственно к выходам первого и второго элементов И вЂ” НЕ, первые входы которых соединены соответственно с выходами первого и второго компараторов адреса и входами запроса доступа магистральных усилителей сигналов адреса и управления первой и второй групп, вторые выходы которых подключены соответственно к шинам ответа первой и второй магистралей, а синхронизирующие входы соответственно соединены с шинами записи первой и второй магистралей и синхровходами первого и второго дешифраторов зон записи, выход генератора тактовых импульсов соединен с первыми входами третьего элемента И-НЕ и элемента ИЛИ, выходами подключенных соответственно с синхровходами первого и

5 второго триггеров, а вторыми входами соответственно через первый и второй элемент задержки — с инверсным выходом второго триггера и прямым выходом первого триггера, вторые входы первого и второго элемен10 тов И вЂ” НЕ соединены соответственно с прямыми выходами первого и второго триггеров, стробирующий вход генератора тактовых импульсов соединен с шиной ответа общей магистрали и через третий элемент

15 задержки — с вторыми информационными входами магистральных усилителей сигналов адреса и управления первой и второй групп.

17374б0

12

19 фиг. 2

Составитель В, Прищепа

Редактор О. Спесивых Техред M.Ìîðãåíòàë Корректор Т. Малец

Заказ 1893 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101