Устройство для приема и передачи информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматизированных систем управления, в частности к устройствам для приема и передачи информации. Цель изобретения состоит в повышении достоверности передачи и приема команд. Устройство содержит два блока памяти, два реверсивных счетчика, регистр, триггер, дешифратор, блок ввода команд, пять элементов задержки, элемент ИЛИ, три элемента И, элемент НЕ, два блока элементов И и блок элементов ИЛИ, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)з G 08 С 19/28

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4801226/24 (22) 12,03,90 (46) 30.05,92. Бюл. М 20 (71) Всесоюзный научно-исследовательский институт проблем вычислительной техники и информатики (72) И.А,Данильченко, Е.С,Бичугов, А,Н.Романов и Н,В,Ромшин (53) 621.398(088.8) (56) Авторское свидетельство СССР

N 1587501, кл, G 08 С 19/28, 1988.

Изобретение относится к автоматизированным системам управления, в частности к устройствам для приема и передачи информации территориально-распределенным объектам. и может быть использовано в сложной АСУ, Цель изобретения — повышение достоверности передачи и приема команд.

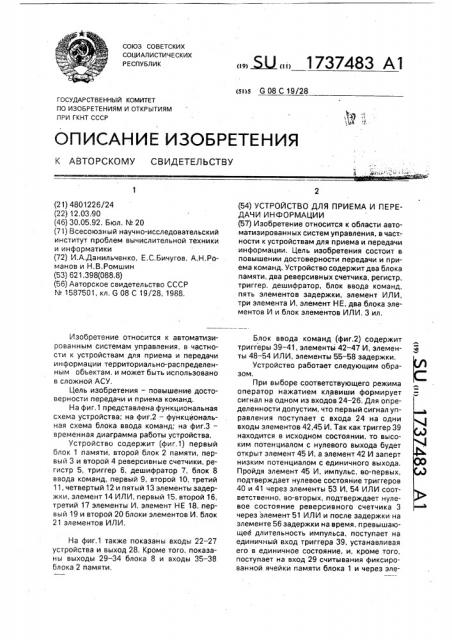

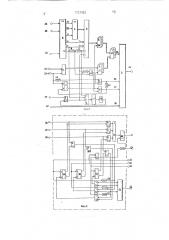

На фиг,1 представлена функциональная схема устройства; на фиг,2 — функциональная схема блока ввода команд; на фиг.3— временная диаграмма работы устройства.

Устройство содержит (фиг,1) первый блок 1 памяти, второй блок 2 памяти, первый 3 и второй 4 реверсивные счетчики, регистр 5, триггер 6, дешифратор 7. блок 8 ввода команд, первый 9, второй 10, третий

11, четвертый 12 и пятый 13 элементы задержки, элемент 14 ИЛИ, первый 15, второй 16, третий 17 элементы И, элемент НЕ 18, первый 19 и второй 20 блоки элементов И. блок

21 элементов ИЛИ.

На фиг.1 также показаны входы 22-27 устройства и выход 28. Кроме того, показаны выходы 29 — 34 блока 8 и входы 35 — 38 блока 2 памяти, Ы(> 1737483 А1 (54) УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ ИНФОРМАЦИИ (57) Изобретение относится к области автоматизированных систем управления, в частности к устройствам для приема и передачи информации. Цель изобретения состоит в повышении достоверности передачи и приема команд. Устройство содержитдва блока памяти, два реверсивных счетчика, регистр, триггер, дешифратор, блок ввода команд, пять элементов задержки, элемент ИЛИ, три элемента И, элемент НЕ, два блока элементов И и блок элементов ИЛИ, 3 ил.

Блок ввода команд (фиг.2) содержит триггеры 39 — 41, элементы 42 — 47 И, элементы 48 — 54 ИЛИ, элементы 55-58 задержки, Устройство работает следующим образом, При выборе соответствующего режима оператор нажатием клавиши формирует сигнал на одном из входов 24-26. Для определенности допустим, что первый сигнал управления поступает с входа 24 на одни входы элементов 42,45 И. Так как триггер 39 находится в исходном состоянии, то высоким потенциалом с нулевого выхода будет открыт элемент 45 И, а элемент 42 И заперт низким потенциалом с единичного выхода.

Пройдя элемент 45 И, импульс, во-первых, подтверждает нулевое состояние триггеров

40 и 41 через элементы 53 И, 54 ИЛИ соответственно, во-вторых, подтверждает нулевое состояние реверсивного счетчика 3 через элемент 51 ИЛИ и после задержки на элементе 56 задержки на время, превышающее длительность импульса, поступает на единичный вход триггера 39, устанавливая его в единичное состояние, и, кроме того, поступает на вход 29 считывания фиксированной ячейки памяти блока 1 и через эле1737483

10

20

30

50 менты 50, 49 ИЛИ на вход элемента 9 задержки..

Содержимое фиксированной ячейки памяти из блока 1 записывается в реверсивный счетчик 3 по импульсу, поступающему на синхровход реверсивного счетчика с выхода 32 блока 8, где импульс считывания был задержан на время опроса содержимого фиксированной ячейки элементом 55 задержки.

Поскольку в исходном состоянии триггер 6 на инверсном выходе дает высокий потенциал, то через открытые этим потенциалом элементь. 19 И и 21 ИЛИ код адреса со счетчика 3 поступает на адресный вход блока 2 памяти, После задержки на время переходных процессов в реверсивном счетчике 3 импульс с выхода элемента 9 задержки через элементы 14 ИЛИ и 16 И, также открытым высоким потенциалом с инверсного выхода триггера 6, поступает на вход считывания блока 3 памяти и первая команда кортежа выдается объектам управления, После выдачи первой команды на выход

28 импульс с выхода элемента 10 задержки поступает на суммирующий входы реверсивных счетчиков 3 и 4, увеличивая их содержимое на единицу и тем самым подготавливая адрес следующей ячейки на входе блока 2.

При поступлении следующего сигнала с того же входа 24 на входы элементов 42,45

И будет открыт элемент 42 И высоким потенциалом единичного выхода триггера 39, а элемент 45 И будет закрыт.

Теперь импульс с входа.24, пройдя элемент 42 И и элементы 48,49 ИЛИ, поступает на вход элемента 9 задержки и через элементы 14 ИЛ И и 16 И считывает содержимое очередной ячейки блока 2 на выход 28 и т,д, Если же очередной входной сигнал поступит с другого входа, например 25, -o через открытый высоким потенциалом элемент 46 И он сбросит в исходное состояние реверсивные счетчики 3,4 и затем через элемент 57 задержки поступит на вход считывания другой фиксированной ячейки памяти блока 1, считывая адрес описанным выше образом.

Необходимость реверсивного счетчика

4, дешифратора 7, элемента 17 И и элемента

НЕ 18 обусловлена тем, что при необходимости lloBTopHoA выдачи той же команды оператор может повторно выдать объектам управления. Для этого после выдачи очередной команды на вход 27 подается импульс повторной выдачи, который поступает на один вход элемента 17 И, на другой вход которого подается сигнал с элемента НЕ 18.

Если реверсивный счетчик 4 уже зафиксировал факт выдачи команды на выход 28, то дешифратор 7 на своем выходе будет иметь низкий потенциал, Как только реверсивный счетчик 4 будет обнулен, то дешифратор 7 зафиксирует этот факт выдачей высокого потенциала на вход элемента НЕ

18, а последний закроет элемент 17 И, блокируя процесс повторной выдачи команд.

Таким образом, после передачи определенного числа команд из кортежа в реверсивном счетчике 4 будет зафиксировано это число, дешифратор 7 зафиксирует это обстоятельство низким потенциалом на своем выходе, а элемент НЕ 18 высоким потенциалом стирает элемент 17 И по второму входу, Импульс повторной выдачи данных с входа 27 проходит через элемент 17 И и поступает на вычитающие входы реверсивных счетчиков

3,4, уменьшая их содержимое на единицу, Кроме того, этот же импульс после задержки на элементе 11 на время срабатывания реверсивных счетчиков 3,4 через элементы 14

ИЛИ и 16 И поступает на вход считывания блока 2.

Оператор осуществляет выдачу каждой последующей команды кортежа только после получения подтверждения о приеме очередной команды всеми объектами управления.

Если какой-то из объектов управления не получит команду управления, то при отсутствии подтверждения от него за установленный интервал времени оператор повторяет выдачу последней команды управления.

С этой целью импульс синхронизации, поступающий на вход 23 — 2 для занесения кода адреса в регистр 5 с входа 23 — 1, сразу подается на единичный вход триггера 6 и устанавливает его в единичное состояние, при котором высоким потенциалом с единичного выхода будут открыты элементы 20

И и низким потенциалом с нулевого выхода закрыты элементы 19 И и элемент 16 И, запрещающий прохождение импульсов считывания с выхода элемента 14 ИЛИ.

В результате этого код адреса с выхода регистра 5 через элементы 20 И и 21 ИЛИ поступает на адресный вход блока 2 памяти, а импульс синхронизации, задержанный элементом 12 на время установки адреса, поступает на вход записи блока 2 как импульс записи.

Все подтверждения от объектов таким же образом заносятся по тем адресам, которые указывает источник информации.

Как только запись входного сообщения будет окончена, импульс с выхода элемента

13 задержки поступает на вход сброс триг1737483

50

55 гера 6, по которому последний сбрасывается в исходное состояние, отключая от адресного входа блока 2 памяти регистр 5 и подключая к нему реверсивный счетчик 3, Таким образом, введенные узлы и блоки позволяют существенно повысить надежность устройства по выдаче команд управления.

Формула изобретения

Устройство для приема и передачи информации, содержащее блок ввода команд, входы которого являются задающими входами устройства, выходы группы блока ввода команд подключены к входам первого блока памяти, первый выход блока ввода команд подключен к входу первого элемента задержки, выход которого подключен к входу второго элемента задержки, первый элемент И, выход которого подключен к синхровходу второго блока памяти, выходы которого являются выходами устройства, первый реверсивный счетчик, регистр и элемент ИЛИ, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности передачи и приема команд, в него введены первый и второй блоки элементов И, блок элементов ИЛИ, третий, четвертый и пятый элементы задержки, триггер, второй и третий элементы И, второй реверсивный счетчик, дешифратор и элемент НЕ, выходы первого блока памяти подключены к информационным входам первого реверсивного счетчика, второй выход блока ввода команд подключен к синхровходу первого реверсивного счетчика, выходы которого подключены к входам группы первого блока элементов И, выходы которого подключены к входам группы первого блока элементов ИЛИ, третий выход блока ввода команд подключен к входам

"Сброс" первого и второго реверсивных счетчиков, выход первого элемента задержки подключен к первому входу элемента

ИЛИ, выход которого подключен к первому входу второго элемента И, выход которого

5 подключен к входу "Считывание" второго блока памяти, выходы второго оевеосивного счетчика подключены к входам дешифратора, выход которого через элемент НЕ подключен к первому входу третьего эле10 мента И, выход которого, входы обратного счета первого и второго реверсивных счетчиков объединены и через третий элемент задержки подключены к второму входу элемента ИЛИ, выход второго элемента задер15 жки подключен к входам прямого счета первого и второго реверсивных счетчиков, входы группы регистра являются адресными входами устройства, вход регистра, вход четвертого элемента задержки и вход "Уста20 новка" триггера объединены и являются синхровходом устройства, выход четвертого элемента задержки подключен к первому входу первого элемента И, выход которого подключен к синхровходу второго блока па25 мяти и через пятый элемент задержки — к входу "Сброс" триггера, прямой выход которого подключен к входу второго блока элементов И и к второму входу первого элемента И, инверсный выход триггера под30 ключен к входу первого блока элементов И и к второму входу второго элемента И, выходы регистра подключены, к входам группы второго блока элементов И, выходы которого подключены к входам второй группы бло35 ка элементов ИЛ И, выходы которого подключены к адресным входам второго блока памяти, информационные входы которого являются информационными входами устройства, второй вход третьего элемента

40 И является входом инициализации повторной передачи команды устройства.

1737483

7/

1737483

Q Q О О O D

Составитель И. Кузнецов

Техред M.Mîðãåíòàë Корректор О, Кундрик

Редактор А. Долинич

Заказ 1894 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101

L A