Устройство для управления автономным инвертором

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике . Цель изобретения - повышение качества работы на низких частотах и расширение области использования. Устройство управления автономным инвертором содержит измеритель 1 амплитуды, интегратор 2, компараторы 3, 4, источник 5 уставок, распределитель 6, измеритель 7 фазовой ошибки, делитель 8, логический блок 9. 1 з.п. ф-лы, 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛ ИСТИЧ Е С К ИХ

РЕСПУБЛИК (51)5 Н 02 М 7/48

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР . 1"

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ4ЕТЕЛЬСТВУ (21) 4677799/07 (22) 11,04.89 (46) 30,05.92. Бюл. Мз 20 (71) Научно-исследовательский электротехнический институт Производственного объединения "ХЭМЗ" (72) М.А. Гинзбург, Б.Е. Калашников и И.И.Энштейн (53) 621.316.727(088.8) (56) Авторское свидетельство СССР

N 1023625, кл. Н 02 М 7/48, 1981.

Kaimobo V., Mashii M, Pervormauce

Impraement of cearent Souru Iniertar-Fed

Induction motor Dviies — IEEF Transartionson

Industry Applications, 1982 ИА-18, М 6, р.

703-710.

„„. Ж „„1737675 А1 (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ АВТОНОМНЫМ ИНВЕРТОРОМ (57) Изобретение относится к электротехнике. Цель изобретения — повышение качества работы на низких частотах и расширение области использования. Устройство управления автономным инвертором содержит измеритель 1 амплитуды, интегратор 2, компараторы 3, 4, источник 5 уставок, распределитель 6, измеритель 7 фазовой ошибки, делитель 8, логический блок 9. 1 з,п. ф-лы, 4 ил.

1737675

15

25

40

50

Изобретение относится к электротехнике, а именно к преобразователям частоты на основе автономных инверторов тока и напряжения, и может быть использовано при создании аси нхрон н ых частотно-регулируемых электроприводов различного назначения.

Известно устройство для управления трехфазным автономным инвертором, обеспечивающее широтно-импульсную модуляцию (ШИМ) выходного напряжения с целью расширения диапазона регулирования и уменьшения пульсаций частоты вращения и риводного электродвигателя. Устройство содержит задающий генератор, многоступенчатый делитель частоты, кольцевую пересчетную схему, узел формирования несущего сигнала, узел выделения интервалов коммутации и дешифратор, и осуществляет в функции дискретных значений выходной частоты дискретное изменение числа дополнительных коммутаций в инверторе.

Недостатком данного устройства является то, что по мере снижения частоты для поддержания качественной формы выходного сигнала (напряжения, тока) необходимо нара щи вать объем а и и аратуры управления и в пределе, при очень низких частотах устройство технически нереализуемо.

Наиболее близким к предлагаемому является устройство для управления мостовым инвертором со слежением за кривой выходного напряжения, содержащее измеритель амплитуды, интегратор, два компаратора, первыми входами соединенные с выходом интегратора, а вторыми — с источником противоположных по знаку уставок, распределитель импульсов, В устройстве измеряется амплитудное рассогласование задающего и выходного сигналов инвертора, а выделенный сигнал ошибки через интегратор и компараторы управляет работой распределителя импульсов, Недостатком прототипа является то, что устройство предназначено для управления только однофазным инвертором, учитывает лишь амплитудное рассогласование сигналов и не учитывает фазовую ошибку, в результате чего не обеспечивает качественную работу инвертора и электродвигательной нагрузки в области низких частот, Цель изобретения — повышение качества работы инвертора на низких частотах и расширение области применения.

Поставленная цель достигается тем, что в устройство для управления автономным инвертором, содержащее измеритель амплитуды, интегратор, два компаратора, первыми входами соединенные с выходом интегратора, а вторыми — с источником противоположных по знаку уставок, распределитель импульсов, введены измеритель фазовой ошибки входного параметра, делитель входных сигналов и логический блок, реализующий функцию d = (а c)v(bhc), где а, b. c — входные, à d — выходная функция, причем распределитель импульсов выполнен в виде трехфазного пересчетного кольца, делитель двумя входами соединен с выходами измерителя амплитуды и измерителя фазовой ошибки, выходом соединен с входом интегратора, выход d логического блока связан со своим входом С через два последовательно соединенные элемента задержки и с синхронизирующим входом пересчетного кольца, двумя входами а и Ь вЂ” с соответствующими входами направления сдвига пересчетного кольца и с выходом компараторов, при выход пересчетного кольца соединен с входом сравнения измерителя фазовой ошибки.

Кроме того, измеритель фазовой ошибки выполнен в виде суммирующего операционного усилителя, вход которого подключен через управляемые ключи к входу сравнения измерителя фазовой ошибки, причем управляющие входы ключей соединены с теми выходами пересчетного кольца, на которых формируются сигналы соседних по отношению к измеряемой, фаз.

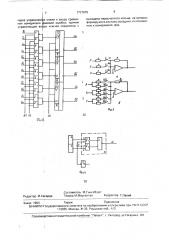

На фиг. 1 изображено устройство для управления автономным инвертором; на фиг. 2 — схема пересчетного кольца; на фиг, 3 — измеритель фазовой ошибки; на фиг. 4 — схема логического блока, На вход устройства (фиг, 1), представленный соединенными входами измерителя

1 амплитуды и измерителя 7 фазовой ошибки, подается трехфазный задающий сигнал, определяющий амплитуду, частоту и фазу тока (напряжения) на выходе автономного инвертора. На второй вход измерителя 7 фазовой ошибки подается выходной сигнал трехфазного пересчетного кольца 6, который в зоне малых частот с большой степенью точности воспроизводит реальный выходной сигнал — ток (напряжение) автономного инвертора. На выходе измерителя

7 фазовой ошибки формируется сигнал, пропорциональный амплитуде входного задающего сигнала и углу сдвига по фазе между задающим сигналом и выходным сигналом пересчетного кольца 6, т,е. током (напряжением) на выходе автономного инвертора.

Выходы измерителя 1 амплитуды и измерителя 7 фазовой ошибки подключены к входам делителя 8, который выполняет автоматическую операцию деления, исклю1737675

25

55 чает влияние амплитуды задающего сигнала на сигнал фазовой ошибки. Выход делителя 8 соединен с входом интегратора 2, в котором сигнал фазовой ошибки интегрируется. Выход интегратора 2 соединен с первыми входами двух компараторов 3 и 4, вторые входы которых соединены с источником 5 противоположных по знаку уставок;

Один из компараторов 3 или 4 переключается при равенстве выходного сигнала интегратора 2 сигналу положительной уставки источника 5, другой — отрицательной уставки источника 5, Выходы компараторов 3 и 4 соединены с входами направления сдвига

ВП и НЗ пересчетного кольца 6, а также с входами а и Ь логического блока 9, выход которого соединен с синхронизирующим входом пересчетного кольца, Кроме того, выход логического блока 9 через два последовательно включенных элемента 10 и 11 задержки соединен со своим третьим входом с.

Измеритель 1 амплитуды трехфазного сигнала, интегратор 2, компараторы 3 и 4, источник 5, делитель 8 и элементы 10 и 11 задержки известны.

На фиг. 2 показана одна из возможных схем трехфазного реверсивного пересчетного кольца 6, выполненного на J-К триггерах и логических элементах И-НЕ.

На фиг, 3 показаны варианты схемы измерителя 7 фазовой ошибки; а — для инвертора тока; б — для инвертора напряжения, Различие схем измерителя для разных типов инверторов обусловлено наличием фазового сдвига между сигналом пересчетного кольца и выходным током у инвертора тока (одновременно проводят 2 вентильных плеча) и его отсутствием между сигналом пересчетного кольца и выходным напряжением у инвертора напряжения (одновременно проводят 3 вентильных плеча), Измеритель 7 фазовой ошибки (фиг. 3) содержит суммирующий операционный усилитель, на вход которого через управляемые ключи подается трехфазный задающий сигнал, а на управляющие входы ключей подаются выходные сигналы пересчетного кольца, На фиг. 3 показаны соотношение величин резисторов схемы и взаимная фазировка входных и управляющих сигналов, нарушать которые не следует, Схема логического блок» 9 (фиг. 4) содержит 3 логических элемента 2И-НЕ и реализует логическую функцию

d = (а лс)ч(Ьлс).

Для реализации ШИМ вЂ” управление автономным инвертором в области низких частот предлагаемое устройство с помощью измерителей 1, 7, делителя 8, интегратора 2 выделяет величину фазовой ошибки задающего и выходного сигналов, а с помощью компараторов 3 и 4, источника 5 и логического блока 9 преобразует сигнал ошибки в импульсные сигналы управления пересчетным кольцом 6. При равенстве сигнала ошибки величине каждой из уставок источника 5 на выходе блока 9 формируется синхронизирующий сигнал, осуществляющий переключение пересчетного кольца 6. Знаком ошибки обусловлено переключение компаратора 3 либо 4, а следовательно, направление сдвига пересчетного кольца при переключении, которое, в,свою очередь, определяет порядок переключения вентилей автономного инвертора и форму кривой его выходного сигнала (тока или напряжения), Элементы 10 и 11 задержки, соединяющие выход и вход блока 9, ограничивает допустимую с точки зрения коммутационных процессов минимальную длительность межкоммутационного интервала.

Формула изобретения

1. Устройство для управления автономным инвертором, содержащее измеритель амплитуды выходного .параметра инвертора, интегратор, два компаратора, первыми входами соединенные с выходом интегратора, а вторыми — с источником противоположных по знаку уставок, распределитель импульсов, отл и ч а ю щ ее с я тем, что, с целью повышения качества работы на низких частотах и расширения области использования, введены измеритель фазовой ошибки входного параметра, делитель входных сигналов, два элемента задержки и логический блок, реализующий функцию d =

= (anc)v(bee), где а, Ь, с — входные, à d— выходная функция, причем распределитель импульсов выполнен в виде трехфазного пересчетного кольца, делитель двумя входами соединен с выходами измерителя амплитуды и измерителя фазовой ошибки, выходом соединен с входом интегратора, d-выход логического блока связан со своим с-входом через два последовательно. соединенных элемента задержки и с синхронизирующим входом пересчетного кольца, двумя а и b входами с соответствующими входами направления сдвига пересчетного кольца и с выходами компараторов, при этом выход пересчетного кольца соединен с входами сравнения измерителя фазовой ошибки

2. Устройство по и., о т л и ч а ю щ е е— с я тем, что измеритель фазовой ошибки выполнен в виде суммирующего операционного усилителя, вход которого подключен

1737675

an нь

Составитель M.Ãèêçáóðã

Редактор И. Касарда Техред M.Моргентап КоРРектоР Т,Палий

Заказ 1904 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб.. 4/5

Производственно-издательский комбинат "Патент", r, Ужгород, ул,Гагарина, 101 через управляем1е ключи к входу сравнения измерителя фазовой ошибки, причем управляющие входы ключей соединены с выходами пересчетного кольца, на которых формируются сигналы соседних, по отношению к измеряемой, фаз.