Устройство для умножения с контролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств универсальных и специализирован- - ных ЭВМ для умножения нормализованных чисел. Цель изобретения - расширение функциональных возможностей за счет обеспечения входного контроля множимого и множителя и повышения надежности устройства в целом. Устройство состоит из умножителя нормализованных двоичных чисел и схем аппаратного контроля. Введение регистров контрольных разрядов множимого , множителя и результата, а также группы умножителей по модулю 3 и двух дополнительных блоков сравнения позволяет осуществлять контроль выполнения операции умножителя и контроль передач операндов и результата. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4772383/24 (22) 29.12,89 (46) 15.06.92, Бюл. ¹ 22 (71) Институт точной механики и вычислительной техники им, С.А,Лебедева (72) Л.Г.Матясова и Л.Ф.Чайковский (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 807278, кл. G 06 F 7/52, 1981.

Авторское свидетельство СССР № 1361556, кл, G 06 F 11/08, 1986. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ С

КОНТРОЛЕМ (57) Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устИзобретение относится к вычислительной технике и предназначено для использования в быстродействующих цифровых арифметических устройствах для умножения нормализованных чисел.

Цель изобретения — повышение надежности и расширение функциональных возможностей за счет обеспечения входного контроля множимого и множителя.

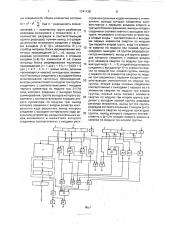

На фиг.1 представлена схема устройства для умножения входным контролем операндов и контролем операции умножения; на фиг.2 — конфигурация блока формирования частичных произведений, представляющего собой матрицу элементов И (совокупность выходов каждой матрицы образует частичное произведение); на фиг,3— поле всех частичных произведений, распо.. Ж 1741128 А1 ройств универсальных и специализирован- ных ЭВМ для умножения нормализованных чисел. Цель изобретения — расширение функциональных возможностей за счет обеспечения входного контроля множимого и множителя и повышения надежности устройства в целом. Устройство состоит из умножителя нормализованных двоичных чисел и схем аппаратного контроля, Введение регистров контрольных разрядов множимого, множителя и результата, а также группы умножителей по модулю 3 и двух дополнительных блоков сравнения позволяет осуществлять контроль выполнения операции умножителя и контроль передач операндов и результата. 3 ил. ложенных в соответствии с их весом (для алгоритма умножения со старших разрядов), а также разбиение сомножителей на секций, причем секция 1 содержит k разрядов, а секции с 2-й no i-ю состоят из разрядов каждая.

Устройство содержит регистры 1, 2 и 3 множимого, множителя и результата, при этом выходы регистров 1 и 2 являются входными шинами множимого и множителя, регистры 4, 5 и 6 контрольных разрядов по модулю 3 множителя, множимого и результата, блок 7 формирования частичных произведений, блок суммирования, состоящий из сумматора 8, образующего на выходе двухрядный код суммы частичных произведений, и сумматора 9 с приведением переносов, включающего дополнительные

1741128

А;, на Вз, и т,д. разряды, элементы 10.1 — 10.i свертки по модулю 3 множимого, элементы 11,1 — 11.1 свертки модулю 3 множителя; умножители

12.1 — 12.i по модулю 3, сумматор 13 по модулю 3 для получения ожидаемой свертки результата, сумматор 14 по модулю 3 результата и элементы 15 — 17 сравнения двухразрядных кодов.

Выходы регистров 1 и 2 множимого и множителя подключены к входам блока 7 формирования частичных произведений, выход которого соединен с входом блока суммирования, состоящего из сумматоров 8 и 9, Выход блока суммирования связан с входом регистра результата, выход которого является выходной шиной результата.

Выход блока суммирования, кроме того, соединен с входом сумматора 14 по модулю 3, а его выход соединен с первым входом блока 15 сравнения, второй вход которого подключен к выходу сумматора 13 по модулю 3.

Выход блока 15 сравнения является выходной шиной контроля результата, Выходы регистров 4 и 5 контрольных разрядов множимого и множителя соединены с первыми входами блоков 16 и 17 сравнения соответственно, вторые входы которых подключены к выходам элементов 10.1 и 11.1 свертки по модулю 3 соответственно. Выходы блоков 16 и 17 являются выходными шинами контроля множимого и множителя.

Выходы групп разрядов с 1-го по i-й регистра 1 множимого соединены с первыми входами элементов 10,1 — 10,i свертки по модулю 3 соответственно, а вторые входы элементов 10,1 — 10(i-1) соединены с выходами элементов 10.2 — 10.I Выходы элементов 10,1 — 10.i соединены с первыми входами умножителей 12.1 — 12.i по модулю

3. Первый вход элемента 11.1 свертки. по модулю 3 соединен с выходом первой группы разрядов регистра 2 множителя, входы элементов 11.2 — 11л соединены с выходами соответствующих групп разрядов регистра

2. Выходы элементов 11,2 — 11.i соединены с соответствующими входами элемента

11.1. Выходы элементов 11,1 — 11,i ñîåäèíåны со вторыми входами умножителей 12,1—

12.i, выход которых подключены к соответствующим входам сумматора 13 по модулю

3. Выход дополнительных разрядов блока суммирования подключен к (i+1)-му входу сумматора 13, Выход сумматора 14 по модулю 3 через регистр 6 контрольных разрядов результата соединен с выходной шиной контрольных разрядов результата.

Устройство предназначено для умножения двух и-разрядных нормализованных чисел без знака с расположением двоичной точки слева от старшего разряда. Произведение имеет ту же разрядность и, что и сомножители. Разряды результата, выходящие из разрядной сетки вправо, отбрасываются.

Множимое и множитель поступают на регистры 1 и 2 соответственно . Их контрольные коды, представляющие собой свертки по модулю 3 множимого и множителя и образованные в устройстве, посылающем сомножители в устройство для умножения, принимаются на регистры 4 и 5.

С выходов регистров 1 и 2 множимое и множитель подаются в блок образования частичных произведений на входы матрицы элементов И, которая образует частичные произведения, подключаемые далее в соответствии с их весом к входам блока суммирования. С выхода блока суммирования результат умножения передается на регистр 3 результата, при этом дополнительные разряды на регистр результата не поступают, а подаются на (i+1)-й вход сумматора 13 по модулю 3.

Матрица элементов И блока 7 формирования частичных произведений для получения полного произведения должна была бы содержать пхп элементов И. Известно, что для получения и-разрядного результата можно отбросить часть элементов И, которые образуют разряды частичных произведений с весом, меньшим веса разряда с номером m >n. Разряды от (и+1) до m являются дополнительным, обеспечивающими необходимую точность умножения. Их количество зависит от и.

На фиг,3 множимое обозначено через А, множитель — через B. Оба сомножителя разбиваются на i групп разрядов. Группы с 2-й по i-ю имеют одинаковую разрядность I, первая группа имеет разрядность k = 1+ m— и. Такое разбиение позволяет образовать в поле частичных произведений зигзагообразную линию, справа от которой расположена отбрасываемая часть этого поля (фиг,3). Все отбрасываемые разряды имеют вес, меньший, чем у разряда с номером m, т,е. условие сохранения точности результата соблюдается.

Отбрасываемая часть представляет собой совокупность (i-1) параллелограммов, обозначенных Р, Р,...Рн, Численное значение каждого параллелограмма — сумма кодов, заключенных внутри него — равно произведению групп разрядов сомножителей, образующих его стороны.

Например, Pr = А Bz, Рг рас..о произведению кода, составленного из Ai-> и

1741128

Численное значение всей отбрасываемой части Роч представляет собой сумму численных значений параллелограммов:

Ро„= Ai В2+ C(Ai-1, Ai) Вз+

+ С(А2, Аз,...Ai) Вь

P = А B - Ai В2- C(AI-1), Ai B3— C(A1, A2 Ai) Bi Рд

Следовательно, для ожидаемой свертки 20 результата OR (P) справедлива формула;

OR(P) = R(A) R(B) — В(А;) R(B2)- R(C(A; 1, Ai) К(Вз) — R(C(A1- А2„„А )) х х R(B;) — R(Pd, (2) 25 где R — функция свертки по модулю 3 (все действия выполняются также по модулю 3), Формула (2) является основной для по- 30 строения схем контроля операции умножения, Значения сверток R(A), R(A2)...R(C(A2, Аз,.ÄAi)) образуются на выходах элементов

10.1, 10,2,...10.i соответственно (фиг.1). Значения сверток R(B), R(B2),...R(Bi) образуются 35 на выходах элементов 11.1, 11.2,...,11Л. Значения пспарных произведений из формулы (2) образуются на выходах умножителей

1 2 . 1 — 1 2 .i, Каждый умножитель по модулю 3 состо- 40 ит из двух схем 2И-2ИПИ, реализующих булевы выражения: х1 = а1.Ь2+ а2 Ь1; х2 = а1 a2+ Ь1 Ь2

45 где х i, х2 — разряды результата умножения пс модулю 3, а1, а2 и b1, b2 — перемножаемые коды.

Эти выражения получены из рассмотре- 50 ния всех допустимых сочетаний а1, а2, b1 и

Ь2 и соответствующих им значений х1 и х2.

Значение ожидаемой свертки результата Ой(Р)формируется на выходе сумматора

13 по модулю 3. При этом коды с выходов 55 умножителей 12.2 — 12.i, а также код дополнительных разрядов с выхода сумматора 9, подаются на входы сумматора 13 с инверсией, что соответствует их вычитанию из где С вЂ” функция сцепления кодовых отрезков, перечисленных в скобках. 10

Выражение для результата P на выходе устройства с учетом (1), а также величины

Рд, определяемой отбрасыванием дополнительных разрядов с выхода блока суммирования, имеет вид; 15 кода с выхода умножителя 12.1, поступающего без инверсии.

На элементе 16 сравнения производится сравнение кодов с выходов элемента 10.1 и регистра 4, а на элементе 17 сравнения— кодов с выходов элемента 11.1 и регистра 5.

Сигналы с выходов элементов 16 и 17 являются сигналами входного контроля множимого и множителя.

На элементе 14 свертки по модулю 3 формируются контрольные разряды результата, которые сравниваются на элементе 15 с кодом с выхода сумматора 13, Сигнал с выхода элемента 15 является сигналом контроля умножения.

Таким образом, схемы контроля устройства выполняют две функции; контроль передач (входной контроль операндов и формирование контрольных разрядов результата) и контроль операции умножения.

Введение схем контроля в устройство для умножения позволяет фиксировать сбой в момент его возникновения, В результате экономится время, затрачиваемое при применении программных средств контроля вычислений. Кроме того, схемы контроля локализуют неисправность, облегчая ее поиск и устранение.

Формула изобретения

Устройство для умножения с контролем. содержащее регистры множителя, мнсжимого и результата, блок формирования частичных произведений, блок суммирования, две группы элементов свертки по модулю три, два сумматора по модулю три и первый блок сравнения, выход которого соединен с выходом контроля результата устройства, входы множимого и множителя которого соединены соответственно с входами регистров мнсжимогс и множителя, выходы блока формирования частичных произведений соединены с входами соответствующих весов блока суммирования, группа выходов которого соединена с входом регистра результата, выход которого соединен с выходом результата устройства, первый и второй входы первого блока сравнения соединены соответственно с выходами первого и второго сумматоров по модулю три, о т л и ч аю ц е е с я тем, что, с целью расширения функциональных возможностей за счет обеспечения входного контроля мнсжимсгс и множителя и повышения надежности устройства в целом, в него введены регистры контрольных разрядов множимогс, множителя и результата, второй и третий блоки сравнения и группа умножителей по модулю три, блок формирования частичных произведений выполнен в виде усеченной матри1741128 цы элементов И, общее количество которых ! — 1

N = n -1. $ (где n — раарядностн сомножителей; — количество групп разбиения разрядов множимого и множителя; К !— количество разрядов в соответствующей группе разрядов), причем выход J-го разряда регистра множимого соединен с первыми входами (n-l(i-1))-х элементов И J-го столбца матрицы блока формирования частичных произведений (J-1,...,n), выход j-ro разряда множителя соединен с вторыми входами (n-l(i-1)-х элементов И j-й строки матрицы блока формирования частичных произведений (i = 1 для J = 1-k; i = (J-k)/! + 2 для ) = k+1 - n; К вЂ” целые. числа, деление производится нацело), выходы всех элементов И матрицы соединены с выходами блока формирования частичных произведений, выходы умножителей по модулю три группы соединены с соответствующими i входами первого сумматора по модулю три, (i+1)-й вход которого соединен с выходом блока суммирования, группа выходов которого соединена с соответствующими входами второго сумматора по модулю три, выход которого соединен с входом регистра контрольного кода результата, выход которого соединен с выходом контрольного кода результата устройства, входы контрольных кодов множимого и множителя которого соединены соответственно с входами регистрое контрольных кодов множимого и множителя, выходы которых соединены соответственно с первыми входами второго и третьего блоков сравнения, выходы которых

5 соединены соответственно с выходами контроля множимого и множителя устройства, а вторые входы — соответственно с выходами первых элементов свертки по.модулю три первой и второй групп, вход i-го элемен10 та свертки по модулю три первой группы соединен выходом i-й группы разрядов регистра множимого, выход р-й группы разрядов которого соединен с первым входом р-ro элемента свертки по модулю три пер15 вой группы(р=1„,.1-1), второй вход которого соединен с выходом (р+1)-ro элемента свертки по модулю три первой группы, выходы с первого по !-й элементов свертки по модулю три соединены с первыми входами соот20 ветствующих умножителей по модулю три группы, вторые входы которых соединены соответственно с выходами с первого no i-й элементов свертки по модулю три второй группы, первый вход первого элемента

25 свертки по модулю три второй группы соединен с выходом первой группы разрядов регистра множителя, выход (р+1)-й группы разрядов которого соединен с входом (р+1)го элемента свертки по модулю три второй

30 группы, выход которого соединен соответственно с (р+1)-м входом первого элемента свертки по модулю три второй группы.

1741128

1741128 и л

Ъ

Составитель Л. Чайковский

Редактор Л. Пчолинская Техред М,Моргентал Корректор О Кравцова

Заказ 2085 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101