Операционный усилитель

Иллюстрации

Показать всеРеферат

Изобретение относится к операционным усилителям и предназначено для использования в аналоговых и аналого-цифровых системах на полевых транзисторах. Цель - повышение коэффициента подавления синфазного напряжения. Цель достигается за счет дополнения истоковых нагрузок первого и второго дифференциальных каскадов транзисторами,дополнительного введения цепи отрицательной обратной связи по синфазному напряжению и преобразователя дифференциального сигнала в однофазный , 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

s Н 03 F 3/45

ГОСУДАPСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4849829/09 (22) 10.07.90 (46) 15.06.92. Бюл. № 22 (71) Новосибирский электротехнический институт связи им, Н.Д.Псурцева (72) Д.Л. Шлемин (53) 621,375.024(088.8) (56) Авторское свидетельство СССР

¹ 1336201, кл. Н 03 F 3/45, 1986. (54) ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ (57) Изобретение относится к операционным усилителям и предназначено для исИзобретение относится к усилительным устройс гвам и предназначено для использования в усилителях различного назначения, которые являются элементами аналоговых и аналого-цифровых систем на КМОП транзисторах.

Цель изобретения — расширение области применения путем повышения коэффициента подавления синфазного напряжения.

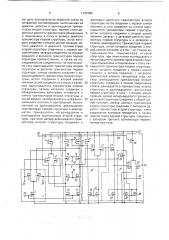

На чертеже приведена принципиальная схема OY.

OY содержит первый 1 и второй 2 входные дифференциальные каскады на транзисторах 3-8, выходную цепь входных дифференциальных каскадов 9 на транзисторах 10-17, ЦООССН 18 на транзисторах

19.-23, ПД-0 24 на транзисторах 25-30, выходной каскад 31 на транзисторах 32 и 33, инвертирующий вход 34, неинвертирующий вход 35, выход 36, вывод 37 первого источника напряжения смещения, вывод 38 второго источника напряжения смещения 38, вывод третьего источника напряжения вмещения, вывод 40, четвертого источника на!

Ы 1741255 А1 пользования в аналоговых и аналого-цифровых системах на полевых транзисторах.

Цель — повышение коэффициента подавления синфазного напряжения. Цель достигается за счет дополнения истоковых нагрузок первого и второго дифференциальных каскадов транзисторами, дополнительного введения цепи отрицательной обратной связи по синфазному напряжению и преобразователя дифференциального сигнала в однофазный. 1 ил. пряжения смещения, отрицательную шину

41 источника питания, положительную шину

42 источника питания, общую шину 43 источника питания, OY работает следующим образом.

На входы OY подается входное напряжение, имеющее дифференциальную и синфазную составляющие, Токи стоков транзисторов 4 и 5, 7 и 8 дифференциальных пар входных каскадов получают соответствующие приращения, которые суммируются на общей нагрузке каскадов, выполненной в виде выходной цепи первого и второго входных каскадов. На стоках транзисторов

12 и 13, являющихся дифференциальным выходом выходной цепи, появляется усиленное входное напряжение. При этом напряжение смещения нуля OY в широком диапазоне синфазных входных напряжений остается практически постоянным, поскольку основным источником напряжения смещения нуля OY является разброс параметров нагрузочных цепей дифференциальных пар, В предлагаемом устройстве нагрузочная цепь является общей для обоих

1741255

35

55 входных каскадов. Дальнейшее подавление синфазного напряжения осуществляется цепью отрицательной обратной связи по синфазному напряжению (ЦООССН). При синфазном повышении напряжения на выходах выходной цепи транзисторы 22 и 23

ЦООССН начинают закрываться, При этом ток стока транзистора 20 уменьшается. Следовательно, уменьшается ток стока транзистора 21, что вызвано взаимодействием транзисторов 19 и 20. Транзисторы 16, 17 и

21 образуют токовое зеркало, поэтому транзисторы 16 и 17 призакрываются, что приводит к компенсации синфазного увеличения выходного напряжения выходной цепи, Аналогичным образом осуществляется компенсация синфазного уменьшения выходного напряжения. Дифференциальный сигнал на выходе выходной цепи не оказывает воздействия на ЦООССН, что обусловлено симметрией транзисторов 22 и 23.

Преобразование дифференциального выхода выходной цепи входных каскадов в однофазный осуществляет преобразователь дифференциального сигнала в однофазный (ПД-O).

Преобразование осуществляется следующим образом.

Выходное напряжение одного плеча выходной цепи, а именно со стока транзистора

12, поступает на затвор транзистора 33 выходного каскада. Выходное напряжение другого плеча выходной цепи, противофазное первому, поступает на затвор транзистора 27. Пусть потенциал затвора транзистора 27 увеличивается, При этом транзистор 27 начинает закрываться, а потенциал стока этого транзистора уменьшается. При этом начинает открываться транзистор 29, что приводит к уменьшению тока стока транзистора 30 и к уменьшению напряжения затвор — исток для транзисторов 26 и 25, а также 32 выходного каскада, Следовательно, изменение потенциала стока транзистора 27 будет скомпенсировано, При этом затвор транзистора 32 выходного каскада получает приращение напряжения, противофазное приращению, напряжения затвор — исток транзистора 33 выходного каскада. Таким образом, на выходе OY появляется сигнал, симметричный относительно нулевого уровня, подаваемого на затвор транзистора 30.

Введение в, схему OY выходной цепи входных дифференциальных каскадов, ЦООССН и ПД-0 позволяет повысить коэффициент подавления синфазного напряжения.

Это позволяет повысить устойчивость OY к помехам, возникающим на шинах питания, а следовательно, делает возможным изготовление OY на одной подложке с цифровыми элементами.

Использование предлагаемого OY позволяет улучшить точностные показатели аналоговых элементов и, кроме того, делает возможным интеграцию на одном кристалле аналого-цифровых систем.

Формула изобретения

Операционный усилитель на полевых транзисторах, содержащий первый дифференциальный каскад с первым генератором тока, выполненные на первом, втором и третьем транзисторах первой структуры, причем затвор третьего транзистора первого генератора тока является выводом для подачи первого напряжения смещения, второй дифференциальный каскад с вторым генератором тока, выполненные на первом, втором и третьем транзисторах второй структуры, причем затвор третьего транзистора BTopolG генератора тока является выводом для подачи второго напряжения смещения, затворы первых и вторых транзисторов первого и второго дифференциальных каскадов попарно объединены и являются первым и вторым входами операционного усилителя соответственно, а цепи стоков транзисторов первого дифференциального каскада соединены со стоками четвертого и пятого транзисторов второй структуры соответственно, затворы которых объединены, истоки подключены к первой шине питания, цепи стоков транзисторов второго дифференциального каскада соединены со стоками четвертого и пятого транзисторов первой структуры соответственно. затворы которых объединены, истоки подключены к второй шине питания, выходной каскад, выполненный на последовательно соединенных по постоянному току шестом транзисторе второй структуры и шестом транзисторе первой структуры, стоки которых объединены и являются выходом операционного усилителя, отличающийся тем, что, с целью повышения коэффициента подавления синфазного напряжения, к стокам четвертого и пятого транзисторов первой структуры подключены истоки введенных седьмого и восьмого транзисторов первой структуры соответственна, затворы которых объединены и являются выводом для подачи третьего напряжения смещения, а к стокам четвертого и пятого транзисторов второй структуры подключены истоки введенных седьмого и восьмого транзисторов соответственно, затворы .которых объединены и являются выводом для подачи четвертого напряжения смещения, при этом стоки седьмых и восьмых транзисторов попарно объединены, а также введе1741255 ны цепь отрицательной обратной связи по синфазной составляющей, выполненная на девятом, десятом и одиннадцатом транзисторах второй структуры, причем стоки девятого и десятого транзисторов объединены 5 и подключены к стоку и затвору девятого транзистора первой структуры, исток которого соединен с второй шиной питания, истоки девятого и десятого транзисторов второй структуры соединены с первой ши- 10 ной питания, затворы соединены со стоками седьмого и восьмого транзисторов первой структуры соответственно, а также на последовательно соединенных по постоянному току одиннадцатом транзисторе второй 15 структуры и десятом транзисторе первой структуры, затвор которого соединен с затвором девятого транзистора первой структуры, исток соединен с второй шиной питания,астоксоединен со стоком и затво- 20 ром одиннадцатого транзистора второй структуры, затвор которого соединен с объединенными затворами четвертого и пятого транзисторов второй структуры, а также введен преобразователь дифферен- 25 циального сигнала в однофазный, выполненный на одиннадцатом, двенадцатом транзисторах первой структуры и двенадцатом, тринадцатом, четырнадцатом и пятнадцатом транзисторах второй струк- 30 туры, при этом затвор двенадцатого транзистора второй структуры соединен с затвором десятого транзистора второй структуры, исток соединен с первой шиной питания, а сток соединен со стоком одиннадцатого транзистора первой структуры, исток которого соединен с второй шиной питания, затвор — с затвором шестого транзистора первой структуры и с затвором и стоком двенадцатого транзистора первой структуры, исток которого соединен с второй шиной питания, а сток — со стоком че-. тырнадцатого транзистора второй структуры, при этом истоки тринадцатого и четырнадцатого транзисторов второй структуры объединены и подключены к стоку пятнадцатого транзистора второй структуры, исток которого соединен с первой шиной питания, а затвор соединен с затвором транзистора BTQpQ!o генератора тока, затвор тринадцатого транзистора второй структуры соединен с точкой соединения стоков двенадцатого транзистора второй структурь и одиннадцатого транзистора первой структуры, а сток — с второй шиной питания, затвор четырнадцатого транзистора второй структуры соединен с общей шиной питания, затвор шестого транзистора второй структуры соединен с затвором девято о транзистора второй структуры, точка соединения затворов четвертого и пятого транзисторов первой структуры соедине; а с затворам третьего транзистора первого генератора тока,