Цифровой приемник сигналов многочастотного кода

Иллюстрации

Показать всеРеферат

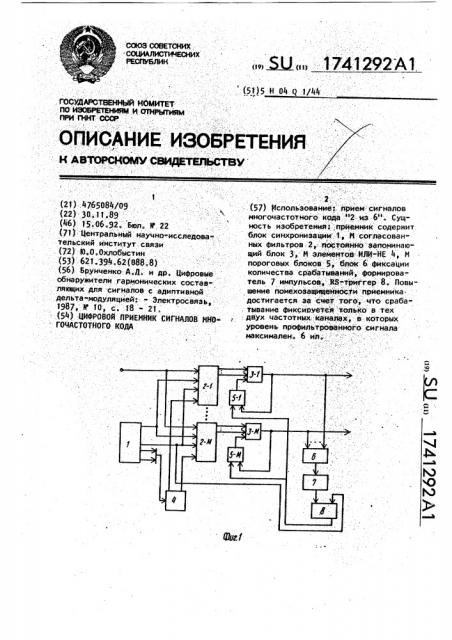

Использование: прием сигналов многочастотного кода 2 из 6й. Сущность изобретения:.приемник содержит блок синхронизации 1, М согласованных фильтров 2, постоянно запоминающий блок 3 И элементов ИЛИ-НЕ 4, M пороговых блоков 5 блок 6 фиксации количества срабатываний, формирователь 7 импульсов, RS-триггер 8. Повышение помехозащищенности приемникадостигается за счет того, что срабатывание фиксируется только в тех двух частотных каналах, в которых уровень профильтрованного сигнала максимален. 6 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 04 q 1/44

ОПИСАНИЕ И3ОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ HOMHTEY

ПО Иасап! И <ЩФйТИЯЫ (21) . 4765084/09

:(22) 30. 11:89 (46) 1S.06.92, Бел:. И, 2 2 (71)" Центральнйй научно-исследова-, тельский институт связи (721 -6..0. Охлобыстин

{53) 62Т-394:.б2(М8.8) (56). Брунченко, А.Д. и др. ЦиФровые обнаружители. гарионических составляющих для "сигналов с адиптивной дельта-модуляцией - Электросвязь, 1967,. И 10, с. 1 8 - 2 l.

- (54) ЦИФРОВОЙ ПРИЕМНИК СИГНАЛОВ МНОГОЧАСТОТНОГО КОДА < „1741292А1

: 2.

- (57) использование::,. прием .сигналов иногочастот-ного ко:"2 мз 6".. Сущность изобретейия!; привиник содержит. блок сйнхронизации. . -1., И согласованнйх Фильтров 2,:.л< слоянио"-запоминаю-щий .блок 3, И элементое-:ИЛИ-НЕ 4, И пороговых блоков 5., блок 6 Фиксации количества срабатываййй,: фориирова-. тель 7 иипульсов:, .RS-: триггер 8..- Повы: шение йомехозащйщенно@ти приеиника достигается:за снят того; что сраба. тывание фиксируется:. только в тех двух частотных каналах,.в которых уровень профильтрованного сигналаиаксииален:. 6 ил.

3 1741292

Изобретение относится к технике,Цель изобретения - повышение по--. .цифровой обработки. сигналов и может мехозащищенности приемника. быть использовано в электросвязи, Поставленная цель достигается тем, например, для приема сигналов много.- что в устройство, содержащее блок частотного кода "2 из 6." (или "2 из синхронизации, тактовые выходы кото8"), преобразованных в цифровую фор- рого подключены к тактовым входам му с помощью дельта"модуляции с инер- согласованных фильтров, выходы котоционным компандированием или импульс- рых соединены с сигнальными входами но"кодовой модуляции. соответствующих пороговых блоков, Приемник сигналов многочастотного выходы которых являются выходами кода, преобразованных в цифровую фор" приемника, входом которого являются му с. помощью дельта."модуляции, может, информационные входы согласованных быть построен на базе поРОговь!х Уст фильтров,,к входам весовых коэффициенройств и набора корреляторов, каждый тов которйх подключены соответствующие

15 из которых содержит линию задержки : выходы поСтоянного запоминающего отводы которой через умножители coe" блока, адресные входы которого соедидинень! с входами сумматора. . нены с адресйыми выходами блока синх. Недостатком устройства, помимо - ронизации; введены .элементы ИЛИ-НЕ .и сложности: реализации,. связанной c HB рО последовательно соединенные блок личием большого .количества Умножите" фиксации количества срабатываний, лей является возможность ложных, к входам которого подключены выходы ° срабатываний, например, при наличИи пороговых блоков, формирователь имтретьей мешающей частоты .или w3< x пульсов и RS-триггер, инверсный выотношениях сигнал/шум в обРабатывае" 25 ход которого подключен к первым вхомом сигнале. - дам элементов ИЛИ-НЕ, вторые входы

3а прототип устройства пРинят пр " которых соединены с выходами соотемник дельта-модулированных сигналов ветствующих пороговых блоков, при который содержит постоянный запоми - этом соответствующий тактовый выход

-- и блок .блок синхронизации и блока синхрониэации подключен к второ30 набор согласованных Фильтровю каждыи . му установочному входу RS-триггера, .,из которых соде орых содержит два элемента . а выходы элементов ИЛИ-НЕ соединены

ИСКЛЮцдЮщЕЕ ИЛИ, два Реверсивных. счет" с запрещающими выходами соответст-. чика, два блока вычисления модУля вующих пороговых блоков. . сумматор и пороговый блок. :, Сущность изобретения сводится к .

Недостатком устройства также яв" - 35 тому, что в течение одного цикла ляется невысокая помехозащищенностью . обработки при приеме, например, сигнапример, при наличии в составе двух" налов многочастотного кода "2 из И" частотного сигнала третьей мешающей первыми по времени сработают порочастоты, а также при наличии « " говые блоки именно в тех двух часнале сильных шумов, уровнем соизмери тотных .каналах,. в которых уровень

46 мых с уровнем сигнала. В соответствии частотых составляющих окажется мак" с требованиями, предъявляемь ми к симальным, после чего на пороговые приемникам кода "2 иэ 6, о6а случая блоки остальных частотных каналов возможны. При использовании t1octoHHHb x может быть подан запрещающий сигнал, порогов срабатывания (что имеет место 45 препятствующий ложным =рабатываниям в описанных выше устройствах} и при на других частотах, кроме двух приРаботе с сигналами в широком A» M"" нятых. В начале следующего .цикла ческом диапазоне пороги выбираются обработки все запрещающие сигналы вблизи нижней границы Рабочего диа"а снимаются и процесс обработки повто" зона уровней и являются относитель"о ® ряется аналогично описанному выше.

1небольшими, а в таких случаях при На фиг.1 приведена блок-схема приеме сигналов с высоким уровнем (" цифрового приемника сигналов многоиспользовании небольших постоянных частотного кода; на фиг.2 - временпорогов) возрастает опасность ложных we диаграммы, поясняющие работу срабатываний. В частности, могут 6 Tb 55 приемника; на фиг.3 - блок-схема .л ошибочно приняты несколько частот. блока синхронизации; на фиг.4 - блоквместо двух переданных, что свиде" схема формирователя импульсов; на т льствует о низкой помехоэащищеннос фиг.,б - блок-схемы согласованных тельствует

Ти. фильтров для сигналов дельта моду

5 17 ляции с инерционным компандированием и импульсно-кодовой модуляций соответственно.

Цифровой приемник сигналов многочастотного, кода содержит блок 1 синх ронизации, тактовые выходы которого подключены к тактовым входам согласованных фильтров 2. Выходы согласованных фильтров 2 соединены с сигнальными входами соответствующих пороговых: блоков 3, выходи которьа яв". ляются выходами приемника. Входом приемника являются информационные входы согласованйых.фильтров, к входаи: весовых коэффициентов которых подключены соответствующие выходы постоянного запоминающего блока.4, адресные входы которого соединены с адресными- выходами блока синхрониза-. ции .Цифровой приемник сигналов многочастотного кода также содержит элементы ИЛИ-НЕ 5 и:последовательно соединенные блок 6 фиксации количества

:срабатываний, к входам которого под-. ключены выходы пороговых блоков .3,: формирователь 7 импульсов и RS-. òðèãгер 8, инверсный выход которого под.- ключен к первым входам элементов ИЛИ. НЕ 5, вторые входы которых соединены с выходами .соответствующих пороговых . блоков, При этом соответствующий тактовый выход блока 1 синхрониза.ции подключен к второму установочному . входу RS.-триггера 8,"а .выходы элементов ИЛИ-НЕ 5 соединены с запре- . .щающими выходами соответствующих . пороговых блоков 3.

-Блок синхронизации (Фиг.3) содержит тактовый генератор 9, дели-. тель.10 частоты, инверторы 11, 12, дифференцирующее звено 13, элемент 14 задержки.

Блок-схема формирователя 7 импульсов (Фиг.4) содержит элемент 15 задержки, инвертор 16 и элемент И 17.

Блок-схема согласованного фильтра для дельта" модулированных сигналов (Фиг.5).содержит элементы 18-1, 18-2,. 0-1-1. " 20-1-r. 20"2-1

20-2-г, ИСКЛ)ЧАЮЩЕЕ ИЛИ с инверсией, реверсивные счетчики 19-1, 19-2,и .сумматор 21.

Блок-схема согласованного фильтра для сигналов импульсно-кодовой моду- ляции.(фиг.6) содержит умножители

22"1, 22-2, сумматоры 23-1, 23-2, 26, элементы 24-1, 24-2 задержки и блоки 25-1, 25-2 вычисления модуля.

41292 S

Устройство работает следующим образом.

На вход устройства .подается цифровой сигнал х(nT)., являющийся результатом преобразования сигналов многочастотного кода "2 из И" в цифровую Форму., напрймер, с помощью дельта-модуляции с инерционным ком10 пандированием. На фиг.2а условно показан сигнальный импульс многочас" тотного кода. Моменты постуйления отдельных отсчетов сигнала x(nT) синх" ронни с тактовой частотой, выдавае мой ло первому тактовому выходу блока

i синхронизации.

Входная цифровая последовательность х(пТ) разбивается на интервалы длительностью Т (фиг.26), равные и перинам Т частоты дискретизации; один интервал Т образует один цикл обработки сигнала;: результат обработ-. ки формируется .на выходе устройства к концу каждого цикла.

Узкополосные согласовайные Фильтры 2-1 ". 2-И настроены на частоты, соответствующие И заданным. частотным составляющим многочастотного кода.

Значения весовых коэффициентов согла30 .сованных Фильтров считываются с соот-. ветствующих выходов:постоянного запоминающего блока 4 синхронно с моментами поступлейия отсчетов х(пТ) входного сигнала. Сигналы начальной установки (e начале каждого цикла

31 обработки длительностью Тц} и тактовая частота NT подаются на сог1 ласованные фильтры 2-1 - 2-M от соответствующих тактовых выходов блока 1 синхронизации.

40 При использовании в качестве АЦП дельта-модуляции с инерционным ком" падированием и,квантовании весовых коэффициентов на два уровня согласованные фильтры строятся в соответст4S вии с блок-схемой, приведенной на фиг.5.

Устройство может использоваться и для обработки сигналов импульснокодовой модуляции, при этом могут. 0 быть использованы согласованные фильтры по блок-схеме, приведенной на Фиг.б. В этом случае сигнал х(пТ) и весовые коэффициенты представляют" ся не однобитными, а многоразрядныМ ми кодовыми словами.

ПО кОрОтким импульсам 025 (Фи

26), Формируемым на втором тактовом выходе блока 1 синхронизации и сле дующим с периодом Тц - NT, осуществ7 . 1741292 8, ляется обнуление (сброс) согласован- мирователя 7 импульсов по переднему .ных фильтров 2-1 - 2-И. фронту выходного сигнала Ug блока, 6 На фиг.2в условно показан харак" фиксации числа срабатываний форми тер изменения в течение. цикла 71 вы- руется короткий положительный имходных сигналов согласованных фильт.- 5 пульс(0,у, фиг.2ж), устанавливающий

Ров 2"1> 2-. 2, 2-3,для случая,.когда . RS-триггер 8 в единичное состояние в обРабатываемом сигнале, помимо . (сигнал це,фиг.2з); на инверсном eblдвух полезных составляющих с частота", ходе RS-триггера 8 сигнал будет рами fq fg присутствует третья ме- вен нулю. формирователь 7 импульсов шающая частота f g. Уровни .частотных . может быть построен, например, как составляющих удовлетворяют в данном показано на фиг.4, где 15 - элемент случае условию Uy< bUg )Ug. Вели"и" . задержки (или интегрирующая цепочка) на Р порога срабатыванйя пороговых 16 - инвертор, 17 - элемент И. Очеблоков 3-1 - 3-3 отмечена на фиг..2в видно, что единичный сигнал появитВблизи-резонансных частот согласован- ся на выходах только тех.элементов. 15 ных.фильтров характер нарастания их ИЛИ-НЕ, вторые входы которых подвыходного сигнала близок к:линей"ому соединены к тем пороговым блокам 3, и случай, показанный пунктиРом на которые к моменту появления единичфиг.2в, ведущий к необнаружению о 2р ного сигнала на выходе RS-триггера лезной частотной составляющей Не- 8 (118., фиг.3з) находились в несра-.

Возможен. B моменты времени 4» y - ботавшем состоянии. В тех же кана» будут выполнены условия срабатывания лах, где пороговые блоки сработали. (превышение порога выходными сигнала (в рассмотренном примере это пороми ц согласованных Фильтров)- со .говые блоки 3-1 . 3-2 первого и второФ-1 -: ., «25 ответственно в первом и втором:частот го частотйых каналов), выходные .сиг» ных каналах.. Выходнь1е сигналы,;noporo". налы элементов ИЛИ-НЕ 5 будут равны вых. блоков 3-1, 3-2 показаны на - нулю, Выходные сигналы элементов фиг.2г,д (сигналы U » ., U .> сооТ,: ИЛИ-HE 5 воздействуют на входы запреветсгвенно). - : та срабатывания .соответствующих поЕсли бы в устройстве отсутствова" . роговых блоков .(запрет осуществляетла введеннщ защита от ложных сраба" ся подачей единичного сигнала). Если, .:тываний (как в прототипе), то в "о .. например, пороговые блоки 3 строят- . .мент 1 сработал бы пороговый блок ся на базе цифровых компараторов, 3-.3 и, поскольку результат Обрэбо . запрет можно осуществить подачей Едики фиксируется в конце цикла (напР" 35 ничного сигнала с элемента ИЛИ-НЕ 5

1 мер, стробированием выходных фигне" . 1 на место старшего разряда двоичного . лов йороговых блоков- вблизи момента. числа, задающего порог срабатывания времени .f.>), был бы зафиксирован. . P порогового блока 3. Например, если прием всех, трех частот (ложное сра максимально возможное значение.ре" батывание на частоте З) ° - 4© зультата F ôèëüòðàöèè равно Р

В предложенном устройстве выход" 1 " 1=2 — 1, то. можно использовать ..

we сигналы пороговых блоков 3-1 + (k + 1) -разрядный компаратор и сое"

3-.И поступают на вход блока 6 фикса- динить выход соответствующего эле-..: ции числа срабатываний, на. выходе мента ИЛИ-НЕ5 с входом (k + 1) -го которого появляется единичный сигнал разряда двоичного числа, определяю45 (Ug, фиг.2е) сразу же, как только. . щего порог P. Наличие формирователя число сработавших пороговых блоков 3 7 импульсов необходимо для того, станет равно двум, Блок 6 фиксации чтобы к моменту (t .) поступления сигможет быть реализован, например, на нала "Сброс" на соответствующий вход базе постоянного запоминающего уст- К Е4-триггера 8 (ет второго тактово. SO

". Ройства, адресные -входы которого сое- ro выхода блока 1 синхронизации) на динены с выходами пороговых блоков его входе В установки в единицу так3 и которое программируется так, что же не присутствовал единичный сир« единице записывается только в те нал, поскольку одновременная подача ячейки, адреса которых содержат толь- 55. активных уровней сигнала на входы ко две единицы (на любых позициях) RS-триггера не допускается. В сооти нули, например, при и6 этому усло« ветствии с приведенным описанием вию удовлетворяют адреса 001010 . очевидно, что в данном устройстве

110000, 100001 и т.д. С помощью фор- обеспечивается прием только двух

10

20 рых соединены с сигнальными входами соответствующих пороговых блоков, выходы которых являются выходами приемника, входом. которого являются

25 информационные входы согласованных циентов которых подключены соответствующие адресные выходы постоянного . запоминающего блока, адресные входы

ЗО которого соединейы с адресными выходами блока сикхройизации, о т л.ич а ю шийся тем, что, с целью повышения помехозащищенности приемника, введены элементы ИЛИ-HE u последовательно соединенные блок

-входам которого подключены выходы . пороговых блоков, формирователь им- пульсов и RS-триггер, инверсный вы" ход которого подключен к первым вхо" дам элементов ИЛИ-НЕ, вторые .входы которых соединены с выходами соответствующих пороговых блоков, при этом соответствуюЩий, тактовый. вйход блока синхронизации подключен к вто45 рому установочному входу RS-триггера, а выходы. элементов ИЛИ-НЕ соединены с запрещающими входами соответствую1, 9 - . 174 частотных составляющих, имеющих максимальный уровень, и устраняются ложные срабатывания на остальных частотах, то есть повышается помехоза" щищенность. устройства.

В заключение следует остановиться на способе построения блока 1.синхро-. низации, блок-схема .которо о приве,дена на фиг.3 и содержит тактовый генератор 9, Формирующий частоту Ьо с. периодом Т = Х„, равным периоду дискретизации обрабатываемого сигна« ла, инверторы 11 - 12, k"ðàçðÿäíûé (k =. (1од Н, где а - минимальное целое, большее а) делитель 10, дифференцирующее.звено 13 и элемент- 14 задержки. При N = 2. на адресные вхо с ды постоянного запоминающего блока 4 подаются выходные сигналы всех k разрядов делителя IO, при этом за один цикл NT обработки перебирается .

N значений адреса, и к. началу сле-: дующего цикла делитель 1.0 автоматически возвращается s исходное .нуле- :.вое состояние.. При N .ô 2 выход де лителя 10 нужно соединить с его входом установки нуля через дешифратор, фиксирующий появление числа N на выходе делителя 10. С помощью элемен. та 14 .задержки формируется сигнал :

V, (фйг;2б), слегка задержанный относительно переднего фронта инверсии частоты йв/2" c k-ro разряда делите.-. ля 10 (имеется в виду, что делитель

10 последовательно принимает состояния 0« ° «001 О « ° «01 у 0«««10 ° ««0« ° «11 .....), благодаря чему в конце циклов, обработки (моменты tq, 1 на фиг.2г) при необходимости возможно стробирование выходных сигналов пороговых . блоков 5 непосредственно передним фронтом инверсии частоты 1 /2, напри"

k . мер,. с помощью 0-триггеров (на фиг. 1 не локазаны).

8 соответствии с приведенным выше описанием технико-экономическая эффективность предлагаемого устройства по сравнению с прототипом заключается

1292 10 в повышении защищенности от ложных срабатываний, в частности от срабатываний на и частотах при и ф 2.

Положительный эффект- достигается тем, что срабатывание фиксируется только в тех двух частотных каналах, в которых уровень профильтрованного сигнала максимален, при этом в каждом цикле обработки формируется специальный сигнал, запрещающий срабатывание во всех остальных частотных ка налах.

Формула изобретения

Цифровой приемник сигналов много-. частотного кода, содержащий блок синхронизации, тактовые выходы которого подключены к тактовым входам согласованных фильтров, выходы котофильтров, к входам .весовых коэффификсации количества срабатываний,.к щих пороговых блоков.

1.74 2 92

X(p7)

"n

Дб

Из< За

У 6

8 д и>

Фиг.2 к щакл об ю

Аостам сомасоРа,клык йгишооФ с2суаесмьлч лоуам да дюзЮю 2о улов оюирего сЪка.3 Ри 2. Л, 1741292 х(т

Рл/юаВ

&рка б ржам аюжеслФа срсб ыЬоиоо пмклюй|е

/ха 6/

nm люле ноы g4nом

Фаюа вй

&ока 3 ат 8mpoo2o ма ьпьбоа

Йгкьаа лько/

em neakzo еаклобою

6srxop Блока Z

om паиФОмннОРО

&ока ламялв ус ФОРО 2ОАяф

Ижмаш Г